Если вам нужно собрать компьютер или улучшить старый, то вам придется столкнуться с оперативной памятью и ее техническими характеристиками. Одна из главных — тактовая частота, которая выражается в МГц (Мегагерц). В общем и целом это и есть выражение скорости работы оперативной памяти, но, как обычно, присутствуют определенные нюансы. Сделает ли более быстрая память более стабильным показатель частоты кадров в играх? Пригодится ли более быстрая память для работы? Что обозначают другие характеристики? Попробуем разобраться.

- Что такое оперативная память (RAM) и как она работает?

- Тактовая частота и тайминги

- Можно ли одновременно использовать модули RAM с разными характеристиками?

- Пропускная способность

- Насколько важна тактовая частота и скорость RAM в целом?

- Современная оперативная память (RAM FAQ 1.01)

- SDRAM: Определение

- Микросхемы SDRAM: Физическая организация и принцип работы

- Микросхемы SDRAM: Логическая организация

- Модули SDRAM: Организация

- Модули памяти: Микросхема SPD

- Тайминги памяти

- Схема доступа к данным микросхемы SDRAM

- Соотношения между таймингами

- 📽️ Видео

Видео:03. Основы устройства компьютера. Память и шина. [Универсальный программист]Скачать

![03. Основы устройства компьютера. Память и шина. [Универсальный программист]](https://i.ytimg.com/vi/mjiJutISb6U/0.jpg)

Что такое оперативная память (RAM) и как она работает?

RAM (Random Access Memory, память с произвольной выборкой — информация записывается и считывается в любом порядке) — это временное и очень быстрое хранилище данных, которые обрабатываются центральным процессором компьютера (CPU). Запуск любой программы приводит к ее загрузке в оперативную память, благодаря чему доступ процессора к ней обеспечивается на порядки быстрее.

Каждый чип RAM состоит из миллионов микроскопических транзисторов и конденсаторов. Каждая пара «транзистор-конденсатор» представляет собой ячейку, и именно в этих ячейках хранится информация.

Эти ячейки могут хранить и выпускать электрический заряд — так информация записывается, считывается и стирается. Процесс записи и чтения происходит гораздо быстрее, чем в случае с традиционными жесткими дисками и даже SSD-накопителями.

При этом RAM энергозависима — при отключении питания все данные в ячейках пропадают. Именно поэтому хранить приложения и игры в памяти постоянно не получится (разве что ваш ПК никогда не выключается, а рядом стоит емкий ИБП).

Видео:Частота процессора, множитель и системная шинаСкачать

Тактовая частота и тайминги

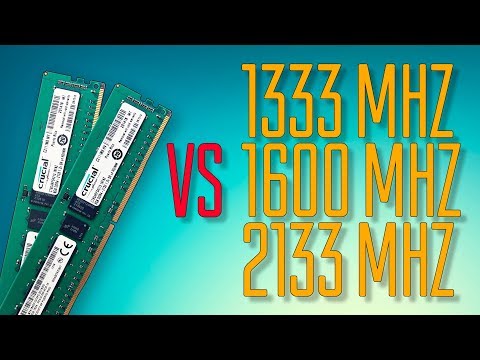

Скорость работы оперативной памяти — штука непростая. Нельзя просто взять тактовую частоту в МГц и использовать ее для сравнения. Для выяснения реальной скорости нужно знать и частоту, и скорость отклика — тайминг.

Тактовая частота выражается в циклах (один Герц — один цикл). Каждая запись и каждое считывание данных — это один цикл. К примеру, RAM с частотой 3200 МГц выполняет 3200 млн циклов в секунду. Чем больше циклов, тем больше информации за единицу времени может «принять» и «отдать» память.

CAS-тайминги (Column Access Strobe) определяет задержку (в циклах), которая проходит между получением памятью конкретной команды и ее исполнением. Они записываются в формате вроде 15-17-17-35.

Таким образом, оперативная память с высокой тактовой частотой и высокими CAS-таймингами может быть не намного лучше более дешевой памяти с более низкой частотой и более низкой задержкой.

Чтобы выяснить реальную скорость работы RAM, нужно поделить ее тактовую частоту — скажем, 3200 МГц — на первое число в строчке CAS-таймингов — скажем, 14. В шанем примере это будет 228.58 млн — именно столько инструкций сможет в секунду исполнить такая память.

Опять-таки для примера возьмем менее быструю RAM с тактовой частотой 2133 МГц и CAS-задержкой 6. Ее реальная скорость — 355.5 млн циклов в секунду. На 55% лучше!

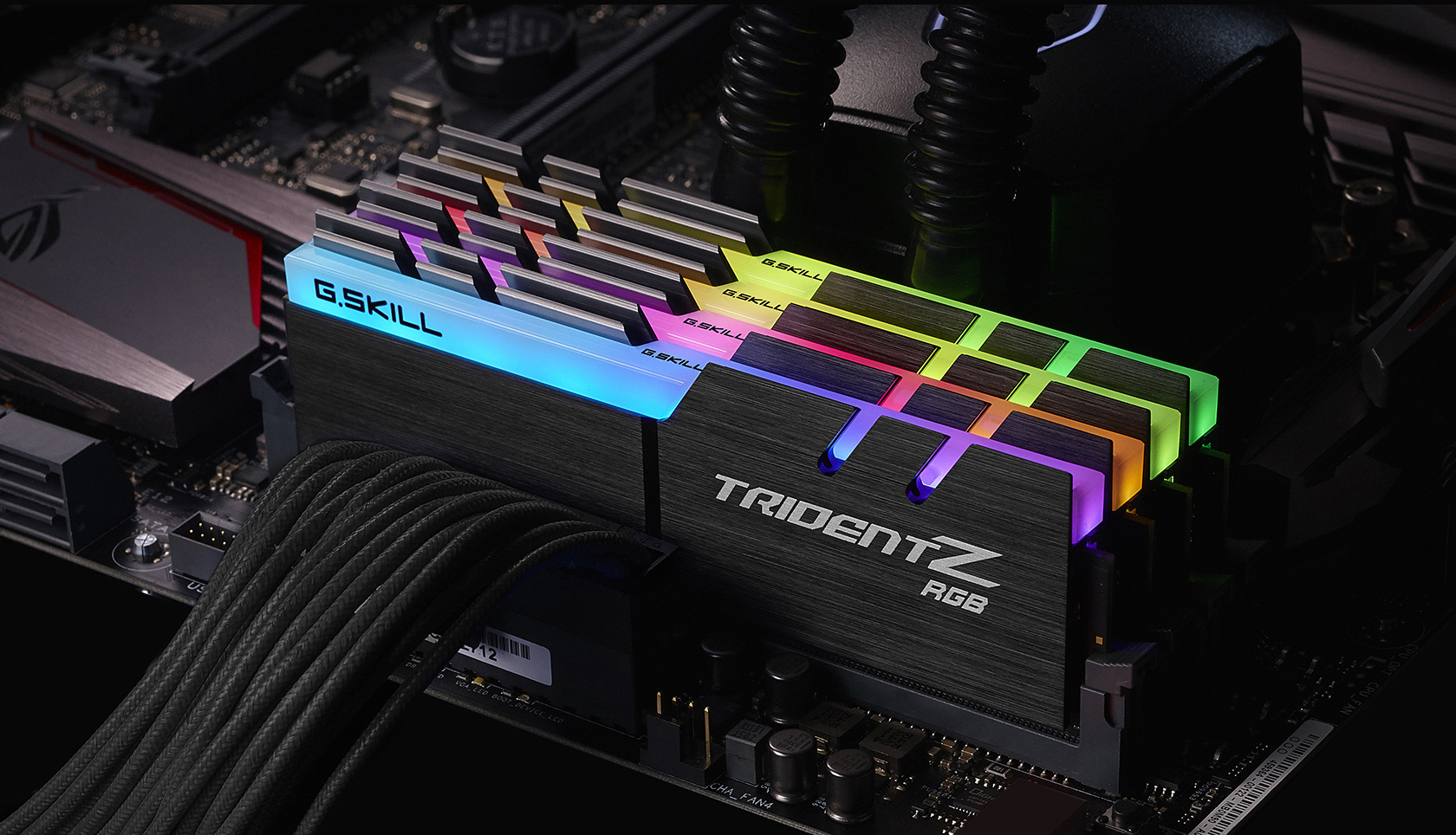

Стоит упомянуть и разгон. Максимальная стандартная тактовая частота оперативной памяти типа DDR4 — 2133 МГц. Если в характеристиках указана более высокая частота — это означает, что производитель гарантирует беспроблемный разгон до указанной скорости. Обычно это означает использование XMP-профилей в BIOS материнской платы, которые автоматически выставляют все нужные параметры так, как было задумано инженерами.

Видео:Какая частота памяти нужна играм... или тайминги?Скачать

Можно ли одновременно использовать модули RAM с разными характеристиками?

Это достаточно комплексный вопрос с комплексным ответом. Впрочем, на него можно дать и краткий ответ — «да».

В теории каждая планка оперативной памяти совместима с другими, которые имеют отличающиеся тайминги и тактовую частоту. Но! Чем больше разница, тем больше работы по синхронизации придется выполнять материнской плате.

К примеру, две планки памяти с одной тактовой частотой (скажем, 2133 МГц) и немного разными CAS-таймингами (которые отличаютя на 1-2) почти наверняка смогут работать вместе без проблем. При этом скорость работы обеих будет автоматически выбрана наименьшая.

Чем больше разница, тем нестабильнее будут две планки работать одновременно (если их больше двух — ситуация ухудшается на порядок, так что больше двух разных планок использовать точно не советуем). В этом случае может понадобиться ручной контроль тактовой частоты и таймингов в настройках BIOS.

Чуть менее краткий ответ на заданный вопрос? «Без убедительной причины лучше не пробовать — можно заработать лишнюю головную боль».

Видео:Как посмотреть частоту на которой работает оперативная память в AIDA64! 2024Скачать

Пропускная способность

Объем, тактовая частота и тайминги — это еще далеко не все. Пропускная способность заслуживает собственной статьи, но если говорить о ней в нескольких абзацаз, то стоит сказать о том, что она влияет на максимальную скорость передачи данных — на каждую планку памяти и с нее.

Объяснить это можно на примере широкой многополосной дороги — чем больше у нее полос, тем больше машин сможет проехать по ней одновременно. Тактовая частота и тайминги при этом — ограничение максимальной скорости движения авто. Ну а сама память — громадный гараж, в который эти машины едут.

Таким образом, двухканальная память работает куда быстрее одноканальной, а четырехканальная (ее поддержка зависит от процессора и материнской платы) — еще быстрее.

Кстати, об объеме. Кратко: оптимальный минимум для любого домашнего ПК в 2019 году — 8 ГБ RAM, но лучше всего начать с 16 ГБ. Больше оперативной памяти нужно устаналивать в компьютеры, которые будут использоваться для стриминга или же для работы в серьезных профессиональных пакетах ПО (например, архитектурных или для редактирования изображений и видео).

Видео:Частота процессора или частота системной шины?Скачать

Насколько важна тактовая частота и скорость RAM в целом?

Что ж, мы выяснили значение нескольких важных характеристик оперативной памяти и их влияние на общую скорость работы системы. Но насколько заметно это влияния в играх и профессиональном ПО? Стоит ли тратить больше денег на высокоскоростную память?

Многочисленные тесты, результаты которых легко можно найти в сети (пример), говорят о том, что перед нами тоже достаточно сложная ситуация.

Многие «синтетические» игровые тесты не показывают особой разницы даже между памятью с частотой 2133 МГц и 3200 МГц — различие в итоговом показателе частоты кадров можно даже списать на погрешность оценки. Такая же картина складывается в играх вроде Assassin’s Creed Odyssey и им подобных. Все потому, что эти тесты гораздо больше полагаются на скорость работы процессора и видеокарты, чем на скорость RAM.

А вот в играх, которые работают на высоких показателях частоты кадров в секунду (скажем, больше 90), ситуация иная. Разница в той же Overwatch может составлять несколько десятков fps — если вы используете монитор с высокой частотой развертки (120, 144 или 240 Гц — в общем, больше стандартных 60), то разницу заметить будет просто.

Таким образом, на высокоскоростную память стоит обращать внимание тем любителям видеоигр, которые играют в соревновательные дисциплины вроде Counter-Strike: Global Offensive, DotA 2, League of Legends, Overwatch и прочие. Это те игры, где исход матча может быть решен разницей в несколько кадров в секунду. Остальным же лучше потратить деньги на память большего объема или более мощную видеокарту.

Также на высокоскоростную память стоит обратить внимание тем, кто много работает в ПО для 3D-моделирования, архитектурном ПО и прочем ПО, которое постоянно выполняет сложные вычисления. И, понятное дело, если вы собираетесь зарабатывать стримингом видеоигр, быстрые планки RAM очень пригодятся — одновременно с игрой будет работать несколько других программ, которым тоже понадобится доступ к оперативной памяти.

Видео:Шина компьютера, оперативная память, процессор и мостыСкачать

Современная оперативная память (RAM FAQ 1.01)

Мы продолжаем публикацию цикла «руководств пользователя», посвященных теоретическому и практическому рассмотрению различных компонентов современного ПК, начало которому положил материал «Современные десктопные процессоры архитектуры x86: общие принципы работы (x86 CPU FAQ 1.0)». В настоящем руководстве мы рассмотрим основные современные виды оперативной памяти, применяемой в десктопных системах (оперативную память, применяемую в серверах и ноутбуках, оставим за его рамками). Под ними будем подразумевать память класса SDRAM SDR (Single Data Rate память с одинарной скоростью передачи данных), DDR (Double Data Rate память с удвоенной скоростью передачи данных) и DDR2 (память DDR второго поколения). Возможно, SDRAM «как таковая» (в ее первоначальном варианте SDR SDRAM) на сегодня уже не является столь актуальным видом памяти, тем не менее, все три перечисленных вида принадлежат одному и тому же классу и базируются примерно на одних и тех же принципах функционирования, которые мы и рассмотрим прямо сейчас.Содержание

- Часть 1. Теоретические основы современной оперативной памяти

- SDRAM: Определение

- Микросхемы SDRAM: Физическая организация и принцип работы

- Микросхемы SDRAM: Логическая организация

- Модули SDRAM: Организация

- Модули памяти: Микросхема SPD

- Тайминги памяти

- Схема доступа к данным микросхемы SDRAM

- Соотношения между таймингами

- Схемы таймингов

- Задержки командного интерфейса

Часть 1. Теоретические основы современной оперативной памяти

SDRAM: Определение

Аббревиатура SDRAM расшифровывается как Synchronous Dynamic Random Access Memory синхронная динамическая память с произвольным доступом. Остановимся подробнее на каждом из этих определений. Под «синхронностью» обычно понимается строгая привязка управляющих сигналов и временных диаграмм функционирования памяти к частоте системной шины. Вообще говоря, в настоящее время изначальный смысл понятия синхронности становится несколько условным. Во-первых, частота шины памяти может отличаться от частоты системной шины (в качестве примера можно привести уже сравнительно давно существующий «асинхронный» режим работы памяти DDR SDRAM на платформах AMD K7 с чипсетами VIA KT333/400, в которых частоты системной шины процессора и шины памяти могут соотноситься как 133/166 или 166/200 МГц). Во-вторых, ныне существуют системы, в которых само понятие «системной шины» становится условным речь идет о платформах класса AMD Athlon 64 с интегрированным в процессор контроллером памяти. Частота «системной шины» (под которой в данном случае понимается не шина HyperTransport для обмена данными с периферией, а непосредственно «шина» тактового генератора) в этих платформах является лишь опорной частотой, которую процессор умножает на заданный коэффициент для получения собственной частоты. При этом контроллер памяти всегда функционирует на той же частоте, что и сам процессор, а частота шины памяти задается целым делителем, который может не совпадать с первоначальным коэффициентом умножения частоты «системной шины». Так, например, режиму DDR-333 на процессоре AMD Athlon 64 3200+ будут соответствовать множитель частоты «системной шины» 10 (частота процессора и контроллера памяти 2000 МГц) и делитель частоты памяти 12 (частота шины памяти 166.7 МГц). Таким образом, под «синхронной» операцией SDRAM в настоящее время следует понимать строгую привязку временных интервалов отправки команд и данных по соответствующим интерфейсам устройства памяти к частоте шины памяти (проще говоря, все операции в ОЗУ совершаются строго по фронту/срезу синхросигнала интерфейса памяти). Так, отправка команд и чтение/запись данных может осуществляться на каждом такте шины памяти (по положительному перепаду «фронту» синхросигнала; в случае памяти DDR/DDR2 передача данных происходит как по «фронту», так и по отрицательному перепаду «срезу» синхросигнала), но не по произвольным временным интервалам (как это осуществлялось в асинхронной DRAM).

Читайте также: Плата компьютера для can шины

Понятие «динамической» памяти, DRAM, относится ко всем типам оперативной памяти, начиная с самой древней, «обычной» асинхронной динамической памяти и заканчивая современной DDR2. Этот термин вводится в противоположность понятия «статической» памяти (SRAM) и означает, что содержимое каждой ячейки памяти периодически необходимо обновлять (ввиду особенности ее конструкции, продиктованной экономическими соображениями). В то же время, статическая память, характеризующаяся более сложной и более дорогой конструкцией ячейки и применяемая в качестве кэш-памяти в процессорах (а ранее и на материнских платах), свободна от циклов регенерации, т.к. в ее основе лежит не емкость (динамическая составляющая), а триггер (статическая составляющая).

Наконец, стоит также упомянуть о «памяти с произвольным доступом» Random Access Memory, RAM. Традиционно, это понятие противопоставляется устройствам «памяти только на чтение» Read-Only Memory, ROM. Тем не менее, противопоставление это не совсем верно, т.к. из него можно сделать вывод, что память типа ROM не является памятью с произвольным доступом. Это неверно, потому как доступ к устройствам ROM может осуществляться в произвольном, а не строго последовательном порядке. И на самом деле, наименование «RAM» изначально противопоставлялось ранним типам памяти, в которых операции чтения/записи могли осуществляться только в последовательном порядке. В связи с этим, более правильно назначение и принцип работы оперативной памяти отражает аббревиатура «RWM» (Read-Write Memory), которая, тем не менее, встречается намного реже. Заметим, что русскоязычным сокращениям RAM и ROM ОЗУ (оперативное запоминающее устройство) и ПЗУ (постоянное запоминающее устройство), соответственно, подобная путаница не присуща.

Микросхемы SDRAM: Физическая организация и принцип работы

Общий принцип организации и функционирования микросхем динамической памяти (DRAM) практически един для всех ее типов как первоначальной асинхронной, так и современной синхронной. Исключение составляют разве что экзотические варианты, тем не менее, существовавшие еще до появления SDRAM, вроде Direct Rambus DRAM (DRDRAM). Массив памяти DRAM можно рассматривать как матрицу (двумерный массив) элементов (строго говоря, это понятие относится к логическому уровню организации микросхемы памяти, рассмотренному в следующем разделе, но его необходимо ввести здесь для наглядности), каждый из которых содержит одну или несколько физических ячеек (в зависимости от конфигурации микросхемы), способных вмещать элементарную единицу информации один бит данных. Ячейки представляют собой сочетание транзистора (ключа) и конденсатора (запоминающего элемента). Доступ к элементам матрицы осуществляется с помощью декодеров адреса строки и адреса столбца, которые управляются сигналами RAS# (сигнал выбора строки Row Access Strobe) и CAS# (сигнал выбора столбца Column Access Strobe).

Из соображений минимизации размера упаковки микросхемы, адреса строк и столбцов передаются по одним и тем же адресным линиям микросхемы иными словами, говорят о мультиплексировании адресов строк и столбцов (упомянутые выше отличия в общих принципах функционирования микросхем DRDRAM от «обычных» синхронных/асинхронных DRAM проявляются, в частности, здесь в этом типе микросхем памяти адреса строк и столбцов передаются по разным физическим интерфейсам). Так, например, 22-разрядный полный адрес ячейки может разделяться на два 11-разрядных адреса (строки и столбца), которые последовательно (через определенный интервал времени, см. раздел «Тайминги памяти») подаются на адресные линии микросхемы памяти. Одновременно со второй частью адреса (адреса столбца) по единому командно-адресному интерфейсу микросхемы SDRAM подается соответствующая команда (чтения или записи данных). Внутри микросхемы памяти адреса строки и столбца временно сохраняются в буферах (защелках) адреса строки и адреса столбца, соответственно.

Важно заметить, что с динамической матрицей памяти связан особый буфер статической природы, именуемый «усилителем уровня» (SenseAmp), размер которого равен размеру одной строки, необходимый для осуществления операций чтения и регенерации данных, содержащихся в ячейках памяти. Поскольку последние физически представляют собой конденсаторы, разряжающиеся при совершении каждой операции чтения, усилитель уровня обязан восстановить данные, хранящиеся в ячейке, после завершения цикла доступа (более подробно участие усилителя уровня в цикле чтения данных из микросхемы памяти рассмотрено ниже).

Кроме того, поскольку конденсаторы со временем теряют свой заряд (независимо от операций чтения), для предотвращения потери данных необходимо периодически обновлять содержимое ячеек. В современных типах памяти, которые поддерживают режимы автоматической регенерации (в «пробужденном» состоянии) и саморегенерации (в «спящем» состоянии), обычно это является задачей внутреннего контроллера регенерации, расположенного непосредственно в микросхеме памяти.

Схема обращения к ячейке памяти в самом общем случае может быть представлена следующим образом:

1. На адресные линии микросхемы памяти подается адрес строки. Наряду с этим подается сигнал RAS#, который помещает адрес в буфер (защелку) адреса строки.

2. После стабилизации сигнала RAS#, декодер адреса строки выбирает нужную строку, и ее содержимое перемещается в усилитель уровня (при этом логическое состояние строки массива инвертируется).

3. На адресные линии микросхемы памяти подается адрес столбца вместе с подачей сигнала CAS#, помещающего адрес в буфер (защелку) адреса столбца.

4. Поскольку сигнал CAS# также служит сигналом вывода данных, по мере его стабилизации усилитель уровня отправляет выбранные (соответствующие адресу столбца) данные в буфер вывода.

5. Сигналы CAS# и RAS# последовательно дезактивируются, что позволяет возобновить цикл доступа (по прошествии промежутка времени, в течение которого данные из усилителя уровня возвращаются обратно в массив ячеек строки, восстанавливая его прежнее логическое состояние).

Так выглядела реальная схема доступа к ячейке DRAM в самом первоначальном ее варианте, реализованном еще до появления первых реально используемых микросхем/модулей асинхронной памяти типа FPM (Fast Page Mode) DRAM. Тем не менее, нетрудно заметить, что эта схема является достаточно неоптимальной. Действительно, если нам требуется считать содержимое не одной, а сразу нескольких подряд расположенных ячеек, отличающихся только адресом столбца, но не адресом строки, то нет необходимости каждый раз подавать сигнал RAS# с одним и тем же адресом строки (т.е. выполнять шаги 1-2). Вместо этого, достаточно удерживать сигнал RAS# активным на протяжении промежутка времени, соответствующего, например, четырем последовательным циклам чтения (шаги 3-4, с последующей дезактивацией CAS#), после чего дезактивировать сигнал RAS#. Именно такая схема применялась в асинхронной памяти типа FPM DRAM и более поздней EDO (Enhanced Data Output) DRAM. Последняя отличалась опережающей подачей адреса следующего столбца, что позволяло достичь меньших задержек при операциях чтения.

В современных микросхемах SDRAM схема обращения к ячейкам памяти выглядит аналогично. Далее, в связи с обсуждением задержек при доступе в память (таймингов памяти), мы рассмотрим ее более подробно.

Микросхемы SDRAM: Логическая организация

А пока перейдем к рассмотрению организации микросхем памяти SDRAM на логическом уровне. Как уже было сказано выше, микросхема DRAM, фактически, представляет собой двумерный массив (матрицу) элементов, состоящих из одного или нескольких элементарных физических ячеек. Очевидно, что главной характеристикой этого массива является его емкость, выражаемая в количестве бит информации, которую он способен вместить. Часто можно встретить понятия «256-Мбит», «512-Мбит» микросхем памяти речь здесь идет именно об этом параметре. Однако составить эту емкость можно разными способами мы говорим сейчас не о количестве строк и столбцов, но о размерности, или «вместимости» индивидуального элемента. Последняя прямо связана с количеством линий данных, т.е. шириной внешней шины данных микросхемы памяти (но не обязательно с коэффициентом пропорциональности в единицу, что мы увидим ниже, при рассмотрении отличий памяти типа DDR и DDR2 SDRAM от «обычной» SDRAM). Ширина шины данных самых первых микросхем памяти составляла всего 1 бит, в настоящее же время наиболее часто встречаются 4-, 8- и 16- (реже 32-) битные микросхемы памяти. Таким образом, микросхему памяти емкостью 512 Мбит можно составить, например, из 128М (134 217 728) 4-битных элементов, 64М (67 108 864) 8-битных элементов или 32М (33 554 432) 16-битных элементов соответствующие конфигурации записываются как «128Mx4», «64Mx8» и «32Mx16». Первая из этих цифр именуется глубиной микросхемы памяти (безразмерная величина), вторая шириной (выраженная в битах).

Читайте также: Кумхо шины страна производства

Существенная отличительная особенность микросхем SDRAM от микросхем более ранних типов DRAM заключается в разбиении массива данных на несколько логических банков (как минимум 2, обычно 4). Не следует путать это понятие с понятием «физического банка» (называемого также «ранком» (rank) памяти), определенным для модуля, но не микросхемы памяти его мы рассмотрим далее. Сейчас лишь отметим, что внешняя шина данных каждого логического банка (в отличие от физического, который составляется из нескольких микросхем памяти для «заполнения» шины данных контроллера памяти) характеризуется той же разрядностью (шириной), что и разрядность (ширина) внешней шины данных микросхемы памяти в целом (x4, x8 или x16). Иными словами, логическое разделение массива микросхемы на банки осуществляется на уровне количества элементов в массиве, но не разрядности элементов. Таким образом, рассмотренные выше реальные примеры логической организации 512-Мбит микросхемы при ее «разбиении» на 4 банка могут быть записаны как 32Mx4x4 банка, 16Mx8x4 банка и 8Mx16x4 банка, соответственно. Тем не менее, намного чаще на маркировке микросхем памяти (либо ее расшифровке в технической документации) встречаются именно конфигурации «полной» емкости, без учета ее разделения на отдельные логические банки, тогда как подробное описание организации микросхемы (количество банков, строк и столбцов, ширину внешней шины данных банка) можно встретить лишь в подробной технической документации на данный вид микросхем SDRAM.

Разбиение массива памяти SDRAM на банки было введено, главным образом, из соображений производительности (точнее, минимизации системных задержек т.е. задержек поступления данных в систему). В самом простом и пока достаточном изложении, можно сказать, что после осуществления любой операции со строкой памяти, после дезактивации сигнала RAS#, требуется определенное время для осуществления ее «подзарядки». И преимущество «многобанковых» микросхем SDRAM заключается в том, что можно обращаться к строке одного банка, пока строка другого банка находится на «подзарядке». Можно расположить данные в памяти и организовать к ним доступ таким образом, что далее будут запрашиваться данные из второго банка, уже «подзаряженного» и готового к работе. В этот момент вполне естественно «подзаряжать» первый банк, и так далее. Такая схема доступа к памяти называется «доступом с чередованием банков» (Bank Interleave).

Модули SDRAM: Организация

Основные параметры логической организации микросхем памяти емкость, глубину и ширину, можно распространить и на модули памяти типа SDRAM. Понятие емкости (или объема) модуля очевидно это максимальный объем информации, который данный модуль способен в себя вместить. Теоретически он может выражаться и в битах, однако общепринятой «потребительской» характеристикой модуля памяти является его объем (емкость), выраженный в байтах точнее, учитывая современный уровень используемых объемов памяти в мега-, или даже гигабайтах.

Ширина модуля это разрядность его интерфейса шины данных, которая соответствует разрядности шины данных контроллера памяти и для всех современных типов контроллеров памяти SDRAM (SDR, DDR и DDR2) составляет 64 бита. Таким образом, все современные модули характеризуются шириной интерфейса шины данных «x64». Каким же образом достигается соответствие между 64-битная шириной шины данных контроллера памяти (64-битным интерфейсом модуля памяти), когда типичная ширина внешней шины данных микросхем памяти обычно составляет всего 4, 8 или 16 бит? Ответ очень прост интерфейс шины данных модуля составляется простым последовательным «слиянием» внешних шин данных индивидуальных микросхем модуля памяти. Такое «заполнение» шины данных контроллера памяти принято называть составлением физического банка памяти. Таким образом, для составления одного физического банка 64-разрядного модуля памяти SDRAM необходимо и достаточно наличие 16 микросхем x4, 8 микросхем x8 (это наиболее часто встречаемый вариант) или 4 микросхем x16.

Оставшийся параметр глубина модуля, являющийся характеристикой емкости (вместимости) модуля памяти, выраженной в количестве «слов» определенной ширины, вычисляется, как нетрудно догадаться, простым делением полного объема модуля (выраженного в битах) на его ширину (разрядность внешней шины данных, также выраженную в битах). Так, типичный 512-МБ модуль памяти SDR/DDR/DDR2 SDRAM имеет глубину, равную 512МБайт * 8 (бит/байт) / 64 бита = 64М. Соответственно, произведение ширины на глубину дает полную емкость модуля и определяет его организацию, или геометрию, которая в данном примере записывается в виде «64Мx64».

Возвращаясь к физическим банкам модуля памяти, заметим, что при использовании достаточно «широких» микросхем x8 или x16 ничего не мешает поместить и большее их количество, соответствующее не одному, а двум физическим банкам 16 микросхем x8 или 8 микросхем x16. Так различают однобанковые (или «одноранковые», single-rank) и двухбанковые («двухранковые», dual-rank) модули. Двухбанковые модули памяти наиболее часто представлены конфигурацией «16 микросхем x8», при этом один из физических банков (первые 8 микросхем) расположен с лицевой стороны модуля, а второй из них (оставшиеся 8 микросхем) с тыльной. Наличие более одного физического банка в модуле памяти нельзя считать определенным преимуществом, т.к. может потребовать увеличения задержек командного интерфейса, которые рассмотрены в соответствующем разделе.

Модули памяти: Микросхема SPD

Еще до появления первого типа синхронной динамической оперативной памяти SDR SDRAM стандартом JEDEC предусматривается, что на каждом модуле памяти должна присутствовать небольшая специализированная микросхема ПЗУ, именуемая микросхемой «последовательного обнаружения присутствия» (Serial Presence Detect, SPD). Эта микросхема содержит основную информацию о типе и конфигурации модуля, временных задержках (таймингах, см. следующий раздел), которых необходимо придерживаться при выполнении той или иной операции на уровне микросхем памяти, а также прочую информацию, включающую в себя код производителя модуля, его серийный номер, дату изготовления и т.п. Последняя ревизия стандарта SPD модулей памяти DDR2 также включает в себя данные о температурном режиме функционирования модулей, которая может использоваться, например, для поддержания оптимального температурного режима посредством управления синхронизацией (регулированием скважности импульсов синхросигнала) памяти (так называемый «троттлинг памяти», DRAM Throttle). Более подробную информацию о микросхеме SPD и о том, как выглядит ее содержимое можно получить в нашей статье «SPD схема последовательного детектирования», а также в серии наших исследований модулей оперативной памяти.

Тайминги памяти

Немаловажной категорией характеристик микросхем/модулей памяти являются «тайминги памяти» понятие, наверняка так или иначе знакомое каждому пользователю ПК. Понятие «таймингов» тесно связано с задержками, возникающими при любых операциях с содержимым ячеек памяти в связи со вполне конечной скоростью функционирования устройств SDRAM, как и любых других интегральных схем. Задержки, возникающие при доступе в память, также принято называть «латентностью» памяти (этот термин не совсем корректен, и пришел в обиход с буквальным переводом термина latency, означающего «задержка»).

В этом разделе мы рассмотрим, где именно возникают задержки при операциях с данными содержимым микросхем памяти, и как они связаны с важнейшими параметрами таймингов памяти. Поскольку в настоящем руководстве мы рассматриваем модули памяти класса SDRAM (SDR, DDR и DDR2), ниже мы рассмотрим конкретную схему доступа к данным, содержащимся в ячейках памяти микросхемы SDRAM. В этом разделе мы также рассмотрим несколько иную категорию таймингов, связанных не с доступом к данным, но с выбором номера физического банка для маршрутизации команд по командному интерфейсу модулей памяти класса SDRAM так называемые «задержки командного интерфейса».

Схема доступа к данным микросхемы SDRAM

1. Активизация строки

Перед осуществлением любой операции с данными, содержащимися в определенном банке микросхемы SDRAM (чтения команда READ, или записи команда WRITE), необходимо «активизировать» соответствующую строку в соответствующем банке. С этой целью, на микросхему подается команда активизации (ACTIVATE) вместе с номером банка (линии BA0-BA1 для 4-банковой микросхемы) и адресом строки (адресные линии A0-A12, реальное количество которых зависит от количества строк в банке, в рассматриваемом примере 512-Мбит микросхемы памяти SDRAM их число составляет 2 13 = 8192).

Активизированная строка остается открытой (доступной) для последующих операций доступа до поступления команды подзарядки банка (PRECHARGE), по сути, закрывающей данную строку. Минимальный период «активности» строки от момента ее активации до момента поступления команды подзарядки, определяется минимальным временем активности строки (Row Active Time, tRAS).

Повторная активизация какой-либо другой строки того же банка не может быть осуществлена до тех пор, пока предыдущая строка этого банка остается открытой (т.к. усилитель уровня, содержащий буфер данных размером в одну строку банка и описанный в разделе «Микросхемы SDRAM: Физическая организация и принцип работы», является общим для всех строк данного банка микросхемы SDRAM). Таким образом, минимальный промежуток времени между активизацией двух различных строк одного и того же банка определяется минимальным временем цикла строки (Row Cycle Time, tRC).

Читайте также: Таблица параметры всех шин

В то же время, после активизации определенной строки определенного банка микросхеме SDRAM ничего не мешает активизировать какую-либо другую строку другого банка (в этом и заключается рассмотренное выше преимущество «многобанковой» структуры микросхем SDRAM) на следующем такте шины памяти. Тем не менее, в реальных условиях производителями устройств SDRAM обычно здесь также умышленно вводится дополнительная задержка, именуемая «задержкой от активации строки до активации строки» (Row-to-Row Delay, tRRD). Причины введения этой задержки не связаны с функционированием микросхем памяти как таковых и являются чисто электрическими операция активизации строки потребляет весьма значительное количество электрического тока, в связи с чем частое их осуществление может приводить к нежелательным избыточным нагрузкам устройства по току.

2. Чтение/запись данных

Следующий временной параметр функционирования устройств памяти возникает в связи с тем, что активизация строки памяти сама по себе требует определенного времени. В связи с этим, последующие (после ACTIVATE) команды чтения (READ) или записи (WRITE) данных не могут быть поданы на следующем такте шины памяти, а лишь спустя определенный временной интервал, называемый «задержкой между подачей адреса строки и столбца» (RAS#-to-CAS# Delay, tRCD).

Итак, после прошествия интервала времени, равного tRCD, при чтении данных в микросхему памяти подается команда READ вместе с номером банка (предварительно активизированного командой ACTIVATE) и адресом столбца. Устройства памяти типа SDRAM ориентированы на чтение и запись данных в пакетном (Burst) режиме. Это означает, что подача всего одной команды READ (WRITE) приведет к считыванию из ячеек (записыванию в ячейки) не одного, а сразу нескольких подряд расположенных элементов, или «слов» данных (разрядность каждого из которых равна ширине внешней шины данных микросхемы например, 8 бит). Количество элементов данных, считываемых одной командой READ или записываемых одной командой WRITE, называется «длиной пакета» (Burst Length) и обычно составляет 2, 4 или 8 элементов (за исключением экзотического случая передачи целой строки (страницы) «Full-Page Burst», когда необходимо дополнительно использовать специальную команду BURST TERMINATE для прерывания сверхдлинной пакетной передачи данных). Заметим, что для микросхем памяти типа DDR и DDR2 параметр Burst Length не может принимать значение меньше 2 и 4 элементов, соответственно причину этого мы рассмотрим ниже, в связи с обсуждением различий в реализации устройств памяти SDR/DDR/DDR2 SDRAM.

Возвращаясь к чтению данных, заметим, что существует две разновидности команды чтения. Первая из них является «обычным» чтением (READ), вторая называется «чтением с автоматической подзарядкой» (Read with Auto-Precharge, «RD+AP»). Последняя отличается тем, что после завершения пакетной передачи данных по шине данных микросхемы автоматически будет подана команда подзарядки строки (PRECHARGE), тогда как в первом случае выбранная строка микросхемы памяти останется «открытой» для осуществления дальнейших операций.

После подачи команды READ, первая порция данных оказывается доступной не сразу, а с задержкой в несколько тактов шины памяти, в течение которой данные, считанные из усилителя уровня, синхронизируются и передаются на внешние выводы микросхемы. Задержка между подачей команды чтения и фактическим «появлением» данных на шине считается наиболее важной и именуется пресловутой «задержкой сигнала CAS#» (CAS# Latency, tCL). Последующие порции данных (в соответствии с длиной передаваемого пакета) оказываются доступными без каких-либо дополнительных задержек, на каждом последующем такте шины памяти (по 1 элементу за такт для устройств SDR, по 2 элемента в случае устройств DDR/DDR2).

Операции записи данных осуществляются аналогичным образом. Точно также существуют две разновидности команд записи простая запись данных (WRITE) и запись с последующей автоматической подзарядкой строки (Write with Auto-Precharge, «WR+AP»). Точно также при подаче команды WRITE/WR+AP на микросхему памяти подаются номер банка и адрес столбца. Наконец, точно также запись данных осуществляется «пакетным» образом. Отличия операции записи от операции чтения следующие. Во-первых, первую порцию данных, подлежащих записи, необходимо подать по шине данных одновременно с подачей по адресной шине команды WRITE/WR+AP, номера банка и адреса столбца, а последующие порции, количество которых определяется длиной пакета на каждом последующем такте шины памяти. Во-вторых, вместо «задержки сигнала CAS#» (tCL) важной здесь является иная характеристика, именуемая «периодом восстановления после записи» (Write Recovery Time, tWR). Эта величина определяет минимальный промежуток времени между приемом последней порции данных, подлежащих записи, и готовности строки памяти к ее закрытию с помощью команды PRECHARGE. Если вместо закрытия строки требуется последующее считывание данных из той же самой открытой строки, то приобретает важность другая задержка, именуемая «задержкой между операциями записи и чтения» (Write-to-Read Delay, tWTR).

3. Подзарядка строки

Цикл чтения/записи данных в строки памяти, который в общем случае можно обозначить «циклом доступа к строке памяти», завершается закрытием открытой строки банка с помощью команды подзарядки строки PRECHARGE (которая, как мы уже отмечали выше, может быть «автоматической», т.е. являться составной частью команд «RD+AP» или «WR+AP»). Последующий доступ к этому банку микросхемы становится возможным не сразу, а по прошествию интервала времени, называемого «временем подзарядки строки» (Row Precharge Time, tRP). За этот период времени осуществляется собственно операция «подзарядки», т.е. возвращения элементов данных, соответствующих всем столбцам данной строки с усилителя уровня обратно в ячейки строки памяти.

Соотношения между таймингами

В заключение этой части, посвященной задержкам при доступе к данным, рассмотрим основные соотношения между важнейшими параметрами таймингов на примере более простых операций чтения данных. Как мы рассмотрели выше, в самом простейшем и самом общем случае — для пакетного считывания заданного количества данных (2, 4 или 8 элементов) необходимо осуществить следующие операции:

1) активизировать строку в банке памяти с помощью команды ACTIVATE;

2) подать команду чтения данных READ;

3) считать данные, поступающие на внешнюю шину данных микросхемы;

4) закрыть строку с помощью команды подзарядки строки PRECHARGE (как вариант, это делается автоматически, если на втором шаге использовать команду «RD+AP»).

Временной промежуток между первой и второй операцией составляет «задержку между RAS# и CAS#» (tRCD), между второй и третьей — «задержку CAS#» (tCL). Промежуток времени между третьей и четвертой операциями зависит от длины передаваемого пакета. Строго говоря, в тактах шины памяти он равен длине передаваемого пакета (2, 4 или 8), поделенного на количество элементов данных, передаваемых по внешней шине за один ее такт — 1 для устройств типа SDR, 2 для устройств типа DDR. Условно назовем эту величину «tBL».

Важно заметить, что микросхемы SDRAM позволяют осуществлять третью и четвертую операции в некотором смысле «параллельно». Чтобы быть точным команду подзарядки строки PRECHARGE можно подавать за некоторое количество тактов x до наступления того момента, на котором происходит выдача последнего элемента данных запрашиваемого пакета, не опасаясь при этом возникновения ситуации «обрыва» передаваемого пакета (последняя возникнет, если команду PRECHARGE подать после команды READ с временным промежутком, меньшим x). Не вдаваясь в подробности, отметим, что этот промежуток времени составляет величину, равную величине задержки сигнала CAS# за вычетом единицы (x = tCL — 1).

Наконец, промежуток времени между четвертой операцией и последующим повтором первой операции цикла составляет «время подзарядки строки» (tRP).

В то же время, минимальному времени активности строки (от подачи команды ACTIVATE до подачи команды PRECHARGE, tRAS), по его определению, как раз отвечает промежуток времени между началом первой и началом четвертой операции. Отсюда вытекает первое важное соотношение между таймингами памяти:

где tRCD время выполнения первой операции, tCL второй, (tBL — (tCL — 1)) третьей, наконец, вычитание единицы производится вследствие того, что период tRAS не включает в себя такт, на котором осуществляется подача команды PRECHARGE. Сокращая это выражение, получаем:

Достаточно поразительный вывод, вытекающий из детального рассмотрения схемы доступа к данным, содержащимся в памяти типа SDRAM, заключается в том, что минимальное значение tRAS не зависит(!) от величины задержки CAS#, tCL. Зависимость первого от последнего достаточно распространенное заблуждение, довольно часто встречающееся в различных руководствах по оперативной памяти.

В качестве примера первого соотношения, рассмотрим типичную высокоскоростную память типа DDR с величинами задержек (tCL-tRCD-tRP) 2-2-2. При минимальной длине пакета BL = 2 (минимально возможной для DDR) необходимо затратить не менее 1 такта шины памяти для передачи пакета данных. Таким образом, в этом случае минимальное значение tRAS оказывается равным 3 (столь малое значение tRAS не позволяет выставить подавляющее большинство контроллеров памяти). Передача более длинных пакетов, состоящих из 4 элементов (BL = 4, tBL = 2), увеличивает это значение до 4 тактов, наконец, для передачи максимального по длине 8-элементного пакета (BL = 8, tBL = 4) требуемое минимальное значение tRAS составляет 6 тактов. Отсюда следует, что, поскольку большинство контроллеров памяти не позволяют указать значение tRAS n n-prefetch» всегда соответствует минимальная величина Burst Length, равная 2 n (n = 1 соответствует DDR; n = 2 DDR2; n = 3 грядущей DDR3).

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле

📽️ Видео

Как посмотреть частоту на которой работает оперативная память в AIDA64?Скачать

Как узнать частоту оперативной памяти компьютера или ноутбукаСкачать

Разгон частоты шины на китайском LGA2011 с помощью SetFSBСкачать

РАЗРУШИТЕЛЬ МИФОВ / ОПЕРАТИВНАЯ ПАМЯТЬ: ЧАСТОТА, ОБЪЕМ И ДВУХКАНАЛСкачать

🔧Проверь свою ОПЕРАТИВНУЮ ПАМЯТЬ, она работает не на все 100!Скачать

Разные планки оперативной памяти. Можно ли совмещать в одном ПК?Скачать

Как разогнать процессор и память? Гоним по шине и множителю.Скачать

Влияние частоты оперативной памяти на производительность в играх (часть 1)Скачать

ЧАСТОТА vs ТАЙМИНГИ - разрушаем мифы! Сколько нужно ОЗУ?Скачать

Виды видеопамяти и сколько её нужно? Какая нужна шина?Скачать

Влияние частоты оперативной памяти в играхСкачать

Нужно ли разгонять оперативную память на AMD ryzen ? ТЕСТ 1600,1866,2133,2666,2999,3200 MHzСкачать

Как настроить оперативную память если настройки авто кривыеСкачать

Отключаем поэтапно память у RTX 3090 и 3060 и измеряем разницу в производительности.Скачать