Магистральный параллельный интерфейс (МПИ) — стандарт, определяющий набор контактов и процедуры обмена по 16-разрядной шине с совмещением (мультиплексированием) адреса и данных.

Стандарт не определяет физической реализации интерфейса.

Принцип работы

Связь между двумя устройствами, подключенными к интерфейсу, осуществляется по принципу «управляющий»—»управляемый» (активный—пассивный). В каждый момент времени только одно устройство является активным. Активное (управляющее) устройство управляет циклами обращения, при необходимости обслуживает прерывания и осуществляет арбитраж.

Связь между устройствами является замкнутой и асинхронной. В ответ на обращение, пассивное устройство выставляет специальный сигнал, означающий что пассивное устройство присутствует и готово осуществлять дальнейший обмен. Если в течение 10 мкс ответ не получен, происходит прерывание специального вида. Таким образом, процесс обмена между устройствами не зависит от времени ответа (в пределах 10 мкс) или длины канала. Отсутствие или неисправность пассивного устройства может быть легко определена при отсутствии ответа.

Реализации

Электроника 60

Системный канал МикроЭВМ (магистральный интерфейс) «Электроника 60» по ОСТ 11.305.903-80 является упрощённым вариантом интерфейса типа «Общая шина» (ГОСТ 26765.51-86), к которому подключаются устройства микроЭВМ — центральные процессоры, запоминающие устройства, периферийные устройства. Физически представляет собой унифицированную магистраль по 33÷42 линиям которой осуществляется передача информации комплекса. Использование единого унифицированного интерфейса, имеющий общий для всех устройств комплекса алгоритм связи, позволяет унифицировать всю аппаратуру сопряжения.

По электрическим и функциональным характеристикам реализация МПИ в «Электроника-60» аналогична шине Q-Bus/LSI-Bus фирмы DEC. Механически незначительно отличается от Q-Bus: у Q-Bus расстояние между контактами 3.175 мм (что составляет 1/8 дюйма), а у МПИ — 3 мм. Также не совпадает нумерация контактов. Подобно Q-Bus, допускалось расширение адреса до 18 и 22 разрядов, что позволяло адресовать до 4 Мб памяти в максимальной конфигурации. Применялся разъем РППМ16х72. Из-за значительного содержания золота на контактах (около 4 грамм) практически все выпущенные изделия были утилизированы.

Компьютеры ДВК строились на базе микропроцессоров серии К1801 которые в качестве системной шины использовали набор сигналов, очень близкий к МПИ, что значительно упрощало конструкцию. Для связи модулей в ДВК применялся интерфейс МПИ, механически и электрически совместимый с реализацией в Электроника 60, но с увеличенным по высоте между платами расстоянием. Таким образом устройства «Электроника-60» могли напрямую применяться в ДВК.

СМ-1425

В СМ-1425 применяется шина функционально и электрически совпадающая с Q-Bus, но механически выполнена на разъемах ОПН-КГ. Процессор и модули ввода-вывода выполнены в виде блоков (БЭ — блоки элементов), которые имеют размер Eurocard 220×233,4 мм.

Компьютер БК-0010/БК-0011М имел системный интерфейс, подобный МПИ, но содержащий неполный набор сигналов и выведенный на разъем СНП58-64/94×9В-23-2-В (вилка). Шина не буферизирована и имеет малую нагрузочную способность.

В компьютере УКНЦ для подсоединения модулей расширения к Центральному и Периферийному процессорам (ЦП и ПП соответственно) также использовался интерфейс, логически и электрически подобный МПИ, но механически несовместимый с ДВК и БК. Для подключения модулей к ПП применялся разъем СНП15-48/80х10Р-19-2. Для подключения устройств к шине ЦП применялся краевой печатный 60-выводный соединитель, на который устанавливался переходник-удлинитель из двух разъемов ОНП-НГ-57-60/100,5х11,2-Р50.

Электроника С5

Компьютеры Электроника С5, начиная с Электроника С5-21, используют МПИ в качестве шины для связи с внешними устройствами. Модель Электроника С5-21 имеет два раздельных канала МПИ : один для связи с локальными устройствами, второй — для организации межмашинной связи и подключения разделяемых внешних устройств при организации многомашинных комплексов. Разъем — ГРПМШ-1-61.

Микросхемы

Электронная промышленность СССР выпускала несколько разновидностей микросхем с интерфейсом МПИ:

- Различные контроллеры на основе БМК КР1801ВП1, К1806ХМ1 и К1515ХМ1. Например, КР1801ВП1-035 — контроллер последовательного интерфейса.

- КР1801РЕ2 — масочное ПЗУ 4К×16 бит

- К1801РР1 — программируемое ПЗУ с электрическим стиранием

- К1809РЕ1 — масочное ПЗУ 4К×16 бит

- К588РЕ1 — масочное ПЗУ 4К×16 бит

- К573РФ3 — программируемое ПЗУ с УФ стиранием

- КР537РУ11 — ОЗУ емкостью 256×16 бит

- К1809РУ1 — ОЗУ емкостью 1К×16 бит

Читайте также: Борторасширитель для легковых шин размеры

Назначение контактов

Физическая реализация (тип разъема и нагрузочные характеристики) может отличаться в различных устройствах. Функционально сигналы делятся на сигналы передачи адреса/данных, сигналы арбитража приоритета и сигналы управления состоянием системы. Минимальный набор включает в себя только 16 сигналов передачи адреса/данных несколько сигналов управления.

| Международное | Старое | Новое | Назначение |

|---|---|---|---|

| Сигналы передачи адреса и данных | |||

| DAL15..DAL00 | АД15..АД00 | АД15..АД00 | Адрес-данные |

| SYNC | СИА | ОБМ | Синхронизация активного устройства |

| RPLY | СИП | ОТВ | Синхронизация (ответ) пассивного устройства |

| DIN | ВВОД | ДЧТ | Ввод (чтение) данных |

| DOUT | ВЫВОД | ДЗП | Вывод (запись) данных |

| WTBT | БАЙТ | ПЗП | Выбор (признак записи) байта |

| BS7 | ВН ВВ | ВУ | Выбор внешнего устройства (внутренний ввод) |

| REF | РГН | РГН | Регенерация памяти |

| Сигналы арбитража приоритета | |||

| IRQ | ТПР | ЗПР | Требование (запрос) прерывания |

| IAKN | ППР | ПРР | Предоставление (разрешение) прерываний |

| EVNT | ПРТ | ПВС | Прерывание по таймеру (по внешнему событию) |

| DMR | ТПД | ЗМ | Требование прямого доступа (запрос магитрали) |

| DMGO | ППД | РЗМ | Предоставление прямого доступа (разрешение захвата магистрали) |

| SACK | ПВ | ПЗ | Подтверждение выборки (запроса) системного канала (магистрали) |

| Сигналы управления состоянием системы | |||

| INIT | СБРОС | УСТ | Начальная установка |

| HALT | ОСТ | ОСТ | Останов |

| POK | ПИТН | АСП | Сетевое питание нормальное (Авария сетевого питания) |

| DCOK | ПОСТН | АИП | Постоянное напряжение нормальное (Авария источника питания) |

Полное название сигнала на шине включает в себя литеру B (Bus) для международного обозначения или литеру К (Канал) для русского. Последняя литера означала активный уровень, большинство сигналов передаются в инверсной TTL логике, поэтому в конце добавляется литера L (Low) для международного обозначения или литера Н (Низкий) для русского. Для сигналов в обычной ТТЛ логике обозначения соответственно H (High) и В (Высокий). Например, полное обозначение сигнала на шине: B HALT L или К ОСТ Н

Эмулятор БК-0010 на FPGA — часть 2

Первая часть

Если вы уже успели поработать с блочным дизайном в Vivado, то могли увидеть, что внешний вид многих стандартных IP изменяется в зависимости от настраиваемых параметров. Например, модуль AXI-GPIO может быть одноканальным или двухканальным в зависимости от параметра «Enable dual channel»:

Для проекта БК-0010 нам тоже будет удобно воспользоваться этой технологией и сегодня мы узнаем, как это сделать.

- Рассмотрим общие сведения об архитектуре БК-0010

- Поговорим об интерфейсах, о том, как их создавать и как с ними работать.

- Создадим несколько вспомогательных IP, внешний вид и характеристики которых меняются в зависимости от параметров.

Общие сведения об архитектуре

Все элементы БК-0010 (CPU, RAM, ROM, порты) связаны между собой через шину МПИ. МПИ – это упрощённый вариант Q-bus от DEC, представляет собой 16-ти разрядную совмещённую (адрес и данные передаются по одним и тем же проводникам) двунаправленную шину.

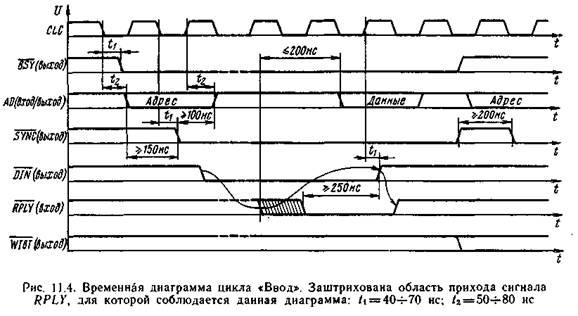

Оригинальная шина МПИ была асинхронная, те или иные сигналы выставлялись на ней с некоторыми задержками, нормированными в наносекундах.

В том случае, если в процессе обмена по шине МПИ, Slave устройство не отвечало слишком долго, происходило прерывание по ошибке шины (в отличие, например, от Z80, где ничего подобного не было). Данная архитектурная особенность используется в БК-0010, поэтому её нужно эмулировать.

В проекте БК-0010 будет использоваться похожая внутренняя шина. Разумеется, нет никакого смысла делать совмещенную двунаправленную шину адреса и данных внутри FPGA, поэтому шин будет три – ADDR, DATAIN, DATAOUT (все по 16 бит). Шина будет полностью синхронной, никаких задержек в наносекундах.

Читайте также: Давление в шинах автомобиля лексус рх 300

В БК-0010 на шине МПИ было только одно Master устройство – CPU, поэтому процедуры захвата шины, прямого доступа к памяти и тому подобного я не реализовывал.

Остальные сигналы я оставил максимально соответствующими оригинальным:

SYNC – Сигнал, сообщающий о том, что Master выставил адрес на шину ADDR. Память адресуется байтами, но по шине данных байт с четным адресом передаётся всегда в младших 8 битах, байт с нечетным в старших.

DIN – Сигнал, сообщающий о том, что Master запросил чтение по ранее выставленному адресу. Чтение осуществляется всегда двухбайтовыми словами, если Master-у нужен только один байт, то второй игнорируется.

DOUT – Сигнал, сообщающий о том, что Master выставил данные на шину DATAOUT и требует, чтобы данные были записаны по ранее выставленному адресу.

WTBT – Сигнал, указывающий на то, что осуществляется байтовая операция. Выставляется только в цикле записи. Master обязан выставить записываемый байт либо в младшие 8 бит шины DATAOUT (в случае чётного адреса) либо в старшие (в случае нечётного). Оставшийся байт игнорируется Slave-устройством.

RPLY – Сигнал, с помощью которого Slave сообщает Master-у о том, что он закончил цикл шины (выставил данные в цикле чтения либо принял их в цикле записи). Если сигнал не приходит в течение 64 циклов, происходит прерывание по ошибке шины.

VIRQ – Сигнал требования прерывания.

IAKO – Сигнал подтверждения/запроса адреса прерывания. Данный сигнал проходил последовательно через все устройства, которые могли потребовать прерывание. Если устройству в данный момент прерывание не требовалось, то оно передавало сигнал дальше по цепочке. Если устройство в данный момент требовало прерывание, то оно не передавало сигнал дальше и начинало цикл передачи адреса прерывания. Позицией устройства в цепочке передачи сигнала IAKO определялся относительный его приоритет.

Прерывания от внешних устройств в БК-0010 используются, поэтому эти сигналы нужны.

Шины и интерфейсы

С шинами и интерфейсами есть некоторая терминологическая путаница, на которую нужно обратить внимание. В Verilog/VHDL шиной (bus) называется связанный набор однотипных цифровых сигналов, предназначенный для передачи многоразрядных чисел. Например шина данных, состоящая из восьми бит.

Кроме того, шиной так же принято называть совокупность разнородных сигналов (сигналы для данных, адреса, управления). Например шина PCI, шина AXI4, в нашем случае шина МПИ. Такая конструкция в терминологии Xilinx Vivado называется интерфейс (interface).

Нам придётся работать с шиной МПИ в нескольких местах. Этот интерфейс будут иметь как минимум CPU, RAM, ROM, порты внешних устройств. Для удобства работы мы сделаем его описание как единой сущности, чтобы не пришлось каждый раз вручную соединять каждый сигнал.

Для этого в Vivado вызываем инструмент Tools->Create interface:

Добавляем сюда все необходимые сигналы, указываем их направление (для Slave направление будет автоматически инвертировано по сравнению с Master), обозначаем, какие сигналы должны присутствовать обязательно, а какие могут отсутствовать. Отдельно отмечаем синхросигналы и сигналы сброса.

Описание интерфейса сохраняется в формате xml. Для того, чтобы мы в проекте могли с ним работать, необходимо в свойствах проекта добавить путь к папке с этим файлом.

IP-модуль с настраиваемыми характеристиками

Рассмотрим как создавать такие модули на примере интерконнекта. Интерконнект — это модуль, который соединяет между собой Master и Slave порты. Поскольку количество портов заранее не известно, этот параметр должен быть настраиваемым. Сам модуль интерконнекта в нашем случае весьма прост, поскольку нам не требуется ни преобразования ширины шины, ни буферизации. Его можно реализовать на комбинационной логике.

Читайте также: Какая высота протектора у новой зимней шины бриджстоун близак vrx

В нашем случае у нас будет только один процессор, соответственно интерконнекту достаточно иметь только один Slave порт. Количество Master портов будет задаваться параметром MASTER_INTERFACES:

Текущая ревизия модуля поддерживает до 11 Master портов, естественно это количество можно сделать любым.

- Создаём головной файл модуля, в котором описываем все сигналы, которые могут в этот модуль прийти. Их будет очень много — нам надо описать все сигналы для всех возможных портов MPI (1 Slave + 11 Master) + сигналы clk и rst. Пока что сигналы clk и rst в модуле не используются, поскольку он целиком сделан на комбинационной логике, но я оставил их для единообразия, вдруг в будущем потребуется буферизация или что-то подобное.

Преобразуем наш модуль в IP (Tools->Create and Package new IP). После этого у нас в Project Manager появляется новый пункт Package IP, где можно настраивать параметры проекта.

На вкладке Interfaces создаём 12 интерфейсов MPI, используя описание интерфейса, созданное на предыдущем этапе.

Настраиваем маппинг между созданными интерфейсами MPI и сигналами модуля. Если сигналы модуля названы так же, как порты в интерфейсе, то Vivado сделает этот маппинг сама, но в данном случае она не сможет догадаться, что сигналы M00_ADDR и M00_DIN относятся к нулевому Master порту, а M02_DOUT ко второму, так что придётся кое-что подправить руками.

Задаём список возможных значений для параметра MASTER_INTERFACES. Кроме списка можно использовать также значения в шестнадцатеричном либо десятичном виде, checkbox, radio button.

Настраиваем условия видимости портов. Порты S00_MPI и M00_MPI у нас видны всегда, порт M01_MPI помечаем как optional и то, что он должен быть виден лишь при условии $MASTER_INTERFACES > 1. Аналогично поступаем с остальными портами Master.

Используя опции условной компиляции в Verilog, создаём необходимую логику работы нашего модуля, в зависимости от значения параметра MASTER_INTERFACES:

Теперь вместо полутора сотен сигналов у нас есть аккуратный список из 12 интерфейсов, которые мы можем использовать в блочном дизайне:

На этом этапе мы также создаём несколько модулей с интерфейсом MPI, это модули RAM и ROM. Их реализация довольно тривиальна, в основе лежит конечный автомат, реализующий логику работы шины MPI, а конкретно циклов чтения (ROM) либо чтения и записи (RAM). Модулей ROM у нас три — один для системного монитора, другой для интерпретатора языка Фокал и третий для модуля тестов. Размер каждого модуля по 8 КБ, все они создаются на основе блочной памяти FPGA. Размер модуля RAM 32КБ.

Важный момент — пространства имён не поддерживаются, поэтому массивы для инициализации разных ROM необходимо называть по-разному. Одинаковое название (даже в разных IP) приводит к труднодиагностируемой ситуации, когда один ROM инициализируется содержимым другого, при этом никаких warning-ов об этом не выдаётся.

Начинаем собирать наш проект. Пока у нас есть немного — модуль интерконнекта и модули RAM и ROM:

Сигналы clk и rst пока никуда не подключены, мы их подключим как только разберёмся с clock domains. У модуля RAM осталось много неподключенных сигналов — туда будет подключаться контроллер дисплея. Слева у интерконнекта остался интерфейс MPI Slave. Сюда будет подключен модуль CPU.

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле