Новая версия HyperTransport 3.1 лишила процессоры INTEL с шиной QPI преимущества этой быстрой шины. Предыдущая спецификация HyperTransport 3.0 имела пиковую пропускную способностью до 41,6 Гбайт/c. В стандарте была введена поддержка частот 1,8 ГГц, 2.0 ГГц, 2,4 ГГц, 2,6 ГГц, функции «горячего подключения», динамического изменения частоты шины и энергопотребления, динамического конфигурирования и других инновационных решений. Максимальное расстояние передачи данных без потери эффективности по шине HT 3.0 составляла 1 метр. Улучшена поддержка многопроцессорных конфигураций, добавлена возможность автоматического конфигурирования для достижения наибольшей производительности. Основные технические характеристики технологии Hyper-Transport HT 3.0 приведены в табл. 1. Физическая реализация дифференциальной линии масштабируемой шины HT показана на рис. 1.

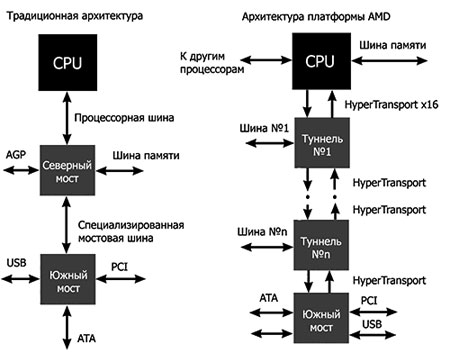

Опираясь на высокоскоростную шину HyperTransport архитектура AMD64 позволила создавать системы, избавленные от недостатков предыдущих поколений архитектур и обладающие высокой масштабируемостью. Начиная со спецификации HyperTransport 3.0 был анонсирован низковольтный дифференциальный интерфейс Hyper-Transport HTX (рис. 1) и коннектор HTX (внешний разъем), что позволило протоколу HT работать с внешними устройствами. Специалисты признают, что на сегодняшний день шина Hyper-Transport 3.0 является наиболее быстрой и имеет очень гибкий протокол обмена.

Рис. 1. Принципы физической реализации шины HT (Low Voltage Differential Signaling — LVDS).

Особенностью HT 3.0 является также и режим un-ganging, который позволит динамически, в процессе работы, конфигурировать шину. Например, одна 1×16 HT может виртуально быть сконфигурирована в 2×8 HT. Это может пригодиться при использовании с процессорами, логически разделенными на два ядра. На каждое ядро будет приходиться свой HT-канал.

В персональных компьютерах, как среди внутренних, так и среди периферийных шин, наблюдается тенденция перехода от синхронных параллельных шин к высокочастотным последовательным. Все эти нововведения и смена приоритетов преследуют, в конечном счете, одну цель — повышение суммарного быстродействия системы, ибо не все существующие архитектурные решения способны эффективно масштабироваться. Последовательные шины не обязательно «однобитные», возможны и 2, и 8, и 32 бит ширины при сохранении присущей последовательным шинам пакетной передачи данных (рис. 2), то есть в пакете импульсов содержатся данные, адрес, CRC и другая служебная информация, разделенная на логическом уровне.

Рис. 2.

Основным отличием параллельных шин от последовательных является сам способ передачи данных. В параллельных шинах понятие «ширина шины» соответствует ее разрядности, т. е. количеству сигнальных линий, на которые одновременно выставляют передаваемые данные. Сигналом для старта и завершения цикла приема/передачи данных служит внешний синхросигнал. В последовательных же каналах передачи используется одна сигнальная линия, или используется две отдельные линии (каналы) для разделения потоков приема-передачи. Соответственно, информационные биты здесь передаются последовательно.

Ширина последовательной шины определяется количеством одновременно задействованных отдельных последовательных каналов передачи. Данные для передачи через последовательную шину облекаются в пакеты. Пакет это единица информации, передаваемая как целое между двумя устройствами. В пакет, помимо собственно полезных данных, включается некоторое количество служебной информации: стартовые/стоповые биты, заголовки пакетов, синхросигналы, биты четности или контрольные суммы и т. п.

Пропускная способность HyperTransport 3.1 по сравнению с текущей версией 3.0 увеличена на 23%. Увеличение максимальной тактовой частоты с 2,6 ГГц до 3,2 ГГц позволяет выполнить до 6,4 миллиардов передач в секунду, что в случае 16-битной связи соответствует высокой пропускной способности 25,6 Гбайт/с, а в случае 32-разрядной — истинно впечатляющие 51,2 Гбайт/с (максимальная производительность QPI составляет 6,4 миллиарда передач в секунду, что соответствует пропускной способности 25,6 Гбайт/с, но как уже отмечалось выше — это не является пределом для QPI). Еще более приметно увеличена тактовая частота в спецификации соединителей, используемых для связи между платами (HTX3) — с 800 МГц до 2,6 ГГц. Этот шаг нацелен, в частности, на повышение скорости взаимодействия процессоров и сопроцессоров, реализованных силами FPGA на отдельных платах.

Данные для передачи через последовательную шину облекаются в

Всё течёт, всё меняется. В сфере компьютерных технологий эта фраза никогда не потеряет актуальности, равно как и девиз «Быстрее! Выше! Сильнее!». И действительно, последние несколько лет можно назвать «временами перемен» компьютерной индустрии. В полной мере это коснулось и такой специфичной области, как шины передачи данных.

Среди наиболее динамично развивающихся областей компьютерной техники стоит отметить сферу технологий передачи данных: в отличие от сферы вычислений, где наблюдается продолжительное и устойчивое развитие параллельных архитектур, в «шинной» 1 сфере, как среди внутренних, так и среди периферийных шин, наблюдается тенденция перехода от синхронных параллельных шин к высокочастотным последовательным. (Заметьте, «последовательные» – не обязательно значит «однобитные», здесь возможны и 2, и 8, и 32 бит ширины при сохранении присущей последовательным шинам пакетной передачи данных, то есть в пакете импульсов данные, адрес, CRC и другая служебная информация разделены на логическом уровне 2 ).

Читайте также: Маркировка шин с шипом

Все эти нововведения и смена приоритетов преследуют в конечном итоге одну цель – повышение суммарного быстродействия системы, ибо не все существующие архитектурные решения способны эффективно масштабироваться. Несоответствие пропускной способности шин потребностям обслуживаемых ими устройств приводит к эффекту «бутылочного горлышка» и препятствует росту быстродействия даже при дальнейшем увеличении производительности вычислительных компонентов – процессора, оперативной памяти, видеосистемы и так далее.

Процессорная шина

Любой процессор архитектуры x86CPU обязательно оснащён процессорной шиной. Эта шина служит каналом связи между процессором и всеми остальными устройствами в компьютере: памятью, видеокартой, жёстким диском и так далее. Так, классическая схема организации внешнего интерфейса процессора (используемая, к примеру, компанией Intel в своих процессорах архитектуры х86) предполагает, что параллельная мультиплексированная процессорная шина, которую принято называть FSB (Front Side Bus), соединяет процессор (иногда два процессора или даже больше) и контроллер, обеспечивающий доступ к оперативной памяти и внешним устройствам. Этот контроллер обычно называют северным мостом , он входит в состав набора системной логики ( чипсета ).

Используемая Intel в настоящее время эволюция FSB – QPB , или Quad-Pumped Bus, способна передавать четыре блока данных за такт и два адреса за такт! То есть за каждый такт синхронизации шины по ней может быть передана команда либо четыре порции данных (напомним, что шина FSB–QPB имеет ширину 64 бит, то есть за такт может быть передано до 4х64=256 бит, или 32 байт данных). Итого, скажем, для частоты FSB, равной 200 МГц, эффективная частота передачи адреса для выборки данных будет эквивалентна 400 МГц (2х200 МГц), а самих данных – 800 МГц (4х200 МГц) 3 .

В архитектуре же AMD64 (и её микроархитектуре K8), используемой компанией AMD в своих процессорах линеек Athlon 64/Sempron/Opteron, применён революционно новый подход к организации интерфейса центрального процессора – здесь имеет место наличие в самом процессоре нескольких отдельных шин. Одна (или две – в случае двухканального контроллера памяти) шина служит для непосредственной связи процессора с памятью, а вместо процессорной шины FSB и для сообщения с другими процессорами используются высокоскоростные шины HyperTransport. Преимуществом данной схемы является уменьшение задержек (латентности) при обращении процессора к оперативной памяти, ведь из пути следования данных по маршруту «процессор – ОЗУ» (и обратно) исключаются такие весьма загруженные элементы, как интерфейсная шина и контроллер северного моста.

Различия реализации классической архитектуры и АМD-K8

Ещё одним довольно заметным отличием архитектуры К8 является отказ от асинхронности, то есть обеспечение синхронной работы процессорного ядра, ОЗУ и шины HyperTransport, частоты которых привязаны к «шине» тактового генератора (НТТ), которая в этом случае является опорной. Таким образом, для процессора архитектуры К8 частоты ядра и шины HyperTransport задаются множителями по отношению к НТТ, а частота шины памяти выставляется делителем от частоты ядра процессора 4

В классической же схеме с шиной FSB и контроллером памяти, вынесенным в северный мост, возможна (и используется) асинхронность шин FSB и ОЗУ, а опорной частотой для процессора выступает частота тактирования 5 (а не передачи данных) шины FSB, частота же тактирования шины памяти может задаваться отдельно. Из наиболее свежих чипсетов возможностью раздельного задания частот FSB и памяти обладает NVIDIA nForce 680i SLI, что делает его отличным выбором для тонкой настройки системы (разгона).

HyperTransport

Эмблема HyperTransport Technology Consortium

HyperTransport – это прежде всего технология, управлением спецификациями и продвижением которой занимается HyperTransport Technology Consortium, куда входят такие компании, как Advanced Micro Devices (AMD), Alliance Semiconductor, Apple Computer, Broadcom Corporation, Cisco Systems, NVIDIA, PMC-Sierra, Sun Microsystems, Transmeta и ещё более 140 малых и больших компаний.

Основные особенности и возможности, предоставляемые технологией HyperTransport

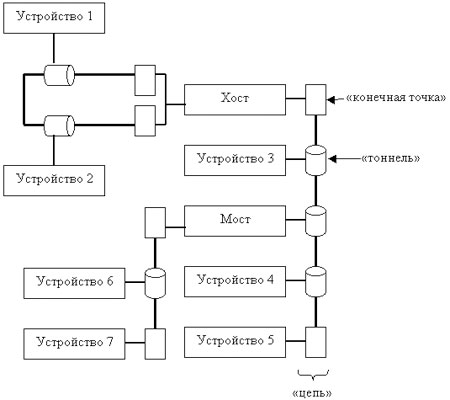

Технология HyperTransport (ранее известная как Lightning Data Transport) – это последовательная (пакетная) связь, построенная по схеме peer-to-peer (точка-точка), обеспечивающая высокую скорость при низкой латентности (low-latency responses). HyperTransport имеет оригинальную топологию на основе линков, тоннелей, цепей (цепь – последовательное объединение нескольких туннелей) и мостов (мост выполняет маршрутизацию пакетов между отдельными цепями), что позволяет этой архитектуре легко масштабироваться. Иными словами, HyperTransport призвана упростить внутрисистемные сообщения (передачи) посредством замены существующего физического уровня передачи существующих шин и мостов, а также снизить количество узких мест и задержек. При всех этих достоинствах HyperTransport характеризуется также малым числом выводов (low pin counts) и низкой стоимостью внедрения. HyperTransport поддерживает автоматическое определение ширины шины 6 , допуская ширину от 2 до 32 бит в каждом направлении, использует Double Data Rate, или DDR (данные посылаются как по переднему, так и по заднему фронтам сигнала синхронизации), кроме того, она позволяет передавать асимметричные потоки данных к периферийным устройствам и от них.

Читайте также: Давление в шинах хендай туссан 2019 2 литра

Топология шины HyperTransport

На данный момент консорциумом HyperTransport разработана уже третья версия спецификации, согласно которой шина HyperTransport может работать на частотах до 2,6 ГГц (сравните с шиной PCI и её 33 или 66 МГц). Это позволяет передавать до 5200 миллионов пакетов в секунду при частоте сигнала синхронизации 2,6 ГГц; частота сигнала синхронизации настраивается автоматически.

Полноразмерная (32-битная) полноскоростная (2,6 ГГц) шина способна обеспечить пропускную способность до 20800 МБ/с (2*(32/8)*2600) в каждую сторону, являясь на сегодняшний день самой быстрой шиной среди себе подобных.

Самые известные решения c использованием HyperTransport:

Использование шины НyperТransport на примере двухпроцессорной системы на базе AMD Opteron

Последовательные и параллельные шины

Дата добавления: 2014-11-28 ; просмотров: 10343 ; Нарушение авторских прав

По способу передачи сигнала все шины можно разделить на последовательные и параллельные.

Основным отличием параллельных шин от последовательных является сам способ передачи данных. Параллельные шины можно рассматривать как совокупность сигнальных линий (можно сказать что просто проводников), объединённых по их назначению (данные, адреса, управление), которые имеют определённые электрические характеристики и протоколы передачи информации. Группы этих сигнальных линий также называются шинами:

— Линии для обмена данными (шина данных);

— Линии для адресации данных (шина адреса);

— Линии для управления данными (шина управления);

Для каждой из этих шин вводится понятие ширины. В параллельных шинах понятие «ширина шины» соответствует её разрядности – количеству сигнальных линий, или, другими словами, количеству одновременно передаваемых («выставляемых на шину») битов информации. Сигнал на каждой линии может принимать два значения 0 и 1 (линия с двумя состояниями). Сигналом для старта и завершения цикла приёма/передачи данных служит внешний синхросигнал.

Для передачи в шине может использоваться положительная логика или отрицательная логика. При положительной логике высокий уровень напряжения соответствует логической единице на соответствующей линии связи, низкий – логическому нулю. При отрицательной логике – наоборот.

На рис … показана в приближенном виде передача данных по шине шириной 8 разрядов (т.е. шина имеет 8 линий для передачи данных и одну для синхросигнала). Понятно, что за один цикл по 8-разрядной шине может передаваться один байт.

Проблема параллельных шин в том, что каждая линия такой шины имеет свою длину, свою паразитную ёмкость и индуктивность, а также взамоиндуктивность. При параллельной передаче байты мешают друг другу вследствие наличия взаимоиндуктивности, поэтому вероятность ошибок увеличивается, чем ограничивается частота шины.

Помимо линий (проводников) важным компонентом шины является контроллер шины,который осуществляет управление процессом обмена данными и служебными сигналами и обычно выполняется в виде отдельной микросхема либо интегрируется в микросхемы Chipset. Для работы контроллера шины нужен внешний синхронизирующий сигнал (тактовая частота), который вырабатывается опорным генератором.

Еще раз обсудим особенности каждой из видов шин (линий), перечисленных выше.

Шина данных – это основная шина, по которой собственно и происходит передача информации. Количество ее разрядов (линий связи) определяет скорость и эффективность информационного обмена. Скорость передачи данных (она же пропускная способность) высчитывается по формуле:

скорость передачи данных = тактовая частота * разрядность * [2..4]

Полученное число не является реальным. В жизни на шины влияет куча всевозможных факторов: неэффективная проводимость материалов, помехи, недостатки конструкции и сборки а также многое другое. По некоторым данным, разность между теоретической скоростью передачи данных и практической может составлять до 25%.

| Будет передано |

| Синхросигнал |

| Рисунок Работа параллельной шины, сигналы на линии данных |

Шина данных всегда двунаправленная, так как предполагает передачу информации в обоих направлениях.

Шина адреса — вторая по важности шина, которая определяет максимально возможную сложность микропроцессорной системы, то есть допустимый объем памяти и, следовательно, максимально возможный размер программы и максимально возможный объем запоминаемых данных. Количество адресов, обеспечиваемых шиной адреса, определяется как N =2 I , где I, – количество разрядов. Разрядность шины адреса обычно кратна 4 и может достигать 64. Шина адреса может быть однонаправленной (когда магистралью всегда управляет только процессор) или двунаправленной (когда процессор может временно передавать управление магистралью другому устройству).

Для снижения общего количества линий связи магистрали часто применяется мультиплексирование шин адреса и данных. То есть одни и те же линии связи используются в разные моменты времени для передачи как адреса, так и данных (в начале — адрес, потом — данные). Понятно, что мультиплексированная шина адреса/данных обеспечивает меньшую скорость обмена. Иногда в шинах применяется частичное мультиплексирование, то есть часть разрядов данных передается по немультиплексированным линиям, а другая часть — по мультиплексированным с адресом линиям.

Шина управления — это вспомогательная шина, управляющие сигналы на которой обеспечивают согласование работы процессора (или другого хозяина магистрали, задатчика, master) с работой памяти или устройства ввода/вывода (устройства-исполнителя, slave).

Для успешной передачи данных не достаточно установить их на шине данных и задать адрес на шине адреса. Для того чтобы данные были записаны (считаны) в регистре устройств, подключенных к шине, адреса которых указаны на шине адреса, необходим ряд служебных сигналов: записи/считывания, готовности к приему/передачи данных, подтверждения приема данных, аппаратного прерывания, управления и др. Все эти сигналы передаются по шине управления.

Управляющие сигналы также обслуживают запрос и предоставление прерываний, запрос и предоставление прямого доступа.

Самые главные управляющие сигналы — это стробы обмена, то есть сигналы, формируемые процессором и определяющие моменты времени, в которые производится пересылка данных по шине данных, обмен данными.

— Строб записи (вывода), который определяет момент времени, когда устройство-исполнитель может принимать данные, выставленные процессором на шину данных;

— Строб чтения (ввода), который определяет момент времени, когда устройство-исполнитель должно выдать на шину данных код данных, который будет прочитан процессором.

При этом большое значение имеет то, как процессор заканчивает обмен в пределах цикла, в какой момент он снимает свой строб обмена. Возможны два пути решения, синхронный и асинхронный обмен, (рис. ….) соответственно, шины также делятся на синхронные и асинхронные:

— При синхронном обмене процессор заканчивает обмен данными самостоятельно, через раз и навсегда установленный временной интервал выдержки (tвыд), то есть без учета интересов устройства-исполнителя;

— При асинхронном обмене процессор заканчивает обмен только тогда, когда устройство-исполнитель подтверждает выполнение операции специальным сигналом (так называемый режим handshake — рукопожатие).

Достоинства синхронного обмена – более простой протокол обмена, меньшее количество управляющих сигналов. Недостатки — отсутствие гарантии, что исполнитель выполнил требуемую операцию, а также высокие требования к быстродействию исполнителя, при синхронном обмене приходится искусственно увеличивать длительность строба обмена для соответствия требованиям большего числа исполнителей, чтобы они успевали обмениваться информацией в темпе процессора.

Рисунок Синхронный и асинхронный обмен.

Достоинства асинхронного обмена — более надежная пересылка данных, возможность работы с самыми разными по быстродействию исполнителями. Недостаток — необходимость формирования сигнала подтверждения всеми исполнителями, то есть дополнительные аппаратурные затраты.

Линии шины управления могут быть как однонаправленными, так и двунаправленными.

В последовательных шинах используется одна сигнальная линия (возможно использование двух отдельных каналов для разделения потоков приёма-передачи). Соответственно, информационные биты здесь передаются последовательно. Данные для передачи через последовательную шину облекаются в пакеты (пакет – единица информации, передаваемая как целое между двумя устройствами), в которые, помимо собственно полезных данных, включается некоторое количество служебной информации: старт-биты, заголовки пакетов, синхросигналы, биты чётности или контрольные суммы, стоп-биты и т. п.

В качестве примера приведем описание обмена для последовательного интерфейса RS-232.

Данные передаются пакетами по одному байту (8 бит). Вначале передаётся стартовый бит, противоположной полярности состоянию незанятой линии, после чего передаётся непосредственно кадр полезной информации – 8 бит. Увидев стартовый бит, приемник выжидает интервал T1 и считывает первый бит, потом через интервалы T2 считывает остальные информационные биты. Последний бит — стоповый бит, говорящий о том, что передача завершена. Очень важно, чтобы тактовые частоты приемника и передатчика были одинаковыми, допустимое расхождение — не более 10%.

Рисунок Работа последовательной шины, формат данных RS-232

Последовательные шины – не обязательно значит «однобитные», здесь возможны и 2, и 8, и 32 бит ширины при сохранении присущей последовательным шинам пакетной передачи данных, то есть в пакете импульсов данные, адрес, другая служебная информация разделены на логическом уровне.

Последовательные шины часто используют более чем два состояния линии (иногда дополнительные состояния используют для служебной информации).

Малое количество сигнальных линий и логически более сложный механизм передачи данных последовательных шин оборачиваются для них существенным преимуществом – возможностью наращивания рабочих частот. Последовательный способ передачи имеет преимущество перед параллельным если длина линии превышает хотя бы несколько сантиметров.

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле