Самое главное, что должен знать разработчик микропроцессорных систем — это принципы организации обмена информацией по шинам таких систем. Без этого невозможно разработать аппаратную часть системы, а без аппаратной части не будет работать никакое программное обеспечение.

За более чем 30 лет, прошедших с момента появления первых микропроцессоров, были выработаны определенные правила обмена, которым следуют и разработчики новых микропроцессорных систем. Правила эти не слишком сложны, но твердо знать и неукоснительно соблюдать их для успешной работы необходимо. Как показала практика, принципы организации обмена по шинам гораздо важнее, чем особенности конкретных микропроцессоров. Стандартные системные магистрали живут гораздо дольше, чем тот или иной процессор. Разработчики новых процессоров ориентируются на уже существующие стандарты магистрали. Более того, некоторые системы на основе совершенно разных процессоров используют одну и ту же системную магистраль. То есть магистраль оказывается самым главным системообразующим фактором в микропроцессорных системах.

Обмен информацией в микропроцессорных системах происходит в циклах обмена информацией. Под циклом обмена информацией понимается временной интервал, в течение которого происходит выполнение одной элементарной операции обмена по шине. Например, пересылка кода данных из процессора в память или же пересылка кода данных из устройства ввода/вывода в процессор. В пределах одного цикла также может передаваться и несколько кодов данных, даже целый массив данных, но это встречается реже.

Циклы обмена информацией делятся на два основных типа:

- Цикл записи (вывода), в котором процессор записывает (выводит) информацию;

- Цикл чтения (ввода), в котором процессор читает (вводит) информацию.

В некоторых микропроцессорных системах существует также цикл «чтение-модификация-запись» или же «ввод-пауза-вывод». В этих циклах процессор сначала читает информацию из памяти или устройства ввода/вывода, затем как-то преобразует ее и снова записывает по тому же адресу. Например, процессор может прочитать код из ячейки памяти, увеличить его на единицу и снова записать в эту же ячейку памяти. Наличие или отсутствие данного типа цикла связано с особенностями используемого процессора.

Особое место занимают циклы прямого доступа к памяти (если режим ПДП в системе предусмотрен) и циклы запроса и предоставления прерывания (если прерывания в системе есть). Когда в дальнейшем речь пойдет о таких циклах, это будет специально оговорено.

Во время каждого цикла устройства, участвующие в обмене информацией, передают друг другу информационные и управляющие сигналы в строго установленном порядке или, как еще говорят, в соответствии с принятым протоколом обмена информацией.

Длительность цикла обмена может быть постоянной или переменной, но она всегда включает в себя несколько периодов сигнала тактовой частоты системы. То есть даже в идеальном случае частота чтения информации процессором и частота записи информации оказываются в несколько раз меньше тактовой частоты системы.

Чтение кодов команд из памяти системы также производится с помощью циклов чтения. Поэтому в случае одношинной архитектуры на системной магистрали чередуются циклы чтения команд и циклы пересылки (чтения и записи) данных, но протоколы обмена остаются неизменными независимо от того, что передается — данные или команды. В случае двухшинной архитектуры циклы чтения команд и записи или чтения данных разделяются по разным шинам и могут выполняться одновременно.

2.1. Шины микропроцессорной системы

Прежде чем переходить к особенностям циклов обмена, остановимся подробнее на составе и назначении различных шин микропроцессорной системы.

Как уже упоминалось, в системную магистраль (системную шину) микропроцессорной системы входит три основные информационные шины: адреса, данных и управления.

Шина данных — это основная шина, ради которой и создается вся система. Количество ее разрядов (линий связи) определяет скорость и эффективность информационного обмена, а также максимально возможное количество команд.

Шина данных всегда двунаправленная, так как предполагает передачу информации в обоих направлениях. Наиболее часто встречающийся тип выходного каскада для линий этой шины — выход с тремя состояниями.

Обычно шина данных имеет 8, 16, 32 или 64 разряда. Понятно, что за один цикл обмена по 64-разрядной шине может передаваться 8 байт информации, а по 8-разрядной — только один байт. Разрядность шины данных определяет и разрядность всей магистрали. Например, когда говорят о 32-разрядной системной магистрали, подразумевается, что она имеет 32-разрядную шину данных.

Видео:Как работает LIN шина автомобиля. K-Line L-Line шины данных. Лин шина автомобиля. Lin-bus networkСкачать

Шина адреса — вторая по важности шина, которая определяет максимально возможную сложность микропроцессорной системы, то есть допустимый объем памяти и, следовательно, максимально возможный размер программы и максимально возможный объем запоминаемых данных. Количество адресов, обеспечиваемых шиной адреса, определяется как 2N, где N — количество разрядов. Например, 16-разрядная шина адреса обеспечивает 65 536 адресов. Разрядность шины адреса обычно кратна 4 и может достигать 32 и даже 64. Шина адреса может быть однонаправленной (когда магистралью всегда управляет только процессор) или двунаправленной (когда процессор может временно передавать управление магистралью другому устройству, например контроллеру ПДП). Наиболее часто используются типы выходных каскадов с тремя состояниями или обычные ТТЛ (с двумя состояниями).

Как в шине данных, так и в шине адреса может использоваться положительная логика или отрицательная логика. При положительной логике высокий уровень напряжения соответствует логической единице на соответствующей линии связи, низкий — логическому нулю. При отрицательной логике — наоборот. В большинстве случаев уровни сигналов на шинах — ТТЛ.

Читайте также: Сервис по подбору шин

Для снижения общего количества линий связи магистрали часто применяется мультиплексирование шин адреса и данных. То есть одни и те же линии связи используются в разные моменты времени для передачи как адреса, так и данных (в начале цикла — адрес, в конце цикла — данные). Для фиксации этих моментов (стробирования) служат специальные сигналы на шине управления. Понятно, что мультиплексированная шина адреса/данных обеспечивает меньшую скорость обмена, требует более длительного цикла обмена (рис. 2.1). По типу шины адреса и шины данных все магистрали также делятся на мультиплексированные и немультиплексированные.

Рис. 2.1. Мультиплексирование шин адреса и данных.

В некоторых мультиплексированных магистралях после одного кода адреса передается несколько кодов данных (массив данных). Это позволяет существенно повысить быстродействие магистрали. Иногда в магистралях применяется частичное мультиплексирование, то есть часть разрядов данных передается по немультиплексированным линиям, а другая часть — по мультиплексированным с адресом линиям.

Шина управления — это вспомогательная шина, управляющие сигналы на которой определяют тип текущего цикла и фиксируют моменты времени, соответствующие разным частям или стадиям цикла. Кроме того, управляющие сигналы обеспечивают согласование работы процессора (или другого хозяина магистрали, задатчика, master) с работой памяти или устройства ввода/вывода (устройства-исполнителя, slave). Управляющие сигналы также обслуживают запрос и предоставление прерываний, запрос и предоставление прямого доступа.

Сигналы шины управления могут передаваться как в положительной логике (реже), так и в отрицательной логике (чаще). Линии шины управления могут быть как однонаправленными, так и двунаправленными. Типы выходных каскадов могут быть самыми разными: с двумя состояниями (для однонаправленных линий), с тремя состояниями (для двунаправленных линий), с открытым коллектором (для двунаправленных и мультиплексированных линий).

Самые главные управляющие сигналы — это стробы обмена, то есть сигналы, формируемые процессором и определяющие моменты времени, в которые производится пересылка данных по шине данных, обмен данными. Чаще всего в магистрали используются два различных строба обмена:

- Строб записи (вывода), который определяет момент времени, когда устройство-исполнитель может принимать данные, выставленные процессором на шину данных;

- Строб чтения (ввода), который определяет момент времени, когда устройство-исполнитель должно выдать на шину данных код данных, который буде прочитан процессором.

При этом большое значение имеет то, как процессор заканчивает обмен в пределах цикла, в какой момент он снимает свой строб обмена. Возможны два пути решения (рис. 2.2):

- При синхронном обмене процессор заканчивает обмен данными самостоятельно, через раз и навсегда установленный временной интервал выдержки (tвыд), то есть без учета интересов устройства-исполнителя;

- При асинхронном обмене процессор заканчивает обмен только тогда, когда устройство-исполнитель подтверждает выполнение операции специальным сигналом (так называемый режим handshake — рукопожатие).

Рис. 2.2. Синхронный обмен и асинхронный обмен.

Достоинства синхронного обмена — более простой протокол обмена, меньшее количество управляющих сигналов. Недостатки — отсутствие гарантии, что исполнитель выполнил требуемую операцию, а также высокие требования к быстродействию исполнителя.

Достоинства асинхронного обмена — более надежная пересылка данных, возможность работы с самыми разными по быстродействию исполнителями. Недостаток — необходимость формирования сигнала подтверждения всеми исполнителями, то есть дополнительные аппаратурные затраты.

Какой тип обмена быстрее, синхронный или асинхронный? Ответ на этот вопрос неоднозначен. С одной стороны, при асинхронном обмене требуется какое-то время на выработку, передачу дополнительного сигнала и на его обработку процессором. С другой стороны, при синхронном обмене приходится искусственно увеличивать длительность строба обмена для соответствия требованиям большего числа исполнителей, чтобы они успевали обмениваться информацией в темпе процессора. Поэтому иногда в магистрали предусматривают возможность как синхронного, так и асинхронного обмена, причем синхронный обмен является основным и довольно быстрым, а асинхронный применяется только для медленных исполнителей.

По используемому типу обмена магистрали микропроцессорных систем также делятся на синхронные и асинхронные.

Видео:CAN шина👏 Как это работаетСкачать

Раздел 1.

В чем состоит принцип магистрально-модульной организации ЭВМ?

Различные функционально-завершённые блоки (модули) подключены к общим магистралям (шинам), посредством которых взаимодействуют между собой, образуя единую вычислительную систему. Передача информации и синхронизирующих сигналов между различными группами функциональных блоков выполняется в режиме разделения времени, т.е. поочерёдно.

Кратко из Угрюмова: В такой структуре имеется группа магистралей (шин), к которым подключаются различные модули (блоки), обменивающиеся между собой информацией поочерёдно, в режиме разделения времени.

Дайте определение шины (магистрали) и перечислите типы шин в ЭВМ.

Магистраль (шина) – совокупность сигналов, соединяющих несколько функциональных блоков ЭВМ.

Шины бывают параллельные – управляющие сигналы и/или биты информации передаются по отдельным проводам одновременно, и последовательностные – сигналы и биты передаются по одним и тем же проводам, но последовательно друг за другом во времени.

Читайте также: Почему растет давление в шинах

Что такое трехшинная и двухшинная организация ЭВМ.

Наиболее типичной является трёхшинная архитектура микропроцессорных систем с шинами адреса (ША или AB (Address Bus)), данных (ШД или DB (Data Bus)) и шиной управления (IE или CB (Control Bus)).

В двухшинной организации шины адреса и данных заменены на одну мультиплексированную шину адреса-данных.

Что такое мультиплексированная шина адреса-данных. Нарисуйте схему подключения памяти с раздельными шинами адреса и данных к процессору с мультиплексированной шиной.

Мультиплексированная шина адреса/данных – это означает, что по одним и тем же проводам последовательно (с разделением во времени) передаются и адреса, и данные.

Дополнительно: Например, для доступа к микросхеме памяти 64Кслов * 16 бит требуется 16-ти разрядная шина адреса А[15:0] и 16-ти разрядная шина данных D[15:0] – всего 32 линии. Если выполнить мультиплексирование адреса и данных, то необходима только 16-ти разрядная мультиплексированная шина А/D[15..0]. При этом доступ к памяти будет медленнее до 2-х раз из-за появления двух этапов: 1) запись адреса: 2) запись/чтение данных.

Чтобы организовать доступ со стороны микропроцессора с мультиплексированной шиной адреса-данных к микросхеме памяти с раздельными шинами необходимо использовать дополнительный регистр-защелку адреса, который сохраняет адрес на время, пока шина используется для передачи данных.

Постройте структурную схему ЭВМ с одноуровневой системной шиной.

Видео:Кан шина, что это? Поймет школьник! принцип работыСкачать

Что такое сторожевой таймер (WatchDog)? Нарисуйте схему подключения сторожевого таймера к процессору.

WDT – специальное аппаратное устройство, предназначенное для обнаружения программных сбоев и по возможности их исправления.

Дополнительно: Представляет собой цифровой двоичный счётчик, тактируемый от независимого генератора, после переполнения счетчика вырабатывается специальный сигнал, который может либо генерировать сброс, либо вырабатывать системное прерывание.

Чтобы сигнала тревоги не вырабатывалось, ЦП 1 раз в определённое время вырабатывает специальный сигнал сброса WDT (сигнал обнуления).

Это устройство ставится не во всех системах – потому что приходится расставлять команды для таймера. Сторожевой таймер может выноситься из системы наружу.

Что такое часы реального времени (RealTimeClock, RTC)? Нарисуйте схему подключения RTC в ЭВМ. Какие интерфейсы обычно используются для подключения RTC.

Часы реального времени (Real-time clock, RTC) – специализированная микросхема с пониженным энергопотреблением и обычно с автономным питанием. Позволяет вести счет астрономического времени даже тогда, когда главный источник питания выключен. (Обеспечивают течение реального времени.)

Для подключения используются:

1. Последовательный интерфейс: I 2 C, 3-wire, SPI.

2. Параллельный интерфейс: с мультиплексированной шиной «адрес/данные», с разделенными шинами адреса и данных.

3. Однопроводный интерфейс: 1-wire.

Что такое адресное пространство шины и объем подключенной памяти? Как они рассчитываются.

Адресное пространство шины – множество всех адресов, которые можно передать по шине.

Шина адреса на схемах обозначается А[n:0]. Отдельные сигналы (провода) шины адреса обозначаются Ах или А[х] (х=0..n). Число х обозначает номер двоичного разряда адреса, передаваемого по шине. Разрядностью (или шириной) шины адреса называется количество сигналов (разрядов) шины равное (n+1). При такой разрядности обеспечивается доступ к ячейкам памяти по адресам от 0 до (2 n – 1). У параллельной шины с (n+1) линиями адреса адресное пространство составит множество от 0 до (2 n – 1).

Каждая ячейка памяти может иметь различную разрядность ячейки Nb: ячейка может быть или 8-разрядной (1 байт) или иметь большую разрядность, например, 4 байта = 32 бита. Это не изменяет адресного пространства, но увеличивает объем адресуемой памяти, который в байтах рассчитывается как 2 n * Nb. Когда описывают память ЭВМ часто указывают именно данное выражение – (2 n * Nb), которое отражает объем и организацию памяти. Например. (2К*1б) – это 2048 слов по 16 бит = 4 Кбайт: (8М*32) – это (8 * 2 20 ) слов по 4 байта = 32 Мбайт.

Видео:Подробно про CAN шинуСкачать

Что такое шина управления, сигнальная шина управления и командная шина управления. К какому типу относится шина управления у микроконтроллеров семейства MCS51?

Шина управления – совокупность управляющих и синхронизирующих сигналов различного назначения.

Сигнальные шины – это набор групп электрических сигналов, каждая из которых поддерживает определенную функцию: управление записью – чтением в память, управление режимами и процессом прямого доступа к памяти (ПДП), сигналы прерывания и т.д. У сигнальных шин управления нет единой функции, подобно шине адреса и данных.

Командные шины (например, PCI) подразумевают передачу кодов команд общей магистрали (по основной шине данных или по выделенной шине команд). Выделенные сигналы управления отдельными функциями используются в ограниченном объеме – только для управления самой шиной управления (например, выделенные синхросигналы шины или сигналы сброса).

Назовите отличительные особенности в организации внутрикристальных шин (SoC).

Внутрикристальные шины могут быть гораздо шире, чем шины на печатных платах. Это позволяет повысить эффективность передачи и уменьшить скорость модуляции. Другими словами, с увеличением ширины шины растет пропускная способность, а с уменьшением скорости модуляции снижается энергопотребление.

Опишите назначение сигналов CS (ChipSelect) с указанием проблем, при их отсутствии?

За синхронное переключение ведомых устройств на шине (микросхем памяти, контроллеров) в режим записи чтения отвечает процессор – он формирует управляющие сигналы команд записи, чтения, ожидания и т.п. Однако необходимо еще разделить во времени доступ к нескольким устройствам, подключенным на шину параллельно. Например, на шину может быть подключено несколько микросхем памяти и несколько контроллеров ввода-вывода. Логически они различаются диапазоном адресов, закрепленным за каждым из этих устройств. Однако физически на каждое из устройств (памяти, контроллер) подключена одна и та же шина адреса, и каждое устройство воспринимает адреса, начиная с 0. Если попытаться считать значение из ячейки с адресом 0, то все микросхемы выставят на шину данных различные – «свои» – значения, в результате чего произойдет конфликт на шине.

Читайте также: Шины в челябинске из рук в руки

Чтобы избежать описанной ситуации каждая микросхема имеет специальный управляющие вход «выбора кристалла» (Chip Select, CS или Chip Enable, CE) или сигнал «разрешение вывода (на шину данных)» (Output Enable, OE). Только в том случае, если сигнал CS/CE/OE активный микросхема вводит/выводит на шине данных в соответствии с поданными на нее сигналами управления. В противном случае она переводит выходы шины данных в состояние высокого сопротивления и не мешает работе других устройств на шине.

В случае CS/CE микросхема в неактивном режиме отключает не только вывод на шину данных, но и остальные внутренние функции, в том числе запись, а также переходит в режим пониженного энергопотребления. Сигнал OE только отключает вывод на шину, а остальные функции работают без изменения.

Источником сигналов CS/CE/OE будет являться процессор или контроллер шины. Специальный функциональный блок (в процессоре, или в контроллере шины) называемый «Селектор адреса» вырабатывает сигналы CS/CE/OE для каждого устройства на шине из адреса, сформированного процессором.

Нарисуйте схему селектора адреса, обеспечивающего выборку микросхем SRAM (256 байт) согласно следующей карте адресного пространства 0x00-0xFF: SRAM1; 0x100 – 0x17F: RAM2; 0x180-0x27F: SRAM3.

Назначение сигналов LB, UB (Lower Byte, Upper Byte) на шине с шириной данных 16 бит?

LB (Lower Byte) и UB (Upper Byte) — два сигнала выбора байта на шине: выбора младшего банта /LB и старшего байта /UB на 16-ти разрядной шине данных для выполнения текущей операции записи. Эго необходимо если по 16-разрядной шине нужно записать только один младший (старший) байт, не изменяя второго – старшего (младшего) байта.

Например, нужно записать байт 0x55 по адресу 0x0000. Так как шина данных 16-ти разрядная, то она «покрывает» 2-ве байтовых ячейки памяти по соседним адресам: четному и нечетному. Если на шину адреса выставлен 0x0000, то разряды данных [D7..D0] попадают в байтовую ячейку памяти с адресом 0x0000. а разряды [D15..D7] – в байтовую ячейку памяти с адресом 0x0001. Соответственно на младших разрядах шины данных [D7..D0] процессор устанавливает записываемое значение 0x55, а на старших разрядах [D15..D8] значение не определено и может быть установлено процессором в любое состояние, например, 0x00. Если теперь выполнить операцию записи в микросхему ОЗУ с 16-ти разрядным доступом, то ячейка [0x0000] = 0x55 (это правильно), но ячейка [0x0001] = 0x00 (ЭТО НЕВЕРНО. «ИСПОРЧЕНЫЕ» ДАННЫЕ ЗАПИСАННЫЕ В ЭТУ ЯЧЕЙКУ РАНЕЕ). Чтобы избежать такой ситуации, используется дополнительный активный сигнал /LB, разрешающий запись младшего байта с шины данных. При этом сигнал /UB должен оставаться неактивным. Если нужно выполнить запись старшего байта с шины данных (запись байта по нечетному адресу), то наоборот: будет активный /UB и неактивный /LB. Если нужно записать 16-ти разрядное слово целиком, то активные оба сигнала: и /UB и /LB.

Видео:Блок управления, генератор, CAN или LIN шина либо АКБ? P0401, P0523, U1113, U1132, U0106 (Видео 90)Скачать

При операциях чтения сигналы выбора байтов работают аналогично, но в большинстве случаев в этом нет необходимости, так как процессор сам может считать только один из бантов, выставленных на шину данных, или, если нужно, оба байта.

Постройте временную диаграмму цикла чтения из асинхронной памяти, с управляющими сигналами RD(OE), WR(WE), CS

Постройте временную диаграмму цикла записи в асинхронную память, с управляющими сигналами RD(OE), WR(WE), CS

Постройте временную диаграмму цикла чтения из асинхронной памяти, с управляющими сигналами R/nW, E, CS

Постройте временную диаграмму цикла записи в асинхронную память, с управляющими сигналами R/nW, E, CS

Постройте временную диаграмму цикла чтения на шине с подтверждением (REQ – ACK)

Постройте временную диаграмму цикла записи на шине с подтверждением (REQ – ACK)

Для чего используются циклы ожидания (Wait State)? Поясните на временной диаграмме цикла записи в память.

Введение циклов ожидания (Wait State). В данном случае процессор затягивает длительность сигналов управления операцией на шине (/RD и /WR или R/nW и E), чтобы устройство на шине успело ее выполнить. «Затягивание» выполняется на целое число периодов тактового сигнала процессора, которые называются циклами ожидания. Количество циклов ожидания устанавливается путем записи их числа в специальный конфигурационный регистр контроллера памяти. Чтобы память работала при старте системы, до инициализации числа циклов ожидания, по умолчанию устанавливается максимально возможное число.

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле

- Правообладателям

- Политика конфиденциальности

📽️ Видео

Экспресс диагностика CAN шины на автомобиле. №21Скачать

лекция 403 CAN шина- введениеСкачать

LIN шина - пример работы. LIN bus exampleСкачать

поиск нерабочей can шины, часть дваСкачать

MCP2515, контроллер CAN шины с интерфейсом SPIСкачать

Как проверить CAN шину Используем симулятор ElectudeСкачать

Что означает МАРКИРОВКА НА ШИНАХ / Значение всех цифр и букв на резинеСкачать

Шина CAN. Часть 1. Разбираемся как работает CAN bus, разберем кадр данных до "костей".Скачать

Простая проверка CAN шины. Сканер не видит автомобиль через OBD2. Как правильно выбрать изоленту.Скачать

Резина Runflat: мнение шиномонтажникаСкачать

Как Перерабатывают Автомобильные Шины в ЕвропеСкачать

Лекция 308. Шина I2CСкачать

ТИХИЕ ШИНЫ ЭТОГО НЕ ЗНАЮТ БОЛЬШИНСТВО АВТОМОБИЛИСТОВСкачать

Логический анализатор шины i2cСкачать

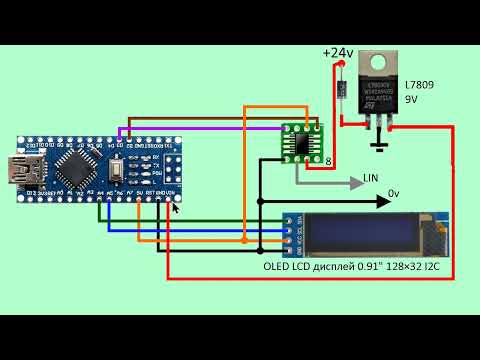

Логический LIN пробник, цифровой тестер лин, к лайн шины автомобиля. На Ардуино, OLED I2C, TJA 1020Скачать