С момента появления домашних компьютеров существует возможность расширять их функционал путём установки большего количества RAM, более ёмких накопителей, дополнительных комплектующих. Но только с появлением IBM PC привычной стала идея о полностью открытой модульной компьютерной системе. А именно, концепция карт расширения позволила пользователям компьютеров не зависеть от конфигураций систем, предлагаемых производителями. Подобные конфигурации можно было, в ограниченных пределах, расширять комплектующими, рассчитанными исключительно на эти системы. Благодаря универсальным картам расширения появились целые отрасли промышленности, они стали и причиной возникновения большого рынка любительских устройств, которые можно было подключать к компьютерам.

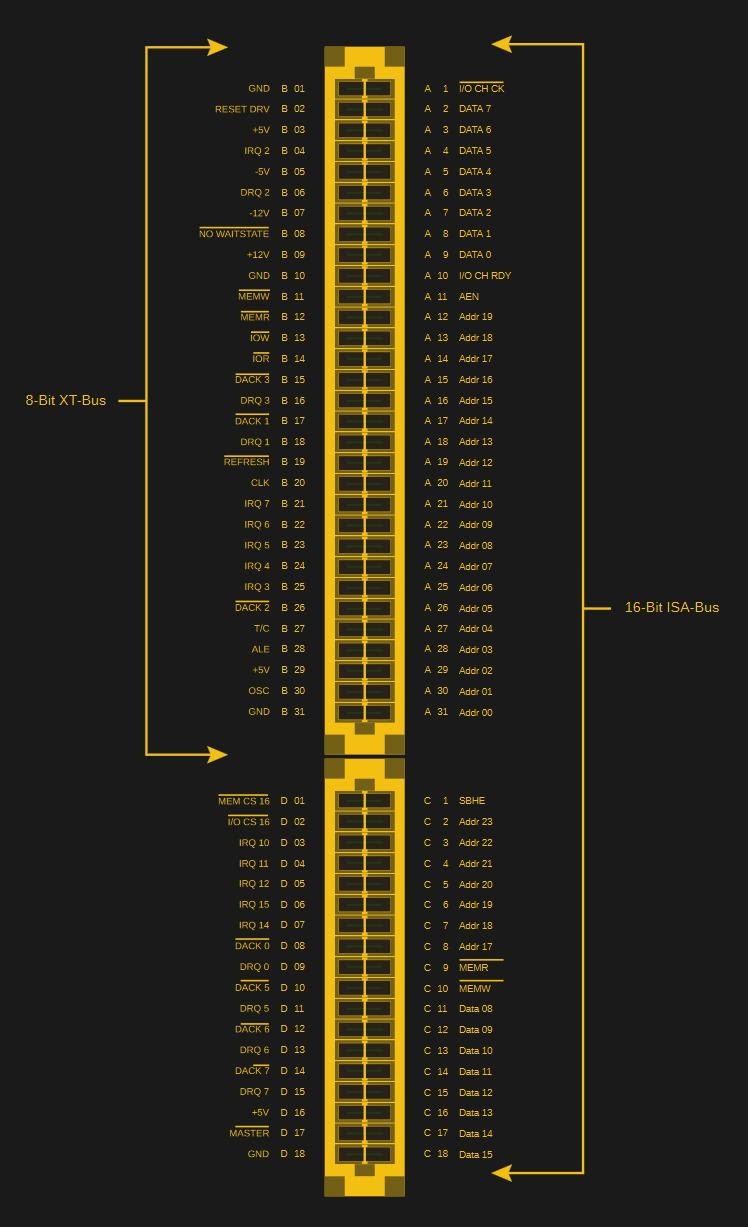

В первом IBM PC было пять 8-битных слотов расширения, подключённых прямо к процессору 8088. Компьютер IBM PC/AT был основан на процессоре 80286, в результате слоты стали 16-битными. С помощью слотов расширения к компьютеру можно было подключать практически всё что угодно: графические и сетевые карты, дополнительную память, какие-то особые платы. Хотя для этих слотов расширения и не существовало официального наименования, во времена PC/AT их называли, соответственно, PC-шинами и AT-шинами. А название Industry Standard Architecture (ISA) — это ретроним, который придумали создатели клонов PC.

Такая открытость ISA означала то, что можно было достаточно легко и дёшево создавать собственные ISA-карты. То же касалось и шины PCI, которая появилась после ISA и была такой же открытой. В результате до сих пор существует полная жизни экосистема, в которой есть место и любительским звуковым картам, рассчитанным на слоты PCI или ISA, и картам расширения, позволяющим оснастить IBM PC 1981-го года поддержкой USB, и много чему ещё.

С чего начать тому, кто в наши дни хочет заняться работой с ISA- и PCI-картами?

Цена простоты

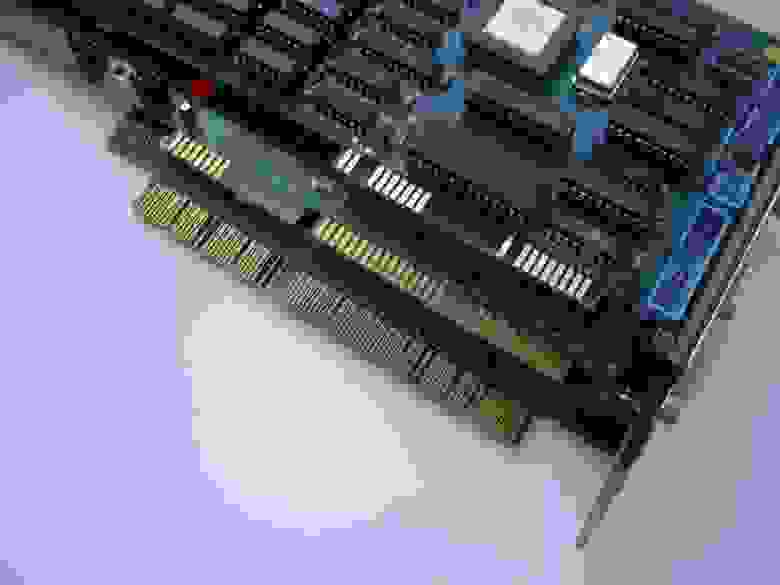

Сверху вниз: 8-битная XT-карта, 16-битная AT/ISA карта, 32-битная EISA-карта

О шине ISA, и о появившихся до неё шинах PC/AT, нужно знать одну важную вещь. Это — не особенно универсальные шины, так как они используются для работы с устройствами, подключёнными к шинам адреса и памяти процессоров 8088 и 80286. Это значит, что, например, тактовая частота шины равняется тактовой частоте соответствующего процессора. А именно, для PC-шины это — 4,77 МГц, а для PC/AT-шины — это 6-8 МГц. Хотя 8-битные карты обычно можно использовать в 16-битных слотах, нет гарантии того, что такие карты, подключённые к этим слотам, будут нормально работать.

По мере того, как разработчики клонов PC использовали в своих моделях компьютеров всё более быстрые процессоры, частота шины AT, в итоге, пришла к значениям, находящимся где-то между 10 и 16 МГц. Это, понятно, привело к тому, что многие существующие AT-карты (ISA) работали в подобных системах неправильно. Через некоторое время большинство производителей оборудования сделало так, чтобы частота шины не была бы напрямую связана с частотой процессора. Но несмотря на то, что в названии шины ISA есть намёк на нечто стандартизированное, настоящего стандарта этой шины не существовало.

Правда, была попытка стандартизировать замену ISA, получившую название Extended ISA (EISA). Эта 32-битная шина, работавшая на частоте 8,33 МГц, была создана в 1988 году. Хотя на рынке домашних компьютеров она и не «взлетела», некоторым вниманием она пользовалась среди пользователей серверного оборудования, особенно — как более дешёвая альтернатива собственной шине IBM Micro Channel architecture (MCA). Компания IBM задумывала эту шину в качестве замены ISA.

В итоге же шина ISA дожила до наших дней, сохранившись, в основном, в промышленном оборудовании и во встраиваемых системах (например, в виде шины LPC), в то время как в других сферах был сначала осуществлён переход на PCI, а позже — на PCIe. А вот интерфейсы для подключения видеокарт к компьютерам шли своим путём. Речь идёт о шинах VESA Local Bus (VLB) и Accelerated Graphics Port (AGP), которые представляют собой специализированные интерфейсы, нацеленные на нужды GPU.

Начало работы с новыми старыми технологиями

Естественным результатом этой бурной истории, в той её части, которая касается ISA, стало то, что тому, кто решил создать новую «карту расширения ISA», следует действовать с осторожностью. Для того чтобы подобное изделие отличалось бы по-настоящему широкой совместимостью, можно разработать 8-битную карту, которая может работать на шинах с частотами, находящимися в диапазоне от 4,77 до 20 МГц. А на разработку 16-битных карт стоит обратить внимание тем, кому не нужно поддерживать компьютеры, основанные на процессоре 8088. При разработке PC/104-карт вообще не должно быть никаких проблем с совместимостью, так как эта шина до крайности близка к наиболее стандартному варианту ISA.

При разработке устройств для ISA и PCI физический интерфейс тоже особых проблем не доставляет, так как и в том и в другом случаях используются контакты, расположенные на ребре платы. Именно такой вариант расположения контактов на платах, актуальный до наших дней, был выбран, преимущественно, из-за его дешевизны и надёжности. На плате расширения нет какого-то физического коннектора. Там, на краю, находятся лишь контактные площадки, которые позволяют подключить плату к слоту. При проектировании подобных плат, правда, надо обращать внимание на их толщину, так как от неё зависит надёжность контакта. Обычно хорошо показывает себя толщина платы в 1,6 мм.

Если кто-то хочет самостоятельно создать ISA или PCI-плату — в интернете можно найти параметры контактов для таких плат. Например — этот отличный обзор. Тут, в частности, есть сведения о расстоянии между контактными площадками, о форме платы в том месте, где находятся контакты, о размерах контактных площадок и о других параметрах плат и контактов.

При проектировании электрических цепей плат стоит знать о том, что ISA использует напряжение в 5 В, а PCI может использовать 5 В, 3,3 В, или и то и другое. В случае с PCI платы различают, используя выступы в PCI-слотах и выемки на картах (ключи). Так, если в слоте имеется один выступ, расположенный на расстоянии 56,21 мм от той его стороны, на котором находятся разъёмы подключаемой к нему карты, то это будет слот, рассчитанный на карты, поддерживающие напряжение 3,3 В. Выступ, расположенный на расстоянии 104,77 мм от края слота, указывает на слот для 5 В-карт. На краях карт есть соответствующие выемки. Если карта поддерживает и 5, и 3,3 В — то на ней будет две выемки (это — так называемые универсальные карты).

Ключи на PCI-картах и разъёмах

Существуют 32-битные и 64-битные варианты PCI. Причём, всеобщий интерес на рынке домашних компьютеров вызвал именно первый вариант шины. Если говорить о развитии PCI, то можно отметить интерфейс PCI-X. Эта шина, в 64-битном варианте, в основном, применялась в серверных системах. В PCI-X удвоена максимальная частота шины (с 66 до 133 МГц) и убрана поддержка 5 В. Поэтому PCI-X-карты часто работают при их установке в слоты PCI, рассчитанные на 3,3 В (то же самое справедливо и для PCI-карт, устанавливаемых в слоты PCI-X). 64-битная карта, и PCI, и PCI-X, может перейти в 32-битный режим в том случае, если она установлена в более короткий, 32-битный слот.

Работа с шинами

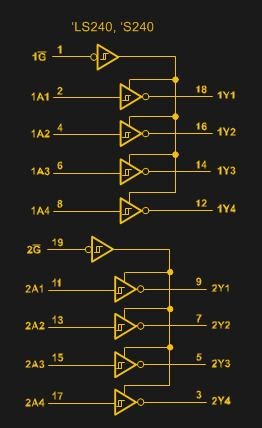

Каждое устройство, подключённое к шине, увеличивает нагрузку на неё. Кроме того, если речь идёт о шинах с общими линиями связи, важно, чтобы отдельные устройства могли бы отключаться от этих линий в то время, когда они эти линии не используют. Обычно для реализации такой схемы работы используется буферный элемент с тремя состояниями. Например — такой, как распространённый 74LS244.

74LS244 может не только обеспечивать изоляцию, что умеют и стандартные цифровые буферы. Этот элемент может переключаться в высокоимпедансное состояние (Hi-Z), что равносильно отключению устройства.

В случае с ISA-картами нам, для организации правильного взаимодействия с шиной, нужно нечто вроде 74LS244 или его двунаправленного варианта 74LS245. У каждой сигнальной линии должен быть буфер или «защёлка». Подробнее об этом можно почитать здесь. А тут описан хороший пример современной ISA-карты, называемой Snark Barker и представляющей собой клон SoundBlaster.

PCI-карты, по идее, тоже можно создавать, используя подобный подход, но обычно в коммерческих PCI-картах используют специализированные интегральные схемы для ускорения ввода-вывода, которые предоставляют компонентам карт простой интерфейс, похожий на ISA. Подобные решения в наши дни, правда, нельзя назвать дешёвыми (если только не рисковать, связываясь с чем-то вроде WCH CH365). Поэтому хорошей альтернативой подобным решениям является реализация PCI-контроллера на базе FPGA. MCA-версия вышеупомянутой карты Snark Barker использует для взаимодействия с шиной MCA CPLD. На сайтах вроде OpenCores имеются проекты, ориентированные на PCI, которые можно использовать в качестве отправной точки для собственных разработок.

Обмен данными с шинами ISA и PCI

После создания новенькой платы с золотыми контактами, и после того, как на ней распаяны буферные элементы или FPGA, нужно ещё и иметь возможность обмениваться данными с шиной ISA или PCI, пользуясь соответствующим протоколом. К счастью, существует множество материалов по ISA, например — этот. А вот протокол PCI, вроде протокола PCIe, это — «коммерческая тайна». В результате соответствующие данные можно официально (и небесплатно) достать лишь на сайте PCI-SIG. Правда, спецификации, всё же, «утекли» в общий доступ.

Конечно, можно использовать существующие ISA- или PCI-проекты в качестве шаблона или руководства для собственных проектов. Вышеупомянутые проекты CPLD/FPGA предлагают нам механизм, позволяющий избежать необходимости в самостоятельной реализации протоколов, а значит — помогают сразу добраться до самого интересного. Создателю платы, в любом случае, придётся использовать систему прерываний (IRQ) для соответствующей шины (выделенные сигнальные линии, основанные, в последних версиях PCI, на сообщениях), а так же учитывать возможность использования DMA (DRQn и DACKn в ISA). Рассказ о тонкостях шин ISA и PCI займёт целую статью. Правда, тем, у кого были ISA-карты с переключателями, или (что хуже), с ISA PnP (Plug’n’Pray), многое из этого должно быть уже знакомо.

Как и в случае с любой другой общей шиной, схема взаимодействия с шиной при записи или чтении данных предусматривает запрос доступа к шине у «хозяина шины» или, в случае с шиной PCI с несколькими «хозяевами», использование процедуры арбитража. К карте расширения, кроме того, можно обращаться напрямую (вот материал об этом, в котором речь идёт об ISA). В Linux это подразумевает использование программ ядра ( sys/io.h ). Сначала получают соответствующие разрешения, а потом уже можно отправлять данные в конкретный IO-порт, соответствующий карте. В целом это выглядит так:

В случае с ISA адрес IO-порта задаётся в самой плате, а для распознавания адреса используется декодер, находящийся на линиях адресного сигнала. Часто на платах для выбора адреса, а так же — линий IRQ и DMA использовались переключатели или перемычки. Технология ISA PnP была призвана улучшить этот процесс, но по факту принесла больше вреда, чем пользы. В случае с PCI технология PnP является частью стандарта. Шина PCI осуществляет поиск устройств при загрузке, а встроенная ROM (BIOS) запрашивает у карт сведения об их нуждах, после чего адреса и другие параметры задаются автоматически.

Итоги

Конечно, если говорить о разработке собственных ISA- или PCI-плат, то тут были рассмотрены лишь самые основы этого дела. Но, надеюсь, мой материал позволил вам хотя бы увидеть общую картину происходящего. Многое из того, что нужно конкретному разработчику карт расширения, зависит от того, какую именно карту он хочет создать, от того является ли она простой 8-битной картой ISA (PC/XT), или 64-битной картой PCI-X.

Правда, шины ISA и PCI хороши тем, что они доступны даже любителям. Скорости этих шин, если нужно отлаживать или анализировать платы, вполне укладываются в возможности любительского аппаратного обеспечения и соответствующих осциллографов. Использование достаточно медленных параллельных шин данных означает, что дифференциальные сигналы тут не применяются, а это облегчает трассировку плат.

Хотя те старые шины, о которых мы говорили, не являются игроками той же лиги, что и шина PCIe, их возможности и их широкая доступность означают, что они могут дать старым компьютерам второй шанс. Даже если речь идёт о чём-то очень простом, вроде накопителя, основанного на флэш-памяти, предназначенного для первого IBM PC.

Занимались ли вы разработкой собственных ISA- или PCI-карт?

Контроллер для isa шины

Шина ISA (Industrial Standart Arhitecture) является фактически стандартной шиной для персональных компьютеров типа IBM PC/AT и совместимых с ними. Шина EISA, с которой ряд фирм выпускал персональные компьютеры, уступила шине PCI и в настоящее время используется редко..

Основные отличия шины ISA персонального компьютера IBM PC/AT от своей предшественницы — шины компьютера IBM PC/XT заключаются в следующем:

- шина AT компьютеров позволяет использовать на внешних платах как 16-разрядные устройства ввода/вывода, так и 16-разрядную память;

- цикл доступа к 16-разрядной памяти на внешней плате может быть выполнен без вставки тактов ожидания;

- объем непосредственно адресуемой памяти на внешних платах может достигать 16 Мб;

- внешняя плата может становиться хозяином (задатчиком) на шине и самостоятельно осуществлять доступ ко всем ресурсам как на шине, так и на материнской плате.

При описании шины целесообразно представить компьютер как состоящий из материнской платы (motherboard) и внешних плат, которые взаимодействуют между собой и ресурсами материнской платы через шину. Все пассивные устройства (не могущие стать задачиками) на шине можно разделить на две группы — память и устройства ввода/вывода (порты). Циклы доступа для каждой из групп отличаются друг от друга как по временным характеристикам, так и по вырабатываемым на шине сигналам.

Чисто условно, для удобства понимания функционирования шины ISA, будем считать, что на материнской плате компьютера существуют следующие устройства, способные быть владельцами (задатчиками) шины: центральный процессор (ЦП), контроллер прямого доступа в память (ПДП), контроллер регенерации памяти (КРП). Кроме этого, задатчиком на шине может быть и внешняя плата. При выполнении цикла доступа на шине задатчиком может быть только одно из устройств. Рассмотрим подробнее функции этих устройств на шине ISA.

Центральный процессор (ЦП) — является основным задатчиком на шине. По умолчанию именно ЦП будет считаться задатчиком на шине. Контроллер ПДП, а также контроллер регенерации памяти запрещают работу ЦП на время своей работы.

Контроллер ПДП — это устройство связано с сигналами запроса на режим ПДП и сигналами подтверждения режима ПДП. Активный сигнал запроса на ПДП будет разрешать последующий захват шины контроллером ПДП для передачи данных из памяти в порты вывода или из портов ввода в память.

Контроллер регенерации памяти — становится владельцем шины и генерирует сигналы адреса и чтения памяти для регенерации информации в микросхемах динамической памяти как на материнской памяти, так и внешних платах.

Внешняя плата — взаимодействует с остальными устройствами через разъем на шине ISA. Может становиться задатчиком на шине для доступа к памяти или устройствам ввода/вывода.

Кроме этого, на материнской плате компьютера имеется ряд устройств, которые не могут быть задатчиками на шине, но тем не менее взаимодействуют с ней. Это следующие устройства:

Часы реального времени (Таймер-счетчик) — это устройство состоит из часов реального времени для поддержки даты и времени и таймера, как правило на базе микросхемы Intel 8254A. Один из таймеров-счетчиков этой микросхемы вырабатывает импульсы с периодом 15 микросекунд для запуска контроллера регенерации памяти на регенерацию.

Кросс материнской платы — часть материнской платы, которая соединяет разъемы шины ISA для подключения внешних плат с другими ресурсами на материнской плате.

Память на материнской плате — часть или все микросхемы памяти прямого доступа (ОЗУ), используемые для хранения информации ЦП. На внешних платах также могут быть размещены микросхемы дополнительной памяти.

Контроллер прерываний — это устройство связано с линиями запросов прерываний на шине. Прерывания требуют дальнейшего обслуживания ЦП.

Устройства ввода/вывода — часть или все устройства ввода/вывода (такие как параллельные или последовательные порты) могут размещаться как на материнской плате, так и на внешних платах.

Перестановщик байтов данных — это устройство позволяет обмениваться данными между собой 16-разрядными и 8-разрядными устройствами.

Архитектура персонального компьютера IBM PC/AT с точки зрения использования шины ISA показана на рисунке.

Внешние платы, устанавливаемые в разъемы шины, могут быть 8- и/или 16-разрядными. 8-разрядная плата имеет только один интерфейсный разъем и может оперировать только с 8-разрядными данными. 8-разрядный слот также не может быть задатчиком на шине. 16-разрядная плата обязательно имеет два интерфейсных разъема — один основной, такой же как в 8-разрядных платах, и один дополнительный. Такая плата может оперировать как с 8-, так и с 16-разрядными данными и, кроме этого, она может быть задатчиком на шине. Общее число устанавливаемых в разъемы шины плат ограничивается как нагрузочной способностью шины, так и конструктивным исполнением материнской платы. Как правило, допускается устанавливать не более 8 (пять 16-разрядных и три 8-разрядных) внешних плат на шину. Такое ограничение вызвано также и относительно небольшим количеством свободных линий запросов на ПДП и запросов на прерывания, имеющихся на шине.

Читайте также: Списание шин при усн

Центральный процессор по умолчанию является основным владельцем шины, контроллер ПДП и контроллер регенерации памяти могут стать задатчиками на шине, только предварительно запретив работу ЦП. Процесс запрещения работы ЦП состоит в выработке сигнала запроса на ПДП и приема сигнала подтверждения ПДП.

Центральный процессор может быть источником как 16-разрядных операций, так и 32-разрядных. Когда ЦП является 16-разрядным ресурсом, он может выполнять операции как с 16-, так и с 8-разрядными ресурсами на шине. При выполнении ЦП команды, оперирующей с 16-разрядными данными, если ресурс доступа 8- разрядный, то специальными аппаратными средствами на материнской плате в этом случае выполняются два цикла доступа. Если же ЦП является 32-разрядным, то аппаратно на материнской плате компьютера один 32-разрядный цикл работы ЦП с внешним ресурсом должен быть преобразован в два индивидуальных 16-разрядных цикла доступа.

Особенности для внешних плат. Если ЦП является задатчиком на шине, то внешние платы могут функционировать только в режиме памяти или устройства ввода/вывода.

Сигналы для поддержки ПДП заводятся с разъема непосредственно на контроллер ПДП, выполненный, как правило, на микросхеме Intel 8237A. Когда режим ПДП запрашивается каким-либо устройством (хотя бы один из сигналов DRQ становится активным), контроллер ПДП осуществляет захват шины у ЦП. Выдача затем соответствующего сигнала -DACK означает, что контроллер ПДП начал передачу данных. Циклы ПДП не будут выполняться на шине, если сигнал -MASTER будет разрешен с какой-либо внешней платы.

Если запрос на ПДП требуется устройству ввода/вывода, то следует учесть, что каналы 0. 3 ПДП поддерживают передачу только 8-разрядных данных; все данные должны передаваться только по линиям SD . Перестановка байтов в этом случае выполняется аппаратно на материнской плате в соответствии с сигналами SA0 и -SBHE. Такая перестановка может потребоваться, например, при передаче данных из старшего байта 16-разрядной памяти в 8-разрядный порт. Каналы ПДП 5. 7 поддерживают передачу только 16-разрядных данных; все данные должны передаваться как 16-разрядные по линиям SD . Память, участвующая в работе в режиме ПДП по этим каналам, должна быть только 16-разрядной. Перестановщик байтов на материнской плате не будет корректировать несоответствие размеров данных.

ПРИМЕЧАНИЕ: 8-разрядная память со своей стороны может передавать данные в режиме ПДП только 8-разрядным устройствам ввода/вывода; использование 8-разрядной памяти с 16-разрядными устройствами ввода/вывода не допускается.

ВНИМАНИЕ! Контроллер регенерации памяти не может захватить шину до тех пор, пока контроллер ПДП ей владеет. Это означает, что любой цикл ПДП не должен превышать 15 мкс. В противном случае может произойти потеря информации в микросхемах динамической памяти.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Сигналы запроса и подтверждения режима ПДП заведены на все внешние платы и эти сигналы вырабатываются обычными ТТЛ выходами, поэтому все внешние платы должны использовать и анализировать различные каналы ПДП. В противном случае возможен конфликт внешних слотов между собой или с устройствами на материнской плате.

Внешние слоты могут быть или памятью прямого доступа или устройством ввода/вывода, когда они взаимодействуют с контроллером ПДП.

Внешние платы могут функционировать в 5 различных режимах: задатчика шины, памяти и устройств ввода/вывода прямого доступа, памяти и устройств ввода/вывода, регенерации памяти или сброса. Платы могут поддерживать любую комбинацию из первых четырех режимов; сигналу сброса должны подчиниться все платы одновременно.

Только 16-разрядные платы с двумя интерфейсными разъемами могут становиться задатчиками на шине. Для захвата шины внешняя плата должна разрешить сигнал -DRQ и, получив сигнал -DACK от контроллера ПДП, разрешить сигнал -MASTER. На этом процедура захвата шины заканчивается.

Внешняя плата, захватив шину, может выполнять любые циклы доступа, так же как центральный процессор. Единственное ограничение — невозможность выполнять циклы ПДП, так как все интерфейсные сигналы, управляющие работой контроллера ПДП, заведены на материнскую плату и не могут быть использованы контроллером ПДП, находящимся на внешней плате. Когда внешняя плата является задатчиком на шине, контроллер ПДП запрещает сигнал AEN и это позволяет устройствам ввода/вывода нормально дешифрировать адрес и быть доступными для внешней платы. При запрещенном сигнале AEN циклы передачи ПДП невозможны (подробнее в разделе описания сигнала AEN, в гл. 3). Кроме этого, циклы ПДП не могут быть выполнены на шине также и потому, что у контроллера ПДП канал, через который был осуществлен захват шины, занят, а другие каналы контроллера ПДП не могут быть использованы до освобождения ранее занятого, т.е. до освобождения шины захватившей ее внешней платой.

ПРИМЕЧАНИЕ: Программное обеспечение, поддерживающее работу внешней платы в качестве задатчика шины, должно обеспечивать использование каналов ПДП только в режиме каскадирования. В противном случае внешняя плата не сможет осуществить захват шины.

ПРИМЕЧАНИЕ: Внешняя плата начинает любой цикл доступа как 16-разрядная, однако если сигнал -MEM CS16 или -I/O CS16 не будет разрешен, цикл будет завершен как 8-разрядный. При этом перестановщик байтов на материнской плате будет определять, по каким линиям данных (SD или SD ) передается байт информации, исходя из анализа сигналов -SBHE и SA0.

ВНИМАНИЕ! Захватившая шину внешняя плата обязана не реже, чем через 15 мкс, вырабатывать сигнал -REFRESH для запроса контроллеру регенерации на регенерацию памяти. Контроллер регенерации при выполнении цикла регенерации памяти вырабатывает сигналы адреса, команд и анализирует сигнал I/O CH RDY, но внешняя плата, выработавшая сигнал -REFRESH, по завершении цикла регенерации снимает этот сигнал и продолжает оставаться задатчиком на шине. При необходимости выполнить несколько циклов регенерации сигнал -REFRESH может быть удержан внешней платой на все время требуемого количества циклов регенерации.

Контроллер регенерации памяти не может захватить шину сам до тех пор, пока контроллер ПДП (а именно через него внешняя плата становится задатчиком на шине) не освободит ее на время регенерации по сигналу -REFRESH.

Внешняя плата может работать в режиме ПДП только в том случае, если контроллер ПДП является задатчиком на шине. В режиме прямого доступа к памяти данные всегда передаются между устройством ввода/вывода и памятью на внешней плате. В режиме прямого доступа к устройству ввода/вывода данные передаются между памятью и устройством ввода/вывода на внешней плате. Внешняя плата, отвечающая на шине как 8- или 16-разрядное устройство, должна соответственно использовать 8- или 16- разрядные каналы контроллера ПДП. В табл. 2.2 показано состояние сигналов на шине для режима ПДП.

ВНИМАНИЕ! Следует специально обратить внимание на некоторые особенности при выполнении циклов передачи данных между 8-разрядными устройствами ввода/вывода и 16-разрядной памятью на внешней плате. Во-первых, внешняя плата должна анализировать сигналы -SBHE и SA0 для правильного определения передаваемых данных.

Во-вторых, при записи в УВВ из памяти на внешней плате перестановщик байтов на материнской плате будет определять, по какой половине шины данных (SD или SD ) следует направить байт; внешняя плата после анализа -SBHE и SA0 должна определить, по какой половине шины данных ей направить байт данных. В-третьих, при чтении УВВ в память на внешней плате перестановшик байтов направляет в память байт данных также либо по старшей половине шины данных SD , либо по младшей половине SD . Внешняя плата по сигналам -SBHE и SA0 должна определять, когда следует переводить в третье состояние свои выходы по младшей половине шины данных SD во избежание столкновений на шине.

Внешняя плата может как 16-разрядная память обмениваться в режиме ПДП как с 8-ми разрядными устройствами ввода/вывода, так и с 16-разрядными. Но, если внешняя плата является 8-разрядной памятью, то в режиме ПДП она может обмениваться данными только с 8-разрядными устройствами ввода/вывода. Другая особенность относится к тому случаю, когда контроллер ПДП выполняет запись данных в 8- разрядное устройство вывода на внешней плате из 16-разрядной памяти. Если такая внешняя плата установлена в 16-разрядный слот и может работать в 16-разрядном режиме, она должна для такого случая поддерживать старшую половину шины данных SD в третьем состоянии во избежание столкновения сигналов на шине.

ВНИМАНИЕ! Когда контроллер ПДП является задатчиком на шине, он игнорирует сигнал -0WS, поэтому если внешняя плата используется как 16-разрядная память и обмен с ней выполняется контроллером ПДП, применение быстрых микросхем памяти в такой плате лишено смысла.

Обычный доступ к внешней плате как к памяти или устройству ввода/вывода. Внешняя плата становится обычным ресурсом памяти или ввода/вывода, если задатчиком на шине является центральный процессор или другая внешняя плата.

ВНИМАНИЕ! Существуют особенности такого использования внешней платы, если она устанавливается в [8/16] слот, а участвует в обмене данными как 8-разрядная память или УВВ в течении всего цикла доступа. При чтении данных в такую внешнюю плату перестановщик байтов будет переставлять данные между шинами SD или SD для правильного приема данных внешней платой. Внешняя плата при этом должна поддерживать свои выходы SD в третьем состоянии, так как иначе неизбежно столкновение сигналов на шине данных.

ВНИМАНИЕ! Когда некоторые внешние платы становятся задатчиками на шине, они могут игнорировать сигнал I/O CH RDY или -0WS и выполнять цикл доступа как цикл обращения к 8- или 16-разрядной памяти. Но любые внешние платы обязаны возвращать задатчику на шине ISA эти сигналы при необходимости, так как если центральный процессор является задатчиком на шине, то он использует эти сигналы для определения продолжительности цикла доступа.

Все внешние платы оказываются в режиме сброса при разрешенном сигнале RESET DRV; иначе этот режим невозможен. Все выходы с тремя состояниями на плате должны быть в третьем состоянии и все выходы с открытым коллектором должны быть в состоянии логической единицы на время не менее 500 нс после разрешения сигнала RESET DRV. Все внешние платы должны завершить свою инициализацию за время не более 1 мс после разрешения сигнала RESET DRV и быть готовыми к выполнению циклов доступа на шине. Любые операции на шине возможны только после запрещения сигнала RESET DRV.

Контроллер регенерации памяти выполняет циклы чтения памяти по специальным адресам на материнской плате и внешних платах для регенерации информации в микросхемах динамической памяти. Каждые 15 мкс контроллер пытается овладеть шиной для запуска цикла регенерации. Если в этот момент задатчиком на шине является центральный процессор, то он освобождает шину для контроллера регенерации. Если в этот момент шина захвачена внешней платой, то контроллер регенерации выполнит цикл регенерации только при выработке внешней платой сигнала -REFRESH. Если в этот момент задатчиком на шине являлся контроллер ПДП, то до освобождения им шины цикл регенерации не может быть выполнен.

Когда выполняется цикл регенерации, контроллер регенерации вырабатывает сигналы адреса SA с одним из 256 возможных адресов регенерации. Другие адресные линии неопределены и могут находиться в третьем состоянии. Этот цикл может выполняться с задержкой по сигналу I/O CH RDY с разрешенными сигналами -SMEMR и -MEMR.

ВНИМАНИЕ! Циклы регенерации должны выполняться каждые 15 мкс для перебора всех 256 адресов за 4 мс. Если это условие не выполняется, данные, хранящиеся в динамической памяти, могут быть утеряны.

В данной главе рассматриваются характеристики шины, не зависящие от типа устройства, захватившего шину.

Максимальное адресное пространство при обращении к памяти, поддерживаемое шиной ISA, 16 Мб (24 линии адреса), но не все слоты поддерживают полностью это адресное пространство. Когда задатчик на шине осуществляет доступ к памяти на материнской плате или к памяти, установленной в слот, он должен разрешать сигналы -MEMR или -MEMW; аппаратно на материнской плате дополнительно разрешаются сигналы -SMEMR и -SMEMW, если требуемый адрес находится в пределах первого мегабайта адресного пространства. К 8-разрядным слотам подведены только линии -SMEMR и -SMEMR, SD и SA ; поэтому внешние платы, установленные в 8-разрядные слоты, могут быть либо только 8-разрядными устройствами ввода/вывода, либо 8-ми разрядной памятью в первом мегабайте адресного пространства. Внешние платы, устанавливаемые в 8/16-разрядные слоты, принимают все командные сигналы, адреса и данные; они могут быть как 8-, так и 16-разрядными и адресное пространство памяти на них может быть любым в пределах 16 Мб. Цикл доступа к таким внешним платам завершается как 16-разрядный, если плата разрешает сигнал -I/O CS16 или -MEM CS16.

ПРИМЕЧАНИЕ: Память на материнской плате или внешней плате считается 16- разрядным ресурсом только в том случае, если разрешается сигнал -MEM CS16. Этот сигнал вырабатывается из сигналов адреса LA ; поэтому 16-разрядная память может быть выбрана только блоками по 128 Кб; внутри такого блока память не может быть частично 8-разрядной, а частично 16-разрядной, так как невозможно по обращению к меньшему блоку однозначно выработать сигнал -MEM CS16. Разрядность внутри такого блока должна быть одинаковой при обращении по любому адресу внутри 128 Кб.

ВНИМАНИЕ! Микросхемы динамической памяти требуют циклов регенерации через каждые 15 мкс. Если циклы регенерации выполняются реже, чем через 15 мкс, то данные в памяти могут быть потеряны.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Динамическая память на материнской плате может иметь два вида своей организации — 16- или 32-разрядная. Но разрядность памяти на материнской плате принимается во внимание только центральным процессором, для внешних плат динамическая память на материнской плате всегда только 16-разрядная. ПЗУ на материнской плате, содержащее BIOS (Base Input/Output System — Базовая Система Ввода/Вывода), также всегда 16-разрядное.

Максимально адресное пространство для устройств ввода/вывода, поддерживаемое шиной ISA составляет 64 Кб (16 адресных линий). Все слоты поддерживают 16 адресных линий. Первые 256 адресов зарезервированы для устройств, расположенных, как правило, на материнской плате — регистры контроллера ПДП, контроллера прерываний, часов реального времени, таймера-счетчика и других устройств, требующихся для AT совместимости различных компьютеров.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Несмотря на то, что для выбора адреса УВВ доступны все 16 сигналов адреса, традиционно для адресов УВВ в компьютерах серии IBM PC/XT/AT использовались только первые 10 разрядов адреса. Это означает, что адреса из следующих килобайтных блоков будут декодироваться также как адреса в первом килобайте адресов УВВ. Поэтому для вновь разрабатываемых внешних плат следует использовать «окна» в существующем сейчас распределении адресов стандартных УВВ для компьютеров IBM PC/AT. Для увеличения количества используемых адресов УВВ (при необходимости) можно использовать адресное пространство выбранного окна со сдвигом на 1 Кб или кратное ему значение. Очевидно, что внешняя плата в этом случае должна декодировать более чем 10 линий адреса.

Линии запроса на прерывания непосредственно заведены на контроллеры прерываний типа Intel 8259A. Контроллер прерываний будет реагировать на запрос по такой линии в случае, если сигнал на ней перейдет из низкого уровня в высокий. Шина ISA не имеет линий, подтверждающих прием запроса на прерывание, поэтому запрашивающее прерывание устройство должно само определять по реакции ЦП подтверждение приема своего запроса.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Линии запроса на прерывания заведены на все слоты и обрабатываются контроллером прерывания по нарастающему фронту сигнала. До установки новой внешней платы, если она использует в своей работе контроллер прерываний, следует определить, есть ли свободная линия запроса на прерывание и именно ее использовать для новой внешней платы. При не соблюдении этого условия возможно возникновение конфликтных ситуаций на шине.

Центральный процессор или внешняя плата могут выполнить как 8- так и 16-разрядные циклы доступа, причем все циклы всегда начинаются как 16-разрядные, а завершаются как 8- или 16-разрядные. Цикл доступа будет завершен как 8-разрядный, если устройство, к которому осуществляется доступ, запретит сигнал -I/O CS16 или -MEM CS16.

Читайте также: Цветовая маркировка шины заземления по пуэ

Адресные сигналы этого типа поступают на шину с регистров адреса, в которых адрес «защелкивается». Сигналы SA позволяют осуществлять доступ к памяти только в младшем мегабайте адресного пространства. При доступе к устройству ввода/вывода только сигналы SA имеют действительное значение, а состояние сигналов SA не определено.

Во время выполнения циклов регенерации адреса только сигналы SA имеют действительное значение, а состояние сигналов SA неопределено и эти выводы должны быть в третьем состоянии для всех устройств на шине.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Внешняя плата, ставшая задатчиком на шине, должна разрешать сигнал -REFRESH для регенерации памяти, при этом внешняя плата должна перевести свои выходные формирователи сигналов адреса в третье состояние.

Сигналы этого типа поступают на шину без «защелкивания» в регистрах. Когда центральный процессор является задатчиком на шине, то значения сигналов на линиях LA истинны во время выработки сигнала BALE и они могут иметь произвольное значение в конце цикла доступа. Если задатчиком на шине является контроллер ПДП, сигналы LA истинны до начала сигнала -MEMR или -MEMW и сохраняются до конца цикла. При выполнении циклов доступа к памяти сигналы LA всегда истинны, а при доступе к устройствам ввода/вывода эти сигналы имеют уровень логического «0».

При выполнении циклов регенерации состояние линий LA неопределено и все ресурсы на шине должны поддерживать свои выходы по этим линиям в третьем состоянии.

РЕКОМЕНДАЦИИ: Для «защелкивания» сигналов LA следует использовать только регистры с потенциальным входом. Это вызвано тем, что в этом случае новый истинный адрес появится на выходе регистра по началу сигнала BALE (а не по его заднему фронту) и, кроме этого, во время циклов доступа к памяти каким-либо другим задатчиком, а не ЦП, сигнал BALE поддерживается в состоянии логической «1» и регистр с потенциальным входом станет просто повторителем сигналов LA (что и требуется в таком случае).

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Если внешняя плата является задатчиком на шине, то сигналы LA должны быть истинны до начала сигнала -MEMR или -MEMW и сохраняться таковыми до завершения цикла. Если внешняя плата разрешает сигнал -REFRESH (следует помнить, что внешняя плата может это сделать, только будучи задатчиком на шине), то вырабатывать сигналы адреса будет контроллер регенерации, поэтому внешней плате следует перевести свои адресные выходы в третье состояние.

Сигнал -SBHE (System Bus High Enable — Разрешение старшего байта на системной шине) разрешается центральным процессором для указания всем ресурсам на магистрали о том, что по линиям SD пересылается байт данных. Сигналы -SBHE и SA0 используются для определения того, какой байт и по какой половине шины данных пересылается (в соответствии с табл. 3.1).

Сигнал -SBHE не вырабатывается контроллером регенерации при захвате им шины, так как никаких перестановок байтов нет и нет реального чтения данных.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Если внешняя плата становится задатчиком на шине, то она должна вырабатывать сигнал -SBHE так же как центральный процессор.

Если внешняя плата, являющаяся задатчиком на шине, вырабатывает сигнал -REFRESH, то ее выход сигнала -SBHE должен быть переведен в третье состояние.

BALE [8] [8/16]

Сигнал BALE (Bus Address Latch Enable — Разрешение на «защелкивание» адреса на шине) является стробом для записи адреса по линиям LA и сообщает ресурсам на шине, что адрес является истинным и его можно «защелкнуть» в регистре. Этот сигнал также информирует ресурсы на шине о том, что сигналы SA и -SBHE истинны.

При захвате шины контроллером ПДП сигнал BALE всегда равен логической «1» (вырабатывается на материнской плате), так как сигналы LA и SA истинны до выработки командных сигналов. Если контроллер регенерации становится задатчиком на шине, то на линии BALE также поддерживается уровень логической единицы, поскольку сигналы адреса SA истинны до начала командных сигналов.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

При захвате шины внешней платой сигнал BALE поддерживается материнской платой в состоянии логической «1» на все время захвата шины. Адресные сигналы LA и SA должны быть при этом истинны в течении времени разрешения платой командных сигналов.

Если центральный процессор является задатчиком на шине и выполняет цикл доступа к ресурсу на внешней плате, то сигналы LA истинны только в течении короткого времени, поэтому сигнал BALE должен быть использован для «защелкивания» адреса в регистре. При захвате шины любым устройством, кроме ЦП, на линии BALE поддерживается уровень логической «1».

Сигнал AEN (Address Enable — Разрешение адреса) разрешается тогда, когда контроллер ПДП становится задатчиком на шине и сообщает всем ресурсам на шине о том, что на шине выполняются циклы ПДП. Разрешенный сигнал AEN также информирует все устройства ввода/вывода о том, что контроллер ПДП установил адрес памяти и УВВ следует запретить на время сигнала AEN декодирование адреса.

Этот сигнал запрещается, если задатчиком на шине является центральный процессор или контроллер регенерации.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Если внешняя плата, выполняя процедуру захвата шины, вырабатывает сигнал -MASTER, сигнал AEN запрещается контроллером ПДП для того, чтобы позволить внешней плате доступ к устройствам ввода/вывода.

SD и SD

Линии SD и SD , как правило, еще называют шиной данных, причем по линии SD15 передается старший значащий бит, а по линии SD0 — младший значащий бит. Линии SD — младшая половина шины данных, SD — старшая половина шины данных. Все 8-ми разрядные ресурсы могут обмениваться данными только по младшей половине шины данных. Поддержка обмена данными между 16-ти разрядным задатчиком на шине и 8-ми разрядным ресурсом осуществляется перестановщиком байтов на материнской плате (табл. 3.1 и рис. 3.1 иллюстрирует его работу).

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Если сигнал — REFRESH разрешен, то внешние платы должны перевести свои выходы по шине данных в третье состояние, так как нет пересылок данных во время циклов регенерации памяти.

Сигналы этой группы управляют как продолжительностью, так и типами циклов доступа, выполняемых на шине. Группа состоит из шести командных сигналов, двух сигналов готовности и трех сигналов, которые определяют размеры и тип цикла.

Командные сигналы определяют вид устройства (память или УВВ) и направление пересылки (запись или чтение).

Сигналы готовности управляют продолжительностью цикла доступа, укорачивая его или, наоборот, удлиняя.

-MEMR [8/16] и -SMEMR [8] [8/16]

Сигнал -MEMR (Memory Read — Чтение памяти) разрешается задатчиком на шине для чтения данных из памяти по адресу, определяемому сигналами по линиям LA и SA . Сигнал -SMEMR (System Memory Read — Системное чтение памяти) функционально идентичен -MEMR, за исключением того, что сигнал -SMEMR разрешается при чтении памяти, находящейся в пределах первого мегабайта адресного пространства. Сигнал -SMEMR вырабатывается на материнской плате из сигнала -MEMR и, поэтому, задерживается относительно сигнала -MEMR на 10 или менее наносекунд.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Если внешняя плата становится задатчиком на шине, то она может разрешать только сигнал -MEMR, так как сигнал -SMEMR может разрешаться только материнской платой при чтении из памяти в первом мегабайте адресного пространства. Если внешняя плата разрешает сигнал -REFRESH, то она должна перевести свой выход по сигналу -MEMR в третье состояние, так после разрешения сигнала -REFRESH контроллер регенерации будет разрешать этот сигнал.

-MEMW [8/16] и -SMEMW [8] [8/16]

Сигнал -MEMW (Memory Write — Запись в память) разрешается задатчиком на шине для записи данных в память по адресу, определяемому сигналами по линиям LA и SA . Сигнал -SMEMW (System Memory Write — Системная запись в память) функционально идентичен -MEMW, за исключением того, что сигнал -SMEMW разрешается при записи в память, находящейся в пределах первого мегабайта адресного пространства. Сигнал -SMEMW вырабатывается на материнской плате из сигнала -MEMW и, поэтому, задерживается относительно сигнала -MEMR на 10 нс или менее.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Если внешняя плата становится задатчиком на шине, то она может разрешать только сигнал -MEMW, так как сигнал -SMEMW может разрешаться только материнской платой при записи в память в первом мегабайте адресного пространства. Если внешняя плата разрешает сигнал -REFRESH, то она должна перевести свой выход по сигналу -MEMW в третье состояние.

Сигнал -I/OR (I/O Read — Чтение устройства ввода/вывода) разрешается задатчиком на шине для чтения данных из устройства ввода/вывода по адресу, определяемому сигналами SA .

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Если внешняя плата разрешает сигнал -REFRESH, то она должна перевести свой выход по сигналу -I/OR в третье состояние.

Сигнал -I/OW (I/O Write — Запись в устройства ввода/вывода) разрешается задатчиком на шине для записи данных в устройство ввода/вывода по адресу, определяемому сигналами SA .

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Если внешняя плата разрешает сигнал -REFRESH, то она должна перевести свой выход по сигналу -IOW в третье состояние.

Сигнал -MEM CS16 (Memory Cycle Select — Выбор цикла для памяти) разрешается 16-разрядной памятью для сообщения задатчику шины о том, что память, к которой он обращается, имеет 16-разрядную организацию и ему следует выполнить 16-разрядный цикл доступа. Если этот сигнал запрещен, то только 8-разрядный цикл доступа может быть выполнен на шине. Память, к которой выполняется цикл доступа, должна выработать этот сигнал из адресных сигналов LA .

ПРИМЕЧАНИЕ: Контроллер ПДП и контроллер регенерации игнорируют сигнал

-MEM CS16 при выполнении циклов ПДП и регенерации памяти.

РЕКОМЕНДАЦИИ: Декодировав сигналы LA на внешней плате 16-разрядной памяти, следует разрешить сигнал -MEM CS16, если установленный на шине адрес является адресом этой внешней платы. Так как этот сигнал фиксируется на материнской плате, как правило, по заднему фронту сигнала BALE, то схема дешифрации сигналов LA и последующего формирования -MEM CS16 должна иметь минимально возможную задержку (для компьютеров с тактовой частотой ЦП 20 МГц не более 20 нс).

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Если внешняя плата является 16-разрядной памятью, то она должна информировать об этом задатчика на шине, разрешив сигнал -MEM CS16.

Если внешняя плата, являясь задатчиком на шине, выработает сигналы адреса SA и какое-либо устройство ввода/вывода случайно при декодировании этого адреса разрешит сигнал -I/O CS16, то внешняя плата должна игнорировать его в течении цикла доступа к памяти.

Сигнал -I/O CS16 (I/O Cycle Select — Выбор цикла для УВВ) разрешается 16-разрядным УВВ для сообщения задатчику шины о том, что УВВ, к которому он обращается, имеет 16-разрядную организацию и ему следует выполнить 16-разрядный цикл доступа. Если этот сигнал запрещен, то только 8-разрядный цикл доступа к УВВ может быть выполнен на шине. УВВ, к которому выполняется цикл доступа, должна выработать этот сигнал из адресных сигналов SA .

ПРИМЕЧАНИЕ: Контроллер ПДП и контроллер регенерации игнорируют сигнал -I/O CS16 при выполнении циклов ПДП и регенерации памяти.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Если внешняя плата является 16-разрядным УВВ, то она должна информировать об этом задатчика на шине, разрешив сигнал -I/O CS16.

Если внешняя плата, являясь задатчиком на шине, выработает сигналы адреса LA и какое-либо устройство памяти случайно при декодировании этого адреса разрешит сигнал -MEM CS16, то внешняя плата должна игнорировать его в течении цикла доступа к УВВ.

I/O CH RDY [8] [8/16]

Сигнал I/O CH RDY (I/O Channel Ready — Готовность канала ввода/вывода) является асинхронным сигналом, вырабатываемый тем устройством, к которому осуществляется доступ на шине. Если этот сигнал запрещен, то цикл доступа удлиняется, так как в него будут добавлены такты ожидания на время запрещения. Когда задатчиком на шине является центральный процессор или внешняя плата, то каждый такт ожидания по длительности — половина периода частоты SYSCLK (для тактовой частоты SYSCLK=8 МГц длительность такта ожидания — 62.5 нс). Если задатчиком на шине является контроллер ПДП, то каждый такт ожидания — один период SYSCLK (для SYSCLK=8 МГц — 125 нс). При обращении к памяти на внешней плате ЦП всегда автоматически вставляет один такт ожидания (если сигнал -0WS запрещен), поэтому, если внешней плате достаточно времени цикла с одним тактом ожидания, то запрещать сигнал I/O CH RDY не требуется.

ПРИМЕЧАНИЕ: При выполнении циклов ПДП устройства ввода/вывода не должны вырабатывать этот сигнал, так как УВВ разрешает сигнал DRQ только после того, как истинные данные могут быть приняты или посланы УВВ и необходимости в дополнительном управлении длительностью цикла по сигналу I/O CH RDY нет. Только устройства памяти во время циклов ПДП могут разрешать этот сигнал.

ВНИМАНИЕ: Сигнал I/O CH RDY не может быть запрещен на время больше чем 15 мкс, так как при нарушении этого требования возможна потеря данных в микросхемах динамической памяти.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Если внешняя плата является задатчиком на шине, то она должна принимать и анализировать сигнал I/O CH RDY при выполнении ей циклов доступа к другим ресурсам. При работе внешней платы в других режимах она должна разрешать этот сигнал в том случае, когда она готова завершить цикл.

ВНИМАНИЕ! К сожалению, некоторые внешние платы, став задатчиком на шине, игнорируют сигнал I/O CH RDY и выполняют все циклы доступа как обычные циклы доступа к 8- или 16-разрядной памяти. Поэтому, устанавливая в компьютер внешнюю плату, которая требует удлинения цикла доступа по сигналу I/O CH RDY, следует обязательно убедиться в отсутствии в компьютере такой некорректно разработанной внешней платы.

Сигнал -0WS (0 Wait States — 0 тактов ожидания) является единственным на всей шине сигналом, который требует при приеме его задатчиком на шине синхронизации с частотой SYSCLK. Он разрешается ресурсом, к которому осуществляется доступ центральным процессором или внешней платой, и информирует задатчика на шине о том, что цикл доступа должен быть завершен без вставки такта ожидания.

ПРИМЕЧАНИЕ: Несмотря на то, что этот сигнал присоединен к слоту для 8-разрядных плат, он не может быть использован 8-разрядным ресурсом. Он может быть использован только при доступе к 16-разрядной памяти, установленной в [8/16] слот, когда центральный процессор или внешняя плата являются задатчиком на шине. Этот сигнал игнорируется при доступе к УВВ или когда контроллер ПДП или контроллер регенерации являются задатчиком на шине.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Если внешняя плата является задатчиком на шине, то она должна принимать сигнал -0WS от ресурсов, к которым она осуществляет доступ и выполнять циклы доступа с такими ресурсами без дополнительных тактов ожидания. Когда внешняя плата является 16-разрядной памятью, то она должна разрешать сигнал -0WS, если быстродействие этой памяти позволяет выполнять циклы доступа к ней без вставки дополнительного такта ожидания.

ВНИМАНИЕ! К сожалению, некоторые внешние платы, став задатчиком на шине, игнорируют сигнал -0WS и выполняют все циклы доступа как обычные циклы доступа к 8- или 16-разрядной памяти.

-REFRESH [8] [8/16]

Сигнал -REFRESH (Refresh — регенерация) разрешается контроллером регенерации для информирования всех устройств на шине о том, что выполняются циклы регенерации памяти.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Если внешняя плата является задатчиком на шине, то она должна разрешать сигнал -REFRESH для запроса на регенерацию памяти. При этом цикл регенерации будет выполнен даже несмотря на то, что контроллер регенерации не является задатчиком на шине.

Группа центральных сигналов управления состоит из сигналов различных частот, сигналов управления и ошибок.

Сигнал -MASTER (Master — Ведущий) должен вырабатываться только той внешней платой, которая желает стать задатчиком на шине.

ВНИМАНИЕ! Если сигнал -MASTER разрешен на время более 15 мкс, то внешняя плата должна запросить цикл регенерации памяти, разрешив сигнал -REFRESH.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Сигнал -MASTER разрешается внешней платой, становящейся задатчиком на шине, только после приема ей соответствующего сигнала -DACK от контроллера ПДП. После того, как сигнал -MASTER будет разрешен, внешняя плата должна ждать минимум один период частоты SYSCLK, прежде чем начать выработку сигналов адреса и данных и минимум два периода SYSCLK до выработки командных сигналов.

-I/O CH CK [8] [8/16]

Сигнал -I/O CH CK (I/O Channel Check — Проверка Канала Ввода/вывода) может быть разрешен любым ресурсом на шине как сообщение о фатальной ошибке, которая не может быть исправлена. Типичный пример такой ошибки — ошибка четности при доступе к памяти. Сигнал — I/O CH CK должен быть разрешен на время не менее 15 нс. Если в момент выработки этого сигнала задатчиком на шине являлся контроллер ПДП или контроллер регенерации, то сигнал -I/O CH CK будет записан в регистр на материнской плате, а обработан только после того, как центральный процессор станет задатчиком на шине.

Читайте также: Hyundai solaris 2014 can шина

Этот сигнал, как правило, соединен со входом немаскированного прерывания ЦП и его выработка приводит к прекращению нормальной работы компьютера.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Если сигнал -I/O CH CK разрешается в тот момент, когда задатчиком на шине является внешняя плата, то он записывается в регистр на материнской плате и будет обработан только после захвата шины центральным процессором.

RESET DRV [8] [8/16]

Сигнал RESET DRV (Reset Driver — Сброс Устройства) вырабатывается центральным процессором для начальной установки всех ресурсов доступа на шине после включения питания или падения его напряжения. Минимальное время разрешения этого сигнала — 1 мс.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Внешние платы на все время выработки этого сигнала должны перевести свои выходы в третье состояние.

SYSCLK [8] [8/16]

Сигнал SYSCLK (System Clock — системная частота) в данной книге принимается равной 8 МГц, хотя, как правило, эта частота такая же, как и тактовая частота центрального процессора на материнской плате, но с 50% (по длительности) уровнем логической «1». Все циклы шины пропорциональны SYSCLK, но все сигналы на шине, за исключением -0WS, не синхронизированы с SYSCLK.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Когда внешняя плата является задатчиком на шине, она может использовать SYSCLK для задания длины цикла, но кроме как для выработки -0WS любой сигнал для синхронизации может быть использован.

Сигнал OSC вырабатывается материнской платой всегда фиксированной частотой 14.3818 МГц с 45-55% (по длительности) уровнем логической «1». Сигнал OSC не синхронизирован ни с SYSCLK ни с каким-либо другим сигналом на шине и поэтому не может быть использован для применений, требующих синхронизации с другими сигналами. Исторически этот сигнал появился для поддержки первых контроллеров цветных мониторов для персональных компьютеров серии IBM PC. Этот сигнал удобен для использования внешними платами, поскольку он одинаков для всех моделей компьютеров, совместимых с IBM PC/AT.

Группа сигналов прерывания используется для запроса на прерывание центрального процессора.

ПРИМЕЧАНИЕ: Обычно сигналы запроса на прерывания присоединены к контроллеру прерываний типа Intel 8259A. Несмотря на то, что доступ к контроллерам прерываний (как к УВВ) имеет любой задатчик на шине, для совместимости программного обеспечения только центральный процессор может обслуживать контроллер прерываний.

IRQ [8/16] IRQ [8]

Прерывание может быть запрошено ресурсами как на материнской плате, так и на внешних платах разрешением соответствующего сигнала IRQ. Сигнал должен оставаться разрешенным до подтверждения прерывания центральным процессором, которое, как правило, заключается в доступе ЦП к ресурсу, запросившему прерывание.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Запрос на прерывание записывается в триггер в контроллере прерываний по нарастающему фронту сигнала запроса на прерывание и должен вырабатываться микросхемами с обычными ТТЛ выходами. Поэтому, выбирая линию запроса на прерывание для своей внешней платы, следует убедиться, что эта линия не занята какой-либо другой внешней платой.

Эти сигналы поддерживают циклы пересылки данных при прямом доступе в память.

ПРИМЕЧАНИЕ: Каналы ПДП поддерживают только пересылки 8-разрядных данных. Каналы ПДП поддерживают пересылки только 16-разрядных данных.

DRQ [8] [8/16] DRQ [8]

Сигналы DRQ (DMA Request — запрос на ПДП) разрешаются ресурсами на материнской плате или внешними платами для запроса на обслуживание контроллером ПДП или для захвата шины. Сигнал DRQ должен быть разрешен до тех пор, пока контроллер ПДП не разрешит соответствующий сигнал -DACK.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Сигналы DRQ вырабатываются с выходов обычных ТТЛ микросхем, поэтому при установке внешней платы в слот шины ISA следует правильно выбрать канал ПДП, который не должен быть занят другими внешними платами.

-DACK [8] [8/16] -DACK [8]

Сигналы -DACK (DMA Acknowledge — подтверждение ПДП) разрешаются контроллером ПДП как подтверждение сигналов запросов DRQ . Разрешение соответствующего сигнала -DACK означает, что либо циклы ПДП будут начаты, либо внешняя плата захватила шину.

Сигнал T/C (Terminal Count — Окончание счета) разрешается контроллером ПДП тогда, когда по какому-либо из каналов ПДП будет окончен счет числа пересылок данных, то есть все пересылки данных выполнены.

Для питания внешних плат на шине ISA используются 5 напряжений питания постоянного тока: +5 В, -5 В, +12 В, -12 В, 0 В (корпус — Ground). Все линии питания заведены на 8-разрядный разъем, кроме одной линии по +5 В и одной линии корпуса на дополнительном разъеме.

Максимально допустимые токи потребления для внешней платы по каждому напряжению питания приведены в табл. 4.1.

Таблица 4.1. Максимальные токи потребления внешней платой

ВНИМАНИЕ! Данные, приведенные в табл. 4.1, не означают, что каждая из установленных в слоты внешних плат может потреблять такие токи. Таблица информирует только о том, какие токи разрешается пропускать через разъем (разъемы) внешней платы. Общие допустимые токи потребления для всех внешних плат как правило, ограничиваются источником питания компьютера. Поэтому, до установки новой внешней платы в слот шины следует определить наличие соответствующего резерва по токам потребления для этой платы у источника питания компьютера.

Циклы шины ISA всегда асинхронны по отношению к SYSCLK. Различные сигналы разрешаются и запрещаются в любое время; внутри допустимых интервалов сигналы отклика могут также быть выработаны в любое время. Исключением является только сигнал -0WS, который должен быть синхронизирован с SYSCLK.

На шине существуют 4 индивидуальных типа циклов: Доступ к Ресурсу, ПДП, Регенерация, Захват Шины. Цикл Доступа к Ресурсу выполняется, если центральный процессор или внешняя плата в качестве задатчиков обмениваются данными с различными ресурсами на шине. Цикл ПДП выполняется, если контроллер ПДП является задатчиком на шине и выполняет циклы передачи данных между памятью и УВВ. Цикл Регенерации выполняется только контроллером регенерации для регенерации микросхем динамической памяти. Цикл Захвата Шины выполняется внешней платой для того, чтобы стать задатчиком на шине.

Структурно циклы отличаются по типу задатчика на шине и видами ресурсов доступа на ней. Внутри типа цикла существуют различные виды его, обусловленные различной продолжительностью каждого вида.

Существуют три типа цикла Доступа к Ресурсу:

- цикл с 0 тактов ожидания — этот цикл наиболее короткий из всех возможных;

- нормальный цикл — при выполнении такого цикла ресурс доступа не запрещает сигнал готовности I/O CH RDY — далее цикл такого вида будет называться просто нормальным;

- удлиненный цикл — при выполнении такого цикла ресурс доступа запрещает сигнал готовности I/O CH RDY на время, необходимое ресурсу для приема или передачи данных — далее цикл такого вида будет называться удлиненным.

В циклах ПДП и Регенерация тоже существуют два вида: нормальный и удлиненный, исходя из таких же, описанных выше условий.Ниже все типы циклов будут подробно описаны и, кроме этого, в гл. 6 приведены временные диаграммы всех типов циклов.

Центральный процессор начинает цикл Доступа к Ресурсу выработкой сигнала BALE, сообщающего всем ресурсам об истинности адреса на линиях SA , а также для фиксации ресурсами адреса по линиям LA . Ресурсы должны сообщать ЦП разрешением сигнала -MEM CS16 или -I/O CS16 о том, что цикл должен быть 16- разрядным; иначе цикл будет завершен как 8-разрядный. ЦП также вырабатывает команды -MEMR, -MEMW, -IORC и -IOWC определяющие тип ресурса (память или УВВ), а также направление передачи данных. Если доступ к памяти в первом мегабайте адресного пространства, то также будет разрешаться сигнал -SMEMR или -SMEMW. Ресурс доступа, которому необходимо изменить время цикла, должен отвечать сигналом -0WS или I/O CH RDY для информирования ЦП о продолжительности цикла доступа.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Внешняя плата, захватившая шину, также начинает цикл доступа с выработки адресных сигналов, но, в отличии от ЦП, не подтверждает адрес сигналом BALE. На линии этого сигнала поддерживается материнской платой на все время захвата шины внешней платой уровень логической «1». Поэтому внешняя плата должна выработать истинные сигналы как по линиям SA так и по линиям LA до начала разрешения командных сигналов, сохраняя адрес до конца цикла. Внешняя плата также должна иметь возможность анализа сигналов -MEM CS16 и -I/O CS16 и в соответствии с этими сигналами завершать цикл как 16- или 8-разрядный.

Цикл доступа с 0 тактов ожидания — наиболее короткий цикл из всех возможных на шине. Этот цикл может быть выполнен только при доступе ЦП или внешней платы (когда она задатчик на шине) к 16-разрядной памяти. В начале цикла задатчик должен установить адрес на линиях LA для выбора блока памяти в 128 Кб. Если затем не будет разрешен сигнал -MEM CS16, то цикл будет завершен как 8-разрядный (нормальный или удлиненный) и цикл с 0 тактов ожидания не будет выполнен. Если ресурсом будет разрешен сигнал -MEM CS16, то затем он должен разрешить сигнал -0WS в соответствующее время после выдачи командного сигнала -MEMR или -MEMW для завершения цикла с 0 тактов ожидания. При запрещении сигнала -0WS цикл завершается как нормальный или удлиненный.

ПРИМЕЧАНИЯ: Если сигнал -0WS разрешается ресурсом доступа, то задатчик не требует разрешения сигнала I/O CH RDY — он игнорируется. Только сигнал -0WS является на шине ISA синхронным по отношению к SYSCLK сигналом.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Внешняя плата, захватившая шину, выполняет цикл доступа с 0 тактов ожидания точно также как центральный процессор.

Нормальный цикл может быть выполнен ЦП или внешней платой (если она владеет шиной) при доступе к 8- или 16-разрядному УВВ или к памяти. После выдачи на шину сигналов адреса задатчик разрешает командные сигналы -MEMR, -MEMW, -I/OR или -I/OW. В ответ ресурс должен разрешить сигнал I/O CH RDY в соответствующее время, так как иначе цикл будет завершен как удлиненный. Разрешение I/O CH RDY заставляет задатчика завершить цикл за фиксированный период времени (этот период кратен периоду SYSCLK, но не синхронизирован с ним). Длительность нормального цикла определяется временем разрешения сигналов -MEMR, -MEMW, -I/OR или -I/OW которое, в свою очередь, зависит от размера данных и адреса ресурса доступа.

Удлиненный цикл может быть выполнен ЦП или внешней платой (если она владеет шиной) при доступе к 8- или 16-разрядному УВВ или к памяти. Задатчик на шине выполняет удлиненный цикл в том случае, если ресурс, к которому осуществляется доступ, не разрешает в соответствующее время после разрешения командного сигнала сигнал I/O CH RDY. Задатчик продолжает разрешать командный сигнал до тех пор, пока ресурс не разрешит сигнал I/O CH RDY. Период времени удлиненного цикла также кратен SYSCLK, но не синхронизирован с ним.

Контроллер регенерации пытается захватить шину по истечении 15 мкс с последнего цикла регенерации двумя способами:

- если шиной владеет центральный процессор, то он по завершении выполнения текущей команды передает шину контроллеру регенерации;

- если шиной владеет контроллер ПДП, то шина будет передана контроллеру регенерации только по завершении циклов пересылки данных контроллером ПДП.

Назначение следующих сигналов во время цикла регенерации имеют оригинальную интерпретацию:

-REFRESH — разрешение этого сигнала сообщает о начале цикла регенерации;

Адрес — контроллер регенерации вырабатывает только сигналы по линиям адреса SA , остальные сигналы адреса не определены;

-MEMR — сигнал -MEMR разрешается контроллером регенерации, при этом сигнал -SMEMR будет разрешен материнской платой;

SD — линии данных игнорируются контроллером регенерации и все ресурсы на шине обязаны перевести свои выходы по линиям данных в третье состояние;

— эти сигналы игнорируются контроллером регенерации:

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Когда внешняя плата является задатчиком на шине, она должна самостоятельно разрешать сигнал -REFRESH для запуска цикла регенерации памяти.

Нормальный цикл регенерации контроллер регенерации начинает с разрешения сигнала -MEMR, в ответ ресурс должен разрешить сигнал I/O CH RDY в соответствующее время, так как иначе цикл будет завершен как удлиненный. Длину цикла фактически определяет только продолжительность сигнала -MEMR.

Удлиненный цикл контроллер регенерации выполняет в том случае, если хотя бы один ресурс доступа не разрешает сигнал I/O CH RDY в соответствующее время после разрешения сигнала -MEMR. Контроллер регенерации продолжает разрешать сигнал -MEMR до того, как сигнал I/O CH RDY будет разрешен всеми ресурсами на шине. Период времени удлиненного цикла также кратен SYSCLK, но не синхронизирован с ним.

Цикл ПДП подобен циклу доступа, который выполняет другой владелец шины. Циклы ПДП запускаются после разрешения сигнала -DACK контроллером ПДП. Размер передаваемых данных зависит от используемого канала ПДП: каналы с 0 по 3 определены для 8-разрядных пересылок данных, а каналы с 5 по 7 для 16-разрядных пересылок данных. Сигналы -MEM CS16 и -I/O CS16 игнорируются самим контроллером ПДП, но эти сигналы использует перестановщик байтов на материнской плате.

Циклы ПДП выполняются только между памятью и устройствами ввода/вывода. Сигналы адреса, вырабатываемые контроллером ПДП, содержат только адрес памяти и не содержат адрес УВВ. Процесс пересылки данных в цикле ПДП выполняется так: источник данных выставляет данные на шине, а приемник данных должен быть готов их принять в это же самое время. Команды записи и чтения также разрешаются одновременно для правильного выбора направления пересылки. При этом сигнал чтения обязательно разрешается раньше, чем сигнал записи во избежание столкновения между буферами данных в двух ресурсах.

УВВ, запрашивающее режим ПДП на шине, разрешает сигнал DRQ соответствующего канала. Если задатчиком на шине является центральный процессор, то он освобождает шину контроллеру ПДП, который, в свою очередь, извещает УВВ разрешением сигнала -DACK о том, что начинается цикл ПДП. Так как контроллер ПДП вырабатывает только адрес памяти, УВВ должно использовать сигналы -I/OR, -I/OW и -DACK для приема или передачи данных в режиме ПДП.

Цикл ПДП начинается с разрешения сигнала -DACK соответствующего канала, а также сигнала AEN. Разрешением сигнала AEN контроллер ПДП извещает все ресурсы на шине о том, что адреса и командные сигналы вырабатываются контроллером ПДП, а не центральным процессором, контроллером регенерации или внешней платой. После разрешения командных сигналов контроллер ПДП анализирует сигнал I/O CH RDY для определения длительности цикла.

Если цикл удлиняется, то период удлинения кратен удвоенному периоду SYSCLK, хотя и не синхронизирован с SYSCLK.

ПРИМЕЧАНИЕ: Данные, которые записываются в память или УВВ, должны быть истинны до разрешения команды записи и оставаться истинными до запрещения команды записи.

Нормальный цикл выполняется контроллером ПДП для 8- или 16-разрядных пересылок данных. Контроллер ПДП разрешает сигналы -MEMR, -MEMW, -I/OR и -I/OW, а память, с которой выполняется обмен, должна разрешить сигнал I/O CH RDY в соответствующее время, иначе цикл будет завершен как удлиненный. Разрешение сигнала I/O CH RDY заставляет контроллер завершить цикл за фиксированный период времени; этот период кратен периоду SYSCLK, но не синхронизирован с ним.

Продолжительность разрешения сигналов -MEMR, -MEMW, -I/OR и -I/OW определяет продолжительность всего цикла, причем эта продолжительность зависит от размера данных для различных адресных пространств.

Удлиненный цикл ПДП выполняется контроллером ПДП также как и нормальный цикл, за исключением того, что при удлиненном цикле сигнал I/O CH RDY не разрешается в соответствующее время после того, как командный сигнал будет разрешен. Контроллер ПДП продолжает разрешать командные сигналы до тех пор, пока УВВ не разрешит сигнал I/O CH RDY. Период времени, на который удлиняется цикл, в этом случае кратен удвоенному периоду SYSCLK, хотя и не синхронен с SYSCLK.

ПРИМЕЧАНИЕ: Сигналы адреса LA во время обычного цикла доступа должны записываться в регистр ресурсами доступа для запоминания адреса в течении всего цикла. В отличие от обычных циклов, при выполнении циклов ПДП эти адресные сигналы истинны в течении всего цикла ПДП.

ВНИМАНИЕ! Каналы ПДП, которые используются внешними платами для захвата шины, должны быть запрограммированы в каскадном режиме.

Любая внешняя плата, установленная в [8/16] слот, может стать задатчиком на шине ISA. Захват шины внешняя плата должна начать с разрешения сигнала DRQ канала ПДП, предварительно запрограммированного в каскадный режим. Канал ПДП, запрограммированный в каскадном режиме, считает, что все циклы ПДП были выполнены внешним ресурсом — в данном случае внешней платой. Контроллер ПДП отвечает внешней плате разрешением сигнала -DACK; внешняя плата в ответ на -DACK разрешает сигнал -MASTER. После разрешения сигнала -MASTER внешняя плата должна ждать некоторое время, после чего может начинать свои циклы доступа.

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле