Рис. 1.1. Два примера физической реализации шины системы.

о — шина специального исполнения, состоящая нз гибких проводов; б -шина, выпол-. ненная в виде печатной схемы.

рамках системыНапример, некоторая группа линий может использоваться для передачи сигналов адреса памяти. Эту группу линий можно назвать адресной шиной. На рис. 1.1 показаны два примера различной физической реализации шин. Все три шины являются специализированными с точки зрения их функций. Эти шины именуются так:

3. Шина управления системы.

Логическое состояние этих трех шин описывает коммуникационный тракт системы в любой момент времени. Коммуникационный тракт-это путь, который данные, представленные в виде электрических сигналов, проходят в системе от одной точки к другой.

По адресной шине системы передаются лишь выходные сигналы, которые поступают с выводов в корпусе микропроцессора. Эта шина предназначена для того, чтобы открывать или выби-

Ваедение в архитектуру с 3 шинами

рать Правильный тракт для электрического соединения в пределах микропроцессорной системы.

Для удобства будем в дальнейшем полагать, что все электрические соединения в микропроцессорной системе осуществляются между микропроцессором и устройством, открытым с помощью адресной шины. В качестве устройства здесь выступает любая электрическая схема, принимающая данные от микропроцессора либо вырабатывающая данные для него. (Позднее-мы покажем, что это не всегда справедливо для систем, управляемых, микропроцессором.) Для начинающих изучение микропроцессорных систем подобное ограничение способствует лучшему пониманию материала. После того как понятие описываемого здесь коммуникационного тракта дано, легче объяснить особенности других коммуникационных трактов, имеющихся в микропроцессорной системе.

Другой важной характеристикой адресной шины системы является ее емкость. Емкость шины определяется числом входящих в нее отдельных электрических линий. Для микропроцессоров 8080, 8085, Z80, 6800 характерна 16-разрядная адресная шина. Это означает, что адресная шина систем, построетных на базе этих микропроцессоров, компонуется из 16 физических линий.

Шина данных системы является двунаправленной шиной. Это означает, что передача данных может производиться в обоих направлениях. В некоторых случаях данные генерируются микропроцессором и передаются от него к определенному устройству системы. Это устройство открывается с помощью заданного логического состояния линий адресной шины и пол уча et данные с шины данных.

В других случаях данные генерируются каким-то источником и передаются микропроцессору посредством шины данных. В качестве источника выступает то устройство системы, которое открывается с помощью адресной шины. Подобный режим Называется вводом данных в микропроцессор.

Хотя передача данных по шине данных может производиться в обоих направлениях, однако в каждый -заданный момент—времени она осуществляется лишь в одном направлении. Это означает что для передачи данных в систему и их приема из системы микропроцессор переводится в соответствующий режим. Более того, по всем разрядам шины в каждый момент времени данные передаются лишь в одном направлении, т. е. в любой момент по всем линиям шины они могут Либо только, вводиться либо только выводиться.

Для микропроцесебров 8080, 8085, Z80 И 6800 шина данных является 8-разрядной. Поэтому говорят, что емкость гййны дан-

ных равна 8 разрядам и параллельно могут передаваться лишь 8 бит информации. По этой, причине перечисленные микропроцессоры относят к классу 8-разрядных микропроцессоров.

На шине управления действует 4 следующих типа сигналов:

1. Чтение из памяти активизировано.

2. Запись в память активизирована.

3. Чтение с устройства ввода активизировано.

4. Запись на устройство ввода активизирована.

4 линии шины управления: ЧТЕНИЕ ИЗ ПАМЯТИ.

N ЗАПИСЬ В ПАМЯТЬ, Т/ ЧТЕНИЕ С УСТРОЙСТВА

ВВОДА, ЗАПИСЬ НА УСТРОЙСТВО ВЫВОДА

Рис. 1.2. Блок-схема системы с 3 шинами. По адресной шине и шине управ-, ления сигналы передаются лншь в оДном направлении (однонаправленные шнны). Шнна данных является двунаправленной, что показано стрелкой, имеющей два направления.

Читайте также: Шины ока кама 204

Позднее для этой шины мы введем некоторые добавочные сигналы. Однако для понимания существа процессов пока необходимо ограничиться указанным списком. сигналов. После того как станут ясны функции этих четырех сигналов, будет легче изучать функции других сигналов.

Шина управления используется лишь для вывода сигналов, т. е. является однонаправленной и работает лишь в режиме вывода. Напротив, шину данных мы рассматриваем как двунаправленную.

Термин активизирован означает, что при наступлении события, запрашиваемого соответствующей линией щнны управления, эта линия имеет активный сигнал логического уровня 1 или 0. В микропроцессорных системах активное состояние линий шины управления может быть либо логической 1, либо ло-

Вееденив в архитектуру с 3 шинами

гическим 0. При этом различные линии с5йстемы могут быть активными при разных уровнях логического сигнала. Например, линия управления ЧТЕНИЕ ИЗ ПАМЯТИ может быть активной при логическом уровне 1, а линия управления ЗАПИСЬ В ПАМЯТЬ — при уровне 0.

Распознавание и инициирование типа электрического соединения для шины данных системы является, функцией сигнала шины управления. Необходимо заметить, чтб линия управления может быть активизированной и при уровне логической 1, и при уровне логического 0.

На рис. 1.2 архитектура систем с тремя шинами показана в виде блок-схемы, из которой видно, что стрелки, соответствующие адресной шине и шине управления, указывают лишь на одно направление. Это говорит о том;, что эти шины однонаправленные. Для шины данных на рис. 1.2 стрелки указывают на два направления, что соответствует двунаправленной шине. Принятые нами обозначения часто используются в литературе для описания этих шин.

1.5. Использование архитектуры с 3 шинами

Теперь мы обсудим общие принципы передачи информации в микропроцессорной системе, имеющей архитектуру с 3 шинами. Прежде всего необходимо пояснить основные функции, реализуемые микропроцессорной системой. После этого можно будет перейти к рассмотрению особенностей их выполнения.

Для первоначального знакомства с микропроцессорами достаточно рассмотреть лишь пять функций, описанных ниже; позднее список этих функций может быть расширен. Такие функции хорошо отображают возможные операции, выполняемые в микропроцессорной системе. К ним относятся:

1. Запись данных в память системы.

2. Чтение данных из памяти системы.

3. Запись данных в устройство ввода-вывода.

4. Чтение данных с устройства ввода-вывода.

5. Выполнение операций с содержимым внутренних регистров микропроцессора.

Указанные пять возможных типов функций микропроцессорной системы позволяют создавать большое число разнообразных средств. Рассмотрим, каким образом эти функции могут быть реализованы посредством архитектуры систем с 3 шинами.

Чтобы понять, каким образом в микропроцессорной системе осуществляется запись данных в память, необходимо выяснить осот бенности передачи данных в память от любого внешнего источ-

Видео:МПСЗ .Микропроцессорная система зажигания на классику.Microprocessor system of ignition.Скачать

2 Микропроцессоры

Видео:Системная шина процессораСкачать

2.1 Архитектура с тремя шинами

Архитектура с тремя шинами является наиболее общей для микропроцессорных систем. Шиной системы называют физическую группу линий передачи сигналов, имеющих схожие функции в рамках системы. Все три шины являются специализированными с точки зрения их функций. Эти шины именуются так:

По адресной шине передаются лишь выходные сигналы микропроцессора, т. е. от микропроцессора к внешнему устройству. Эта шина предназначена для того, чтобы открывать или выбирать правильный тракт для электрического соединения в пределах микропроцессорной системы.

Для удобства будем в дальнейшем полагать, что все электрические соединения в микропроцессорной системе осуществляются между микропроцессором и устройством, открытым (выбранным) с помощью адресной шины. В качестве устройства здесь выступает любая электрическая схема, принимающая данные от микропроцессора либо вырабатывающая данные для него.

Важнейшей характеристикой адресной шины является ее емкость. Емкость шины определяется числом входящих в нее отдельных электрических линий. К примеру, 16-разрядная адресная шина представляет собой 16 независимых физических линий для передачи электрических сигналов.

Шина данных является двунаправленной шиной. Это означает, что передача данных может производиться в обоих направлениях. В первом случае, данные передаются от микропроцессора во внешнее устройство (выбранное адресной шиной ). Этот режим называется выводом данных. Во втором случае, данные передаются от внешнего устройства (выбранного шиной адреса) в микропроцессор. Этот режим называется вводом данных.

Читайте также: Гальваническая развязка шины i2c

Хотя передача данных по шине данных может производиться в обоих направлениях, однако в каждый заданный момент времени она осуществляется лишь в одном из двух направлений. Это означает, что для передачи данных в устройство (систему) и их приема из системы микропроцессор переводится в соответствующий режим. Также как и адресная шина, шина данных обладает определенной емкостью (разрядностью). По емкости шины данных судят о классе микропроцессора. К примеру, при 8-разрядной шине данных микропроцессор будет отнесен к классу 8-разрядных микропроцессоров.

На шине управления действует несколько типов сигналов. Основные из них:

а) чтение данных из памяти;

в) чтение данных с устройства ввода-вывода;

г) запись данных в устройство ввода-вывода.

Позднее для этой шины мы введем некоторые добавочные сигналы. Однако для понимания существа процессов пока достаточно ограничиться указанным списком сигналов. Шина управления используется лишь для вывода сигналов, т. е. является однонаправленной.

Видео:Лекция 4: Типы микропроцессорных системСкачать

3 Архитектура 8-разрядного однокристального

микропроцессора серии К580

Видео:МПСЗ по "БОМЖУ")). #Неидеальнаякопейка.Скачать

3.1 Общая характеристика однокристального мп

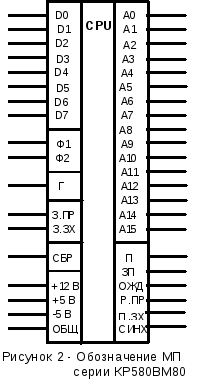

Микропроцессор КР580ИК80А является программируемой универсальной БИС, может считывать информацию из внешних устройств, памяти и производить над ней арифметические и логические операции, анализировать результаты вычислений и записывать данные в память и внешние устройства, функционируя при этом под управлением команд из некоторого фиксированного множества.

Микропроцессорная БИС КР580ИК80 представляет собой однокристальный 8-разрядный МП с двумя магистралями: однонаправленной 16-разрядной адресной магистралью (МА), двунаправленной 8-разрядной магистралью данных (МД) и 12 сигналами управления (шесть входных и шесть выходных).

Таблица 1 — Технические характеристики БИС КР580ИК80

Условное обозначение МП БИС К580ИК80 приведено на рисунке 2.

Функциональное назначение внешних

Адресная шина (А0-А15), обеспечи-

вающая адресацию к любой из 2 16

8-разрядной ячейке памяти или внеш-

Двунаправленная шина данных

(Д0-Д7), используемая для обмена

информации с памятью или ВУ;

СИНХР (SYNC) — на этом выходе МП

БИС фпрмируется сигнал СИНХР в

начале каждого машинного цикла;

П (DBIN,прием) — сигнал ПРИЕМ

на этом выходе указывает на готов-

ность МП БИС к приему данных;

ОЖД (WAIT,ожидание) — сигнал ОЖД

на этом выходе указывает что МП

находится в состоянии ожидания;

ЗП (WR)- на этом выходе МП БИС

сигнал ЗП указывает, что данные

выданы МП БИС и установлены на

МД (магистраль данных) и могут быть

П.ЗХ (HLDA, подтверждение захвата) — на этом выходе МП БИС сигнал П.ЗХ появляется в ответ на сигнал З.ЗХ (запрос захвата) и указывает, что МД и МА находятся в состоянии высокого сопротивления;

Р.ПР (INTE, разрешение прерывания) — на этом выходе сигнал Р.ПР указывает на состояние внутреннего триггера разрешения прерывания МП БИС. Состояние триггера может быть установлено программно с помощью команд EI,DI. При уровне “0” на выходе Р.ПР прием запросов прерывания МП БИС невозможен.

Г (READY, готов) — сигнал ГОТОВ на этом входе информирует о готовности ВУ к обмену информацией с МП БИС . При уровне “0” МП БИС будет находиться в состоянии ОЖИДАНИЕ.

З.ЗХ (HOLT, запрос захвата) — вход, используемый для подачи сигнала З.ЗХ на переход МП БИС в состояние ЗАХВАТ, в котором МА и МД переходят в третье состояние (высокое сопротивление). Обычно состояние используется для организации обмена информацией по каналу прямого доступа к памяти;

З.ПР (INT, запрос прерывания) — вход, используемый для подачи сигнала З.ПР. Сигнал поступает от внешнего источника на прерывание выполнения основной программы и переход на выполнение подпрограмм обслуживания прерывания. Сигнал запроса прерывания не воспринимается МП БИС при работе его в режимах ЗАХВАТ, ОЖИДАНИЕ или нулевом состоянии внутреннего тригера разрешения прерывания;

R (RESET)- вход, по которому поступает сигнал на начальную установку МП БИС, при этом обнуляется его программный счетчик, внутренние триггеры, формирующие сигналы Р.ПР и П.ЗХ;

Читайте также: H81m p33 msi разгон по шине

CLK1,2 — входы для подачи тактовых сигналов Ф1(СДК1) и Ф2(СДК2). Эти сигналы являются не пересекающимися во времени сигналами, определяющими тактовую частоту работы МП БИС.

Видео:Трехшинная архитектура ЭВМСкачать

МИКРОПРОЦЕССОРНАЯ СИСТЕМА С ТРЕМЯ ШИНАМИ

Работой всех устройств подключаемых к процессорному блоку управляет дешифратор DC, к входам которого подводятся линии шины адреса. Обычно дешифраторов бывает несколько. Если используется не все адресное пространство для памяти и ВУ, то на дешифратор заводятся не все линии адреса, чаще всего несколько старших разрядов ША. Например, если на DC завести 4 линии A19..A16, то все адресное пространство будет разбито на неперекрывающиеся блоки по 2^20 / 2^4 = 64Кб, принадлежащие каждому из 16-ти (2^4 = 16) устройств ЗУ или ВУ, подключенных к шинам (на рис.4 показаны 7 устройств). Часть из них могут использовать все отводимое им адресное пространство, например ПЗУ и ОЗУ, другие только несколько адресов.

Типовая МПС, показанная на схеме содержит:

микросхему программируемого периферийного интерфейса ППИ (PPI или IOP), к которой через три 8-битовых независимых канала PA,PB и PC можно подключать периферийные устройства, например принтер, клавиатуру, 8-ми сегментный дисплей или ЦАП и АЦП. Через ППИ может производиться обмен данными с другими МПС или ЭВМ.

Ввод с клавиатуры и вывод на дисплей могут производиться специальными микросхемами.

Связь с удаленными устройствами или абонентами сетей может осуществляться с помощьюуниверсального асинхронного последовательного приемо-передатчика УАПП-UART (программируемый связной интерфейс ПСИ-PCI или IOS). К выводам RxD — приемник и TxD — передатчик через линию связи подключаются передатчик и приемник другого абонента или устройства. Если связь производится через модем, то доступны любые сети.

Для формирования точных, различных по частоте и длительности сигналов, в т.ч. и звукового диапазона используется программируемый интервальный таймер ПИТ-PIT, имеющий три независимых 16-ти разрядных двоичных счетчика. Задержка, длительность или частота выходного сигнала каждого счетчика кратна 3..65535 периодам входного сигнала.

Если в системе используется режим прерывания выполнения основной программы внешними устройствами, требующими безотлагательного вмешательства микропроцессора, то может применяться программируемый контроллер прерываний ПКП — PIC (устройство собирающее заявки на обслуживание от ВУ с входов IRi). Подробно прерывания будут рассмотрены ниже.

Обмен данными между МП и ЗУ или одним из ВУ возможен только при появлении на выходе дешифратора DC единственного сигнала

CS = 0, поступающего на то устройство с которым будет производиться запись или чтение байта данных. Остальные (невыбранные) устройства будут в пассивном состоянии, т.к. их сигналы

CS = 1. Байт информации на ШД считывается ВУ, ЗУ или МП в строго ограниченном интервале времени во время действия одного из управляющих сигналов чтения/записи (

MEMW) из памяти или в память, или во время действия одного из сигналов управления вводом/выводом (

Быстрый обмен данными может производиться с помощью устройства прямого доступа к памяти ПДП (DMA).

Область памяти с упрощенной схемой адресации, к которой МП обращается по принципу «последним вошел — первым вышел» (LIFO). Байты программы в оперативной памяти располагаются последовательно по нарастающим адресам. Стек заполняется по последовательно убывающим адресам. Во избежание перекрытия этих двух областей памяти стек обычно располагается в старших адресах. Начальный адрес стека, называемый дном (bottom) записывается в регистр SP командой MOV SP,0fffeh. Вместо 0fffeh — адрес предпоследнего байта сегмента, может быть другое значение, но выравненное по двухбайтовым, т. е. четным адресам. Текущее значение содержимого SP называется, также адресом вершины стека (top). Если адрес вершины совпадает с адресом дна — стек считается пустым. Рассмотрим механизм помещения в стек и извлечения из него данных на примере команд PUSH AX и POP BX. Пусть начальное значение аккумулятора AX равно 874c.

Команда PUSH выполняется в четыре этапа:

- Адрес в SP уменьшается на 1: (SP)

Дата добавления: 2016-02-20 ; просмотров: 898 ; ЗАКАЗАТЬ НАПИСАНИЕ РАБОТЫ

📽️ Видео

Лекция 3 Программирование микропроцессорных системСкачать

Лекция "Проектирование отказоустойчивых микропроцессорных систем"Скачать

5.Микропроцессорные системы. Виды и классификация микроконтроллеровСкачать

Микропроцессорные системыСкачать

Установка микропроцессорной системы зажигания Secu-3T ЧАСТЬ 1.Скачать

Лекция 1: Электронная системаСкачать

Лекция 3: Шинная структура данныхСкачать

Понятие Микропроцессорной системыСкачать

МПСЗ на минималках #1. Своими руками .Теория.Скачать

Чем отличается МИКРОКОНТРОЛЛЕР и МИКРОПРОЦЕССОРСкачать

Газ-69. Микропроцессорная система зажигания (МПСЗ). Первый выезд из гаража.Скачать

Микропроцессорная техника 3 курс 1 занятиеСкачать

Семинар 3 "Построение микропроцессорной системы на основе микроконтроллера"Скачать

Лекция "Аналоговые устройства в микропроцессорных системах"Скачать

Лекция 310. Шина USB - функциональная схемаСкачать