PCI – фактически стандартная шина, ставшая локальной шиной для микрокомпьютерных систем и все персональные компьютеры имеют шину PCI в своем составе. Однако, хотя эта шина так распространена, кажется невозможным эксперимент, в котором бы она использовалась. PCI кажется такой, что руки любителя никогда ее не коснутся, несмотря на ее высокую производительность.

Фактически невозможно создать PCI плату, которая бы удовлетворяла требованиям стандарта PCI, из одних только стандартных логических микросхем. Но PCI сложная как целая система, однако ее основная часть работают по очень простому протоколу. Поэтому, вполне возможно, чтобы PCI-плата, работающая только как ведомое устройство, была выполнена на небольшой микросхеме программируемой логики. Но следует заметить, что PCI-плата собранная подобным образом не является полноценным PCI устройством и не должна использоваться для управления чем либо. Это лишь эксперимент, производимый с целью понять работу шины PCI.

Основные циклы шины

Цикл записи

Это простейший цикл шины. Устройство назначения определяет начало цикла шины по установившемуся сигналу FRAME#, при следующем тактовом цикле. Как только цикл шины инициирован, команда и адрес выдаются всем устройствам, подключенным к шине, и устройство, определившее, что этот цикл для него, устанавливает сигнал DEVSEL#, отвечая таким образом шине. Поскольку устройство назначения отвечает за 1 такт, это называется быстрое декодирование. Если бы устройство назначения ответило бы на второй или третий цикл тактовой частоты, это было бы среднескоростным или медленным декодированием.

После того, как устройство назначения ответит сигналом DEVSEL#, оно удостоверяется в том, что сигнал IRDY# установлен (записываемые данные верны), и берет данные. В то же самое время устройство назначения знает, что это последний цикл передачи, поскольку FRAME# не установлен, а IRDY# установлен, что означает, текущие данные – последние.

Когда последние данные взяты, устройство назначения сбрасывает сигналы DEVSEL# и TRDY#, эти сигналы будут освобождены при следующем тактовом цикле, таким образом устройство назначение завершило цикл шины.

Это простейший цикл чтения. Здесь требуется один такт буферного цикла, так как агент, который управляет линиями адреса/данных меняется. Таким образом цикл чтения по сравнению с циклом записи требует на один такт больше.

Устройство назначения определяет начало цикла по установившемуся сигналу FRAME# при втором тактовом сигнале (см. рисунок). Как только цикл шины инициирован, команда и адрес выдаются всем устройствам шины. Устройство, которое определило, что этот цикл для него, устанавливает сигнал DEVSEL#, что бы ответить на цикл шины. В этом случае, потому как устройство отвечает на второй цикл, это среднескоростное декодирование. Необходимо выставить данные на шину с паузой в 1 такт, чтобы сменить агента, управляющего линиями адреса/данных. Для этого все равно потребуется 1 такт, даже если устройство ответит в режиме высокоскоростного декодирования.

После двух циклов тактовой частоты с момента старта цикла шины, устройство назначения помещает данные на линии адреса/данных и устанавливает сигнал TRDY#. При следующем тактовом цикле, устройство назначения проверяет сигнал IRDY#. Если IRDY# установлен (инициатор принял данные), передача данных завершена. Сигнал FRAME# сброшен, это значит, что текущие данные последние. Устройство назначения обнаруживает это и завершает транзакцию.

После того, как последние данные переданы, устройство назначения сбрасывает сигналы DEVSEL# и TRDY#, эти сигналы будут освобождены при следующем тактовом цикле, транзакция на этом заканчивается.

Цикл записи (Передача Очередью)

Передача очередью не отличается от отдельной передачи. Устройство назначения проверяет сигнал FRAME# при каждой передаче данных. Если сигнал FRAME# остается установленным, устройство назначения распознает это как следующую передачу данных. Так работает передача очередью. Передача очередью в основном применяется для доступа к памяти, однако может использоваться и для доступа к устройствам ввода/вывода.

Передача очередью демонстрирует наибольшую производительность PCI. Это легко представить, если вспомнить, что в шине PCI адрес и данные мультиплексированы. При передаче очередью адрес назначения определяется 1 раз при старте передачи данных, и этого вполне достаточно. Таким образом PCI уменьшает число проводов, стоимость, но также и стабильность передачи данных.

Видео:Тестер PCI-E 16x и AGP шины видеокартСкачать

Быстрая компенсационная транзакция

Метод первой компенсационной транзакции определен для того, чтобы сделать использование шины эффективным.

Обычно, по крайней мере один тактовый цикл ожидания существует между двумя циклами шины (транзакции). Цикл ожидания это буферное время, чтобы предотвратить коллизии. Однако от этого можно отказаться, когда переключения устройств не происходит между циклами шины.

Работа платы ввода/вывода: Состояния

Поскольку PCI полностью синхронная шина, все операции основаны на системной частоте. В PCI пате необходимо реализовать, концепцию конечного автомата, при которой команда от инициатора обязательно должна быть выполнена. Наша плата ввода вывода реализует конечный автомат всего на одной плис (GAL22V10). Теперь давайте перечислим состояния и связи, представим их на рисунке и объясним.

Шина в ожидании. Начало нового цикла шины определяется из этого состояния. Из этого состояния устройство может перейти в СОСТОЯНИЕ 2 или СОСТОЯНИЕ 3, когда цикл ввода/вывода инициируется для данного устройства. Также возможен переход в СОСТОЯНИЕ 0, когда запускается цикл шины, не взаимодействующий с этим устройством.

Читайте также: Как понять какие у меня шины

Шина не с в состоянии ожидания. Выполняется любая другая транзакция. Ожидаем, пока шина перейдет в состояние ожидания. Из этого состояния не может начинаться новый цикл.

Цикл записи для этого устройства запущен. Устройство устанавливает сигнал DEVSEL# и отвечает циклу шины. В тоже время, устройство устанавливает сигнал TRDY# и показывает, что данные для записи приняты. В тоже самое время устройство защелкивает данные и переходит в СОСТОЯНИЕ 3, когда сигнал IRDY# установлен (инициатор может принять прочитанные данные) и сигнал FRAME# не установлен (последние данные).

DEVSEL# и TRDY# не установлены. Обычно, DEVSEL# и TRDY# освободятся при следующем цикле тактовой частоты, устройство переходит в ожидание (СОСТОЯНИЕ 0). Но, оно непосредственно переходит в СОСТОЯНИЕ 2 или СОСТОЯНИЕ 5 без прохождения через состояние ожидания (быстрая компенсационная транзакция).

Старт цикла чтения. DEVSEL# и TRDY# не установлены. Обычно, DEVSEL# и TRDY# освободятся при следующем цикле тактовой частоты, устройство переходит в ожидание (СОСТОЯНИЕ 0). Но, оно непосредственно переходит в СОСТОЯНИЕ 2 или СОСТОЯНИЕ 5 без прохождения через состояние ожидания (быстрая компенсационная транзакция).

Цикл чтения в процессе. Устройство назначения устанавливает сигнал DEVSEL# и отвечает на цикл чтения. В тоже время на линии адреса/данных выставляются считываемые данные и устанавливается сигнал TRDY#. В тоже время устройство переходит в СОСТОЯНИЕ 7, когда IRDY# установлен (инициатор может принять данные) и сигнал FRAME# не установлен (последние данные).

Цикл чтения закончен. Устройство назначения сбрасывает сигналы DEVSEL# и TRDY#. Тогда сигналы DEVSEL# и TRDY# освобождаются при следующем такте и шина переходит в ожидание.

Это состояние не определено. Даже если устройство перейдет в него в результате ошибки, оно сразу же перейдет в СОСТОЯНИЕ 0 при следующем цикле тактовой частоты, и возвращается в нормальный цикл.

Нарушения правил разработки

Видео:Что такое PCIe? Все виды скоростного интерфейса подключения PCIe 1.0-6.0 (x1 x4 x8 x18 x32)Скачать

Схема устройства в этом эксперименте упрощена путем частичного исключения функций, необходимых для стандарта PCI. Я поясню исключенные функции и вред от их исключения. Это никогда не станет причиной проблем.

Отсутствие регистра конфигурации

Система определяет существование в системе PCI устройства используя регистр конфигурации. Он реализован в устройстве для установки функции устройства как PCI устройства или для перемещения адресов ресурсов чтобы избежать конфликтов.

Адрес назначения в этом устройстве декодируется фиксировано, без подключения регистра конфигурации. Вы должны установить адрес назначения так, чтобы не возникало конфликтов ресурсов, поскольку существование устройства не распознается системой. Наша PCI плата будет смеяться J

Отсутствует функция генерации и проверки четности

Ошибка четности обязательно произойдет при цикле чтения, поскольку проверка или управление сигналом четности не выполняется. Любая операция, такая как NMI произойдет, когда обнаружится ошибка четности, если бит, отвечающий за ошибку четности в конфигурационном регистре инициатора (PCI контроллер) установлен. Но всего этого не произойдет, так как этот бит в персональных компьютерах обычно сброшен.

Старшие 16 бит адреса не распознаются

Только младшие 16 бит адреса декодируются нашей платой, хотя PCI устройство должно декодировать все 32 бита адреса. Но это не вызывает проблем, поскольку запросы к пространству адресов выше 64 килобайт в персональных компьютерах не происходят.

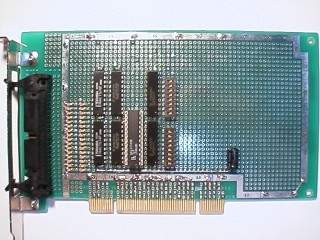

Я использую макетную плату для PCI MCC-331(Sunhayato). Она имеет монтажный разъем, поэтому легче в использовании.

ПЛИС должна быть в диапазоне быстродействия 7 нс или быстрее. Даже 7 нс спецификации PCI. Но так как приобрести ПЛИС с быстродействием выше 5 нс проблематично, ПЛИС используется на границе своих возможностей. Это не вызывает проблем.

Все другие детали типовые и выбирать их производителя не требуется. Ввод и вывод имеют разрядность 16 бит, поскольку это отнимает свободное место на разъеме, хотя существуют применения, где требуются все 32 бита.

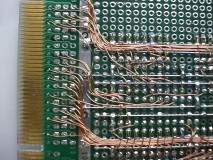

Поскольку это цифровая схема, я думаю долго возиться с ней не придется. Так как на ней много проводов, полезно будет посмотреть это для правильной прокладки проводов. Не используйте любые другие провода, так как в этом случае это становится похожим на гору. Вы должны очень тщательно прокладывать провода, ошибки недопустимы. Здесь легко ошибиться. Я тоже ошибаюсь иногда J . В особенности опасна ошибка подключения контактов разъема, по которым подается питание, это может вывести из строя материнскую плату. Более того, вы должны усилить питающую линию полностью, потому как она работает на высоких частотах, с максимумом в 33 МГц.

Во первых, установите адрес ввода/вывода для этого устройства с помощью переключателей на плате. Поскольку младшие 2 бита не декодируются, 4 байта, которые они составляют занимаются этим устройством. Шина будет конфликтовать когда адрес ввода/вывода дублируется с любым другим устройством PCI в одно и тоже время. Ненужно говорить, что вы должны выбрать адрес, который никем не используется.

Например, когда в устройстве установлен адрес F300h, оно отвечает на адреса с F300h по F303h.

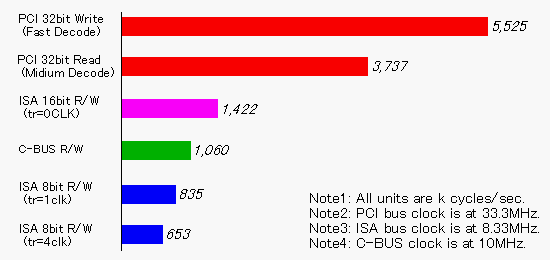

Сравним производительность. Тест считает количество циклов в секунду, которые взаимодействуют с устройством. Вот результаты:

Видео:AGP 8x против старой версии шины PCI(32bit) на примере FX5500Скачать

Как и следовало ожидать PCI показал огромную производительность по сравнению с ISA. Для операции записи 6 тактов/цикл, чтения – 9 тактов/цикл как показали вычисления. Но, так как теоретически на запись/чтение требуется 3 и 4 такта соответственно, мы можем утверждать, что скорость передачи не достигает своего максимума (слишком большое время ожидания на шине). Потеря времени по всей видимости происходит на контроллере PCI материнской платы. Однако, PCI разработана так, что наилучшая производительность достигается при передаче очередью. Снижение производительности при отдельной передаче неизбежно.

Читайте также: Организация can шины в автомобиле

Так же имеются различия в скорости передачи, почти в два раза на шине ISA, при 8ми и 16 битном доступе. Здесь цикл уменьшается, когда устройство отвечает как 16 битное. Это хорошо, когда даже 8 битное устройство может работать с -IOCS16, когда имеется возможность повысить производительность шины ISA.

Ну и как вам статья? Шина PCI, которая казался столь сложной и не возможной для изучения, так же может использоваться и для любительских целей. Хотя все же в общем она кажется сложной, можно заметить, что она основана на удивительно простых процессах.

Выполнение транзакций на шине PCI. Реализация на VHDL

Не так давно я спрашивал о механизме опроса PCI-устройств. После я устроился на работу, доделал тестовое задание, а спрашивал я именно о нем, и благополучно забыл о нем. Но недавно выдали новый проект и пришлось все вспомнить, заодно и решил написать сюда.

Транзакций на шине PCI достаточно много, в данном топике будет описаны только следующие:

- Конфигурационные транзакции

- Транзакции ввода/вывода

- Транзакции обращения к памяти

При осуществлении транзакций возможно 2 варианта:

- Когда ведущим устройством является южный мост

- Когда ведущим устройством является устройство, подключенное к шине PCI

Как уже сложилось, при рассмотрении шины PCI, ведущее устройство я буду называть мастером(Master), ведомое — таргетом (Target).

В данной статье рассматриваются только транзакции, когда мастером является южный мост, так как транзакции, когда мастером является устройство, подключенное к шине PCI заслуживает отдельной статьи.

И так, для работы с шиной, нам понадобятся следующие сигналы:

clk (Clock) — обеспечивает синхронизацию всех транзакций на PCI, а также является входным для каждого PCI — устройства.

AD (Address and Data) — мультиплексирования шина адреса и данных.

IDSEL (Initialization Device Select) — выбор устройства инициализации, используется для выбора кристалла при транзакциях чтения конфигурации и записи.

CBE (Bus Command and Byte Enables) — команды шины и разрешение байта.

FRAME (Frame) — сигнал выдаётся мастером в начале транзакции и определяет её длительность. Для однофазных транзакций FRAME всегда длится один такт. При многофазных транзакциях FRAME снимается за один такт до завершения транзакции.

IRDY (Initiator Ready) — сигнал готовности мастера. Он свидетельствует о готовности мастера завершить текущую фазу данных.

TRDY (Target Ready) — сигнал готовности таргета, свидетельствующий о готовности таргета завершить текущую фазу данных.

STOP (Stop) — этот сигнал выдаётся таргетом, если он хочет остановить текущую транзакцию.

PAR (Parity) — контроль четности по линиям AD и CBE.

RST(Reset) — cигнал сброса. Является асинхронным.

DEVSEL (Device Select) — сигнал выбора устройства.

Перед началом работы с любым устройством его нужно инициализировать. Поэтому рассмотрим особенности выполнения конфигурационных транзакций.

Конфигурационные транзакции. Общие сведения.

Для генерации конфигурационных транзакций PCI на ПК используются обращения к двум портам ввода-вывода, носящим имена CONFIG_ADDRESS и CONFIG_DATA, имеющим адреса 0CF8h и 0CFCh соответственно и входящим в состав моста Host–PCI, через который шина PCI прямо или косвенно соединяется с процессором.

Порт CONFIG_ADDRESS имеет размер двойное слово и доступен только как единое целое. Обращения меньшего размера по принадлежащим ему адресам передаются на шину PCI как обычные транзакции ввода-вывода. Этот порт доступен для чтения и записи и имеет следующий формат:

Когда необходимо выполнить конфигурационную транзакцию, в этот порт записывается адрес регистра конфигурационного пространства PCI, состоящий из номеров шины (разряды 23–16), устройства (15–11), функции (10–8) и собственно регистра (7–2). Биты 1 и 0 должны всегда содержать нули, а старший бит должен содержать единицу, разрешая тем самым выполнение конфигурационной транзакции. Разряды 30–24 зарезервированы и должны содержать нули.

Собственно генерация конфигурационной транзакции происходит при чтении или записи порта CONFIG_DATA, когда в CONFIG_ADDRESS был записан адрес с установленным старшим битом и номером шины, соответствующим шине, подключенной к мосту Host–PCI, или любой шине PCI, лежащей ниже этой шины и соединённой с ней через один или несколько мостов PCI–PCI (допустимый диапазон номеров шин задаётся мосту Host–PCI в процессе его настройки). Доступ к порту CONFIG_DATA должен иметь размер, равный размеру считываемого или записываемого конфигурационного регистра, адрес которого находится в CONFIG_ADDRESS.

Если номер шины, заданный в CONFIG_ADDRESS, совпадает с номером шины, подключённой непосредственно к мосту Host–PCI, генерируется конфигурационная транзакция с адресом типа 0, причём номер устройства, находящийхся в разрядах 15–11 порта CONFIG_ADDRESS, используется для выдачи одного из сигналов IDSEL, которые и служат для выбора конкретного устройства. Кроме того, декодированный номер устройства (один единичный и остальные нулевые биты) в фазе адреса конфигурационной транзакции передаётся в разрядах 31–11 адреса.

Если адрес в CONFIG_ADDRESS указывает не ту шину, которая непосредственно подключена к мосту Host–PCI, последний генерирует конфигурационную транзакцию с адресом типа 1. Она будет обработана мостом PCI–PCI, который опознает содержащийся в адресе номер шины. Этот мост либо выполнит конфигурационную транзакцию с адресом типа 0 (если адресуемое устройство подключено к шине, прямо подсоединённой к этому мосту), либо сгенерирует транзакцию с адресом типа 1, обеспечив тем самым её прохождение через следующий мост. Длина этой цепочки теоретически ограничена только разрядностью поля, отведённого под номер шины (8 бит).

Читайте также: Ниссан либерти размеры шин

Если при выполнении транзакции выяснится, что адресуемого конфигурационного регистра не существует (указан номер несуществующей шины, устройства, функции или регистра), то операция записи не возымеет никаких действий, а операция чтения вернёт процессору значение, содержащее единицы в каждом разряде

Видео:Pci To Sata 3 Контроллер Marvell vs Asmedia. Тест плат расширения. H1111zСкачать

Формат адреса для транзакции типа 1.

Формат адреса для транзакции типа 0.

Формат регистра конфигурации:

Минимальный набор регистров:

- Vendor ID — поле идентифицирует изготовителя устройства. Запрещено использовать значение 0xFFFF.

- Device ID — поле идентифицирует конкретный вид устройства. Запрещено использовать значение 0xFFFF.

- Revision ID — дополнение к идентификатору устройства. Может быть равно нулю.

- Header Type — Для многофункциональных устройств. Если 7ой бит равен 0, то устройство является однофункциональным, иначе — многофункциональное.

- Class Code — доступен только для чтения. Используется для идентификации общего функционального назначения устройства. Старший байт (адрес 0Bh) определяет базовый класс, средний — подкласс, младший — программный интерфейс (если он стандартизован).

- Subsystem ID, Subsystem Vendor ID — задаются производителем. Только для чтения. Хранят идентификаторы, позволяющие точно идентифицировать карты и устройства (в системе могут быть установлены

несколько карт с совпадающими идентификаторами устройства и производителя (Device ID и Vendor ID). - BAR0 — BAR5 — описывают области памяти и портов ввода-вывода.

Для областей памяти и портов описания различаются:

- Бит 0 = 0 — признак памяти. Размером не более 2 Гбайт

- Бит 0 = 1 — признак области портов. Размером до 256 байт.

Размер областей вычисляется следующим образом. В BAR записывается 0xFFFFFFFF. Далее, из BAR считывается значение, и вычитается из 0xFFFFFFFF. Результат и есть размер области. Единица в младшем бите не учитывается.

Общий алгоритм выполнения транзакций

Мастер выставляет на шине AD адрес устройства, на шине CBE выполняемую команду, устанавливает сигнал FRAME в 0 и сигнал IRDY в 0. Далее, мастер ждет от таргета — выставления им сигналов TRDY и DEVSEL. Так же, таргет выставляет на шину AD запрашиваемые данные. Данные считаются валидными, когда IRDY, TRDY и DEVSEL равны уровню логического нуля.

Реализация

Для обращения к выводам ПЛИС потребуются специальные компоненты: буферы ввода/вывода для работы с Z — состоянием.

Так, для шины AD подключение будет выглядеть следующим образом:

- O — выход буфера.

- IO — вход/выход буфера, непосредственно подключается к выводу ПЛИС.

- I — выход буфера.

- T — управление входом, уровень единицы — вход, уровень нуля — выход.

Для остальных сигналов аналогично, не буду приводить, что бы не загромождать статью.

Как я уже писал выше, при начале транзакции, когда на шине AD выставлен адрес, всегда сигнал FRAME равен нулю. Ниже приведен код, который формирует сигнал AdrPhASE, во время действия которого нужно защелкнуть шину адреса и шину команд для последующей работы. Фактически сигнал AdrPhASE есть ни что иное, как выделение спадающего фронта сигнала FRAME, что однозначно идентифицирует начало транзакции.

Далее, работу всего устройства можно описать с помощью автомата.

Для понимания выше написанного, приведу возможные команды, передаваемые по шине CBE.

- 0010 I/O Read

- 0011 I/O Write

- 0110 Memory Read

- 0111 Memory Write

- 1010 Configuration Read

- 1011 Configuration Write

Каждой команде соответствует свое состояние автомата. Переход в него зависит от текущего состояния шины CBE и шины AD для транзакций обращения к памяти и портам ввода-вывода. Выход в начальное состояние осуществляется по приходу сигнала IRDY от мастера.

Чтение конфигурации

Видео:Урок по диагностике видеокарт. Как отремонтировать видеокарту?Скачать

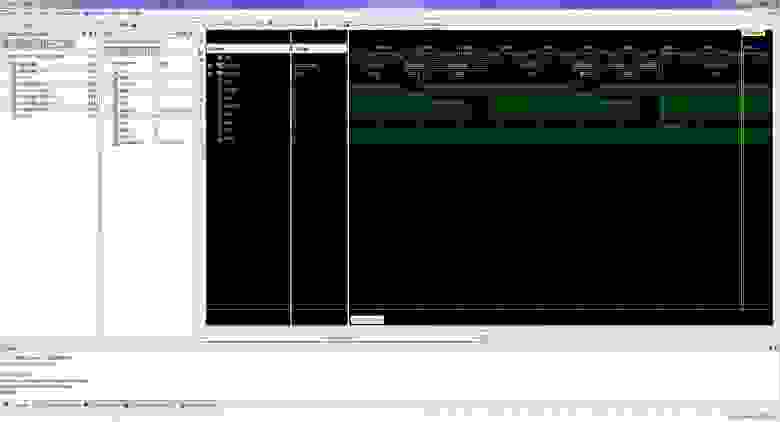

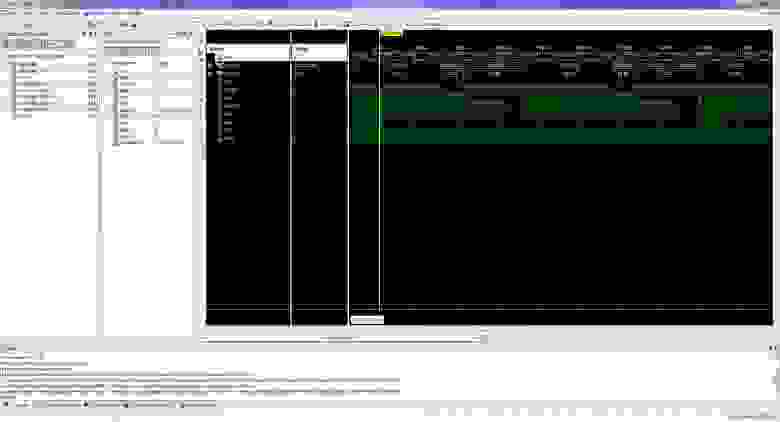

Так выглядит чтение конфигурации в симуляторе:

Запись конфигурации

Запись в порт

На шине AD мастером выставляется номер регистра для записи, в следующем такте выставляются данные, которые нужно записать.

Приведем пример только для записи одного регистра, остальные записываются аналогично.

Чтение порта

Так выглядит запись и чтение порта ввода-вывода:

Запись и чтение памяти

Так выглядит запись и чтение памяти в симуляторе:

Данные на шину AD выводятся следующим образом. В зависимости от состояния автомата, к выходному буферу подключается соответствующий регистр.

Сигнал разрешения выдачи данных на шину AD формируется следующим образом:

Отдельно хотелось бы добавить про компонент STS на примере выработки сигнала DEVSEL

Так как, активные уровни управляющих сигналов равны нулю, то для перехода в Z — состояние и отпускания линии нужно предварительно выдать уровень логической единицы и только потом перевести в Z — состояние.

Заключение

В заключение хочу сказать, что выполнение транзакций на шине PCI не так сложно как кажется. Разработанная прошивка была залита в ПЛИС. Плата с ПЛИС вставлена в PCI слот и был включен компьютер. Система нашла плату и запросила драйвера на нее.

Работает! ?

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле

- Правообладателям

- Политика конфиденциальности

Видео:5 лекция "Шины AGP и PCI Express"Скачать

💥 Видео

эксперимент с задержкой шины pciСкачать

Райзер для видеокарт с неисправной шиной PCI-E (первая дифференциальная пара)Скачать

Гибкий удлинитель-шлейф PCI шиныСкачать

Шина PCIСкачать

ОБЪЯСНЯЕМ PCI Express 4.0Скачать

Шина PCI Express: эволюция от поколения к поколениюСкачать

Обзор: ASM1083 Мост PCI-e - PCIСкачать

PCI и PCI-Express что можно подключитьСкачать

Компьютерная шина PCI ExpressСкачать

Райзер PCI-express для видеокарты своими рукамиСкачать

Влияние шин PCI-e и внутренней шины видеокарты на производительностьСкачать

Очень маленький socket 370 и самый быстрый gpu на шине PCIСкачать

Системная шина персонального компьютера PCIСкачать

Этой штукой можно узнать что сломалось в ноутбуке. Тестер-анализатор PCI PCI-E LPC. 3в1.C AliExpressСкачать

.png)

.png)

.png)

.png)

.png)