Из импульсных и цифровых устройств (логические элементы, триггеры, счетчики, регистры и т.д.), в принципе, возможно создать электронную систему любой сложности. На начальных этапах применения электроники для автоматизации судовых процессов так и поступали. Однако, с повышением сложности решаемых задач увеличивался объем электроники, снижалась надежность, поскольку требовались сотни и тысячи электронных компонентов. Выход из этого тупика был найден с разработкой микропроцессоров. Можно утверждать, что появление микропроцессоров оказало такое революционное воздействие на все сферы человеческой деятельности, которое можно сопоставить с овладением человечеством энергией водяного пара. Достигнутый к настоящему времени уровень автоматизации морских судов, характеризуемый безвахтенным обслуживанием энергетической установки, почти двухкратным сокращением численности судового экипажа (наряду со значительным улучшением условий труда и отдыха) стал возможен благодаря системам комплексной автоматизации, построенным на основе микропроцессоров.

Микропроцессор – программно-управляемое устройство, предназначенное для обработки цифровых данных и выполненное в виде одной или нескольких больших интегральных микросхем (БИС). Первый микропроцессор был разработан фирмой Intel в начале 70-х годов 20-го столетия. К началу 80-х годов были разработаны микропроцессоры типов 8080, 8086, 8088, Z80 и в настоящее время широко применяемые на судах. Классическим, со всеми характерными чертами микропроцессора, стал микропроцессор 8080 фирмы Intel, аналог которого выпускался в том числе и в нашей стране. Он выполнен в виде одной БИС, содержащей около 5000 транзисторов.

Микропроцессор самостоятельно функционировать не может. Он входит основной составной частью в микроЭВМ.

МикроЭВМ – это ЭВМ, содержащая микропроцессор, запоминающее устройство и контроллеры (адаптеры) устройств ввода/вывода. На основе микроЭВМ строятся судовые микропроцессорные системы управления (МПСУ). Под МПСУ понимается управляющая система, включающая в себя микроЭВМ, средства сопряжения с объектом управления (датчики, исполнительные механизмы) и средства связи с оператором (человеком).

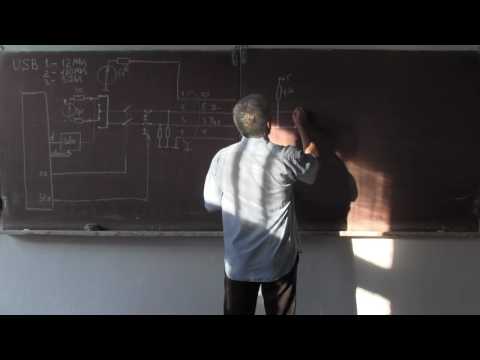

Основные элементы микропроцессора и микроЭВМ приведены на рис. 1:

— АЛУ – арифметико–логическое устройство, выполняет логические и простейшие арифметические операции – И, ИЛИ, НЕ, сложение, вычитание, умножение, деление;

— регистры – ячейки памяти для временного хранения информации;

— дешифратор — по двоичному коду команды распознает её существо;

— счетчик команд – задает в двоичном коде адрес ячейки памяти, в которой находится очередная команда, подлежащая выполнению;

— устройство управления – управляет работой микропроцессора и ЭВМ;

— ГТИ – генератор тактовых импульсов, задаёт темп работы микропроцессора;

— ЗУ – запоминающее устройство;

— ЗУП – запоминающее устройство программ (ПЗУ – постоянное запоминающее устройство);

— ЗУД – запоминающее устройство данных (ОЗУ – оперативное запоминающее устройство);

— контроллеры (адаптеры) – для ввода и вывода информации из микро ЭВМ.

Для взаимодействия этих блоков они связаны между собой электрическими линиями, которые по функциональному признаку сведены в три группы (шины) образующие внутреннюю магистраль микроЭВМ. По шине данных (англ. – Data Bus) информация передаётся между микропроцессором и другими устройствами микро ЭВМ. Информация выражена в двоичном коде определенной разрядности, обычно соответствующей разрядности микропроцессора.

Разрядность микропроцессора – число разрядов двоичного кода, которым представляется информация в микропроцессоре и который он способен обработать в один прием. Характерным для большинства судовых микроЭВМ является 8 или 16 разрядный код. Чем выше разрядность, тем выше производительность микроЭВМ.

Рис. 1. Структурная схема микропроцессора и микроЭВМ

По шине адреса (англ. – Adress Bus) в виде двоичного кода передается адрес ячейки памяти, к которой обращается микропроцессор или адрес контролера (адаптера).

По шине управления (англ. – Control Bus) передаются сигналы, сопровождающие передаваемую по шине данных информацию. Например: сигнал RD — считать содержимое ячейки памяти; сигнал WR – записать (RD, WR – наименование сигналов, сокращение от англ. «read» и «write«).

Взаимодействуют блоки микроЭВМ следующим образом. После подачи питания счётчик команд в виде двоичного кода, подаваемого в шину адреса, задает адрес ячейки, находящейся в ЗУП. В ней содержится первая выполняемая команда. Команды хранятся в ЗУП в виде чисел, выраженных двоичным кодом.

На втором этапе по шине управления передаётся сигнал «RD» и содержимое этой ячейки через шину данных поступает в микропроцессор. В дешифраторе эта команда (ее двоичный код) распознаётся и микропроцессором (АЛУ) выполняются оговорённые ею действия. Результат выполнения команды помещается в один из регистров памяти или в ячейку ЗУД. По завершении выполнения этой команды счетчик команд получает приращение – на его вход подается импульс, который увеличивает двоичный код адреса. Этот адрес снова поступает на шину адреса, происходит считывание и выполнение очередной команды и т.д.

Если существо очередной выполняемой команды состоит в передаче информации на одно из внешних устройств – принтер, дисплей и т.д., то по шине адреса задаётся адрес контроллера (адаптера) этого устройства.

Таким образом, процесс выполнения каждой команды протекает в несколько этапов, называемых машинными тактами. Длительность машинного такта равна периоду импульсов, вырабатываемых ГТИ. Чем выше частота тактовых импульсов, тем большее число команд в единицу времени может выполнить микропроцессор и микроЭВМ. Однако максимальное значение тактовой частоты ограничено быстродействием элементов (транзисторов), на которых он построен. Так, 8-разрядный микропроцессор 8080 способен работать с тактовой частотой 2,5 МГц, что позволяет ему выполнять около 600 тысяч простых команд, каждая из которых занимает 4 машинных такта. Более совершенный микропроцессор 8088 имеет тактовую частоту до 10 МГц, что обеспечивает ему, наряду с вдвое большей разрядностью (16 разрядов) в несколько раз большую производительность.

Данные микропроцессоры разработаны в 70-х годах и их тактовая частота к настоящему времени представляется весьма скромной. Однако их производительность вполне достаточна для решения задач автоматизации отдельных объектов судового энергетического оборудования, что и обеспечивает им широкое применение. Современные же высокопроизводительные 32-, 64-разрядные микропроцессоры, тактовая частота которых находится на уровне нескольких гигагерц, используются в судовых ЭВМ, выполняющих роль диспетчерских станций. Эти ЭВМ связывают отдельные, локальные подсистемы автоматики, построенные на более простых ЭВМ в единую систему комплексной автоматизации СЭУ, координируют их работу, являются по существу постом управления всей СЭУ. Их структура и параметры, организация программного обеспечения близки к таковым у персональных ЭВМ (англ. – РС).

- Назовите основные элементы микропроцессора и микроЭВМ.

- Какие группы образуют внутреннюю магистраль микроЭВМ?

- Дайте определение разрядности.

- Как разрядность влияет на производительность процессора?

- В чем отличие ОЗУ от ПЗУ?

- Что такое машинный такт?

По шине адреса микро эвм сигналы передаются в виде

1. Устройство и работа микро-ЭВМ

В состав любой ЭВМ входит арифметико-логическое устройство (АЛУ). Оно выполняет некоторый набор арифметических и логических операций над входными словами (операндами) фиксированной разрядности, выдавая результат в виде выходного слова той же разрядности. Вид выполняемой в АЛУ операции задается устройству внешним кодом операции. При арифметических операциях АЛУ учитывает перенос из младших разрядов и генерирует перенос в старшие разряды результата. Логические операции выполняются параллельно и независимо над соответствующими битами операндов.

Кроме переноса в старшие разряды, который представляет собой признак переполнения разрядной сетки АЛУ, в устройстве могут формироваться и другие признаки результата, такие как равенство результата нулю, его положительность, четность и др.

Принцип действия комбинационного АЛУ удобно пояснить с помощью функциональной схемы (рис.1.1). Здесь изображено двухразрядное АЛУ, обеспечивающее выполнение четырех операций: поразрядных логических «И», «ИЛИ», «исключающего ИЛИ» и арифметического сложения. Схема построена на основе набора комбинационных устройств, выполняющих нужные операции, и выходных мультиплексоров. Мультиплексоры передают на выходы АЛУ выходные сигналы тех комбинационных устройств, которые реализуют операцию, заданную кодом операции.

Схемой АЛУ предусмотрено формирование следующих признаков результата:

Видео:Как работает LIN шина автомобиля. K-Line L-Line шины данных. Лин шина автомобиля. Lin-bus networkСкачать

F2 переполнение разрядной сетки (перенос в старшие разряды);

P положительный результат («плюс»);

Z нулевой результат («ноль»).

Признаки Z и Р формируются всегда, а признак F2 только при выполнении операции арифметического сложения.

Реальные АЛУ имеют, как правило, значительно большее число выполняемых операций, а их структура синтезируется по таблицам истинности.

Шиной принято называть множество идущих параллельно проводников, имеющих одинаковое функциональное назначение. В цифровой технике многоразрядные шины используются для передачи параллельных двоичных кодов с одного устройства на другое.

Очень часто требуется подключать многоразрядную шину к выходу одного из многих цифровых устройств источников параллельного двоичного кода, то есть осуществлять мультиплексирование этой шины. Номер активного источника, передающего на шину свой код, задается при этом с помощью двоичного адреса.

Читайте также: Шины гудрич алл террайн ко2

Очевидно, что можно решить эту задачу, установив мультиплексоры с нужным числом входов в каждом из разрядов шины. Именно так и сделано при составлении функциональной схемы АЛУ (рис.1.1). Однако в общем случае, такое решение оказывается неэкономичным. Повышенные аппаратные затраты связаны здесь с многократным дублированием одинаковых и включенных параллельно по входам дешифраторов, входящих в состав мультиплексоров.

Рис.1.1. Функциональная схема АЛУ

На практике задача мультиплексирования многоразрядной шины решается с помощью особых вариантов цифровых устройств, имеющих выходы с тремя состояниями или открытым коллектором (не путать с общим коллектором!). На схемах такие выходы обозначают так, как показано на рис.1.2.

Принципиальная схема, обеспечивающая мультиплексирование многоразрядной шины, приведена на рис.1.3. Эта схема содержит ряд цифровых устройств АВС0 АВСN, выдающих информацию на шину D3 D0, а также единственный дешифратор, преобразующий поступающий извне адрес активного устройства в набор сигналов выбора устройств (микросхем, кристаллов) .

В каждый момент времени здесь активно лишь одно устройство, которое переводится в активное состояние (выбирается) ложным значением сигнала выбора. Именно оно определяет код, выставленный на шине. Иногда говорят, что активное устройство «захватывает шину». Остальные же устройства пассивны, то есть фактически отключены от шины. Этот режим обеспечивается истинными значениями логических сигналов на их входах выбора.

Современные микросхемы, предназначенные для работы в схеме (рис.1.3), обычно имеют выходы с тремя состояниями. Такие микросхемы удобно рассматривать с помощью модели (рис.1.4), использующей электромагнитное реле.

Рис.1.2. Обозначение на функциональных схемах выходов с тремя состояниями и открытым коллектором

Рис.1.3. Принципиальная схема мультиплексирования многоразрядной шины

Рис.1.4. Модель цифрового устройства, имеющего выходы с тремя состояниями

Основой модели здесь является цифровой блок АВС, выполняющий требуемые функции цифровой обработки. Однако выходы этого блока подсоединены к выводам микросхемы не непосредственно, а через размыкающие контакты реле К.

Если микросхема выбрана (сигнал выбора = 0), контакты реле замкнуты, и выходы с тремя состояниями являются обычными стандартными выходами логических элементов, входящих в цифровой блок. В этом состоянии микросхема передает свой код на шину.

Если же микросхема не выбрана ( = 1), контакты реле разомкнуты, то есть выходы цифрового блока просто отключены от выводов микросхемы, а, следовательно, и от выходной шины. Это третье состояние выходов (в дополнение к двум обычным: «логический ноль» и «логическая единица») часто называют высокоимпедансным.

В реальных устройствах функции реле К и его контактов конечно же выполняют полупроводниковые структуры.

Выходы с открытым коллектором типичны для микросхем, разработанных относительно давно. Тем не менее, такие микросхемы производятся и широко используются.

Выходной каскад с открытым коллектором отличается от стандартного выходного каскада ТТЛ логического элемента отсутствием верхнего выходного транзистора и относящихся к нему элементов (рис.1.5).

Рисунок показывает, что слова «открытый коллектор» означают просто то, что коллектор выходного транзистора VT4 никуда не подключен внутри микросхемы. Для нормальной работы выход с открытым коллектором должен быть соединен с «плюсом» источника питания через резистор нагрузки RН соответствующего номинала.

Рис.1.5. Построение выходного каскада логического элемента с открытым коллектором

Цифровые устройства, имеющие многоразрядный выход с открытым коллектором, строятся с использованием элементов Шеффера по схеме (рис.1.6).

Рис.1.6.Построение многоразрядного цифрового устройства, имеющего выходы с открытым коллектором

Устройства, имеющие выходы с открытым коллектором, подключают к многоразрядной шине точно также как и устройства, имеющие выходы с тремя состояниями. Однако сами проводники шины должны быть обязательно подключены к «плюсу» источника питания через нагрузочные резисторы. В этом случае оказывается, что выходные транзисторы всех пассивных устройств (для них сигнал выбора = 1) закрыты независимо от выходных сигналов их цифровых блоков, то есть эти устройства отключаются от шины. Напротив, единственное активное устройство (для него = 0) передает на шину данных выходные сигналы своего цифрового блока, инвертированные в элементах Шеффера.

Элементы, имеющие выходы с тремя состояниями или открытым коллектором, не только вводят в состав сложных цифровых устройств, но и выпускают в виде отдельных многоразрядных микросхем. В частности, выпускаются многоразрядные микросхемы повторителей или инверторов, имеющие выходы с тремя состояниями и повышенную нагрузочную способность. Такие микросхемы называют шинными формирователями. Они используются в тех случаях, когда нужно связать с многоразрядной шиной цифровые устройства, не имеющие выходов с тремя состояниями, либо имеющие маломощные выходы.

1.1.3.1. Постоянные запоминающие устройства

Постоянные запоминающие устройства (ПЗУ) осуществляют произвольное преобразование двоичных кодов.

Видео:03. Основы устройства компьютера. Память и шина. [Универсальный программист]Скачать

![03. Основы устройства компьютера. Память и шина. [Универсальный программист]](https://i.ytimg.com/vi/mjiJutISb6U/0.jpg)

Функциональная схема ПЗУ содержит полный n-разрядный дешифратор и матрицу логических сумм, задающую нужные выходные сигналы (рис.1.7).

Рис.1.7. Функциональная схема ПЗУ с информационной емкостью М=4х4 бит

Элементы «ИЛИ», использованные в этом ПЗУ, рассматривают логическое состояние свободного, то есть никуда не подключенного входа, как ложное. Таким свойством обладают, например, диодные ДТЛ элементы «ИЛИ».

Каждый из вертикальных проводников 00, 01, 10, 11, соединенных с выходами дешифратора, образует здесь совместно с входными проводниками элементов «ИЛИ» так называемую ячейку памяти.

Входной код, устанавливающий уровень логической единицы на вертикальном проводнике ячейки, называют адресом этой ячейки, а входы А1 и А0 адресными входами.

Адрес представляет собой двоичный номер ячейки внутри данного ПЗУ. Поэтому число ячеек ПЗУ N и число разрядов адреса n связаны соотношением .

При подаче на ПЗУ кода адреса какой-либо ячейки оно выдает на выходы данных двоичное число, записанное, запомненное в этой ячейке.

Запись в рассматриваемое ПЗУ осуществляют путем электрического соединения вертикальных и горизонтальных проводников в матрице логических сумм.

Отметим, что каждый горизонтальный проводник может иметь лишь одно соединение с вертикальными проводниками.

В рассматриваемом ПЗУ в ячейках с адресами 00, 01 и 10 записано слово 00002, а в ячейке с адресом 11 слово 11002.

Основной характеристикой ПЗУ является его информационная емкость М. Информационная емкость измеряется числом бит хранимой в ПЗУ информации. Часто эту емкость изображают в виде произведения числа ячеек ПЗУ на разрядность каждой ячейки. Например, ПЗУ, представленное на рис.1.7, имеет информационную емкость М = 4 х 4 бит.

Реальные ПЗУ имеют сотни и тысячи ячеек памяти, поэтому их информационные емкости могут выглядеть следующим образом: М = 512 х 4 бит; М = 1024 х 8 бит и т. п.

Емкость ПЗУ с восьмиразрядными ячейками часто измеряют в байтах. Используют и более крупные единицы измерения информационной емкости, такие как килобайт и мегабайт:

1 килобайт = 1К = 1024 байт;

1 мегабайт = 1 М = 1024 К = 1024х1024 байт.

Приставки кило- и мега- использованы здесь условно, так как число 1024 = 2 10 лишь приблизительно равно 1000.

Серийно выпускаются микросхемы ПЗУ следующих видов: масочные, однократно программируемые пользователем, перепрограммируемые со стиранием информации ультрафиолетовым облучением кристалла, перепрограммируемые со стиранием информации электрическим сигналом. Под стиранием здесь понимают подготовку ПЗУ к записи новой информации, а под программированием саму запись.

В масочные ПЗУ информацию заносят на заводе-изготовителе, и пользователь изменить ее не может. Однократно программируемые ПЗУ может запрограммировать сам пользователь. Однако повторное программирование таких микросхем невозможно.

Перепрограммируемые ПЗУ пользователь может программировать неоднократно, предварительно стирая ранее записанную информацию.

ПЗУ обычно имеют выходы с тремя состояниями или открытым коллектором и могут использоваться в схеме мультиплексирования многоразрядной шины (рис.1.3).

Регистры памяти предназначены для временного хранения многоразрядных двоичных кодов. Такие регистры обычно представляют собой параллельную группу синхронных D триггеров необходимой разрядности. Так, например, четырехразрядный регистр памяти со статическим управлением выполняют по схеме (рис.1.8а). Такой регистр повторяет входное слово, если тактовый сигнал С = 1, и запоминает, фиксирует это слово, если С = 0. Поэтому регистр со статическим управлением иногда называют «прозрачным фиксатором». Схема регистра с динамическим управлением, или как его иногда называют «регистра D-типа», представлена на рис.1.8б.

Рис.1.8.Функциональные схемы и условные обозначения четырехразрядных регистров памяти

При составлении функциональных схем используют специальные условные обозначения для регистров памяти со статическим (рис.1.8в) и с динамическим управлением (рис.1.8г).

Регистры памяти, обеспечивающие обмен параллельными двоичными кодами между микро-ЭВМ и какими-либо внешними устройствами, часто называют портами ввода-вывода. Микросхемы, выполняющие функции таких портов, часто можно перенастраивать с ввода на вывод или наоборот.

1.1.3.3. Оперативные запоминающие устройства

Оперативные запоминающие устройства (ОЗУ) предназначены для временного хранения множества двоичных слов. Также как и в ПЗУ двоичные слова хранятся здесь в отдельных ячейках памяти, к каждой из которых можно обратиться по адресу.

Читайте также: Выделите части из которых состоит магистраль шина

В отличие от ПЗУ, в ОЗУ обеспечено не только чтение хранящейся в ячейках информации, но и ее оперативное изменение в темпе вычислительного процесса.

Следует иметь в виду, что ОЗУ обеспечивают хранение записанной информации лишь во включенном состоянии. Отключение питания ведет к потере всей хранимой в ОЗУ информации.

Существуют два класса ОЗУ: статические и динамические.

Ячейку памяти статического ОЗУ можно рассматривать как регистр памяти с тремя состояниями выхода, дополненный простейшей логикой управления. Функциональная схема такой ячейки приведена на рис. 1.9.

Видео:Как работает компьютер? Шины адреса, управления и данных. Дешифрация. Взгляд изнутри!Скачать

Рис.1.9. Функциональная схема ячейки памяти статического ОЗУ

Ячейка имеет двунаправленные выводы D3 D0, по которым она либо принимает записываемое слово в режиме записи, либо выдает записанный код на выход режиме чтения. Ячейка запоминает входной код в регистре, если сигналы («») и («») равны соответственно 0 и 1. Если же = 1, а = 0, ячейка выдает на выводы D3 D0 слово, хранящееся в регистре. Как при записи, так и при чтении ячейка должна быть выбрана сигналами = = 0. В противном случае эти процессы будут блокированы.

Введем для рассмотренной ячейки памяти условное обозначение (рис.1.10).

Рис.1.10. Условное обозначение ячейки памяти статического ОЗУ

Объединив множество таких ячеек и дешифратор адреса, легко построить статическое ОЗУ произвольной емкости. Его функциональная схема представлена на рис.1.11. Все ячейки памяти этого ОЗУ одновременно получают сигналы «» (), «» ( или ) и сигнал выбора кристалла . Однако активна, то есть обменивается информацией с двунаправленной шиной D3 D0 только та ячейка, адрес которой распознал дешифратор адреса.

Рис.1.11. Функциональная схема статического ОЗУ

Динамическое ОЗУ может быть построено по тем же принципам, что и статическое, отличаясь лишь нижним уровнем памяти D триггером.

D триггер динамического ОЗУ представляет собой конденсатор небольшой емкости С0, управляемый электронным ключом на МОП транзисторе с индуцированным каналом. Релейно-контакторная модель такого триггера представлена на рис.1.12.

Если тактовый сигнал истинен (С = 1), контакт К1 замкнут и конденсатор С0 либо заряжается, либо разряжается до потенциала входа D.

При ложном значении тактового сигнала (С = 0), конденсатор С0 отключен от входа D и нагружен лишь на высокое входное сопротивление МОП повторителя.

Рис.1.12. Релейно-контактная модель D триггера динамического ОЗУ

Структура любой ЭВМ может быть представлена упрощенной функциональной схемой, приведенной на рис. 1.13. Схема включает в себя память, комбинационное АЛУ, устройство управления, устройства ввода-вывода.

Центральное место в структуре ЭВМ занимает память.

Именно здесь хранятся исходные данные для расчетов, программы обработки этих данных, а так же промежуточные и окончательные результаты вычислений.

Память ЭВМ обычно делится на три части: ОЗУ, ПЗУ и сверхоперативное запоминающее устройство (СОЗУ).

ОЗУ и ПЗУ имеют адресную организацию. Доступ к их ячейкам памяти для записи и чтения информации осуществляется с помощью многоразрядного адреса, воздействующего на цепи группового управления.

СОЗУ представляет собой набор быстродействующих регистров, имеющих индивидуальное управление. Эти регистры обеспечивают работу АЛУ, фиксируя его входные и выходные коды.

Кроме того, СОЗУ используется для временного хранения данных в процессе их обработки.

Выполнение вычислительной машиной арифметических и логических операций над двоичными кодами реализовано в АЛУ.

Общее управление всеми элементами ЭВМ и взаимную синхронизацию их работы обеспечивает устройство управления, исполняющее команды человека-пользователя. Это могут быть команды внешнего управления, поданные, например, с пульта, либо команды программы, заранее занесенные в память.

Команды программы представляют собой двоичные коды, которыми зашифрованы приказы, исполнить те или иные операции математической обработки данных, пересылки данных, управления ходом исполнения программы.

Устройство управления должно автоматически выбирать команду из соответствующей ячейки памяти, исполнять ее, выбирать следующую и т.д.

Обычно используется так называемый естественный порядок выполнения команд, когда последовательно друг за другом выполняются команды, занесенные в ячейки памяти с последовательно увеличивающимися адресами.

Рис.1.13. Функциональная схема ЭВМ

Адрес самой первой ячейки программы устанавливается при этом командой «сброс» внешнего управления.

Естественный порядок выполнения команд не требует каких-либо указаний в кодах команд, то есть используется по умолчанию.

Существуют специальные команды передачи управления, позволяющие нарушать естественный порядок либо безусловно, либо условно (в зависимости от признака результата выполненной АЛУ операции).

Такие команды каким-либо образом указывают устройству управления адрес следующей команды.

Обмен информацией между ЭВМ и внешней средой организуется через устройства ввода-вывода. Следует указать на возможность программного управления вводом-выводом и ввода-вывода по прерываниям.

В первом случае обмен информацией идет по инициативе и под управлением программы.

Во втором устройство ввода-вывода само запрашивает обслуживание под действием внешних сигналов. Устройство управления, реагируя на этот запрос, прерывает выполнение основной программы ЭВМ и запускает заранее подготовленную программу обслуживания устройства ввода-вывода (программу обработки прерывания). По завершении ввода-вывода под управлением программы обработки ЭВМ вновь возвращается к выполнению основной программы с точки прерывания.

Видео:Передача данных - шина SPIСкачать

Устройство управления, АЛУ и регистры СОЗУ принято объединять в единый конструктивный блок, называемый центральным процессором.

Рис.1.14. Функциональная схема ЭВМ, использующая центральный процессор

Вновь изобразим общую функциональную схему ЭВМ, используя понятие центрального процессора (рис.1.14). Эта схема наглядно иллюстрирует систему внутренних информационных связей между устройствами ЭВМ.

В ЭВМ, созданных до появления микропроцессоров, как правило, организовывалась одновременная и параллельная работа центрального процессора, АЛУ, устройств ввода-вывода, ОЗУ и ПЗУ. Такая организация позволяет обеспечить высокую производительность ЭВМ, однако требует наличия многочисленных соединений процессора с другими устройствами как одиночными проводниками, так многоразрядными шинами связи.

Обилие внешних связей препятствовало выполнению традиционных процессорных структур в виде одной или немногих интегральных схем, так как по условиям производства и применения микросхема не могла иметь слишком большое число выводов.

Поэтому при миниатюризации центрального процессора пришлось отказаться от жесткой, статической, выполненной раз и навсегда системы связей устройств вычислительной машины и организовать такую связь гибко, динамически с помощью общей для всех устройств шины (магистрали).

Функциональная схема ЭВМ с магистральной организацией приведена на рис.1.15.

Рис 1.15. Функциональная схема ЭВМ с магистральной организацией

Магистральная организация обеспечивает все связи между устройствами ЭВМ, предусмотренные общей функциональной схемой, но не параллельно, как в схеме (рис.1.15), а последовательно, с разделением во времени.

В каждый момент времени по общей шине взаимодействуют лишь два устройства вычислительной машины. Третье устройство отключено от шины с помощью выходов с открытым коллектором или тремя состояниями.

В рамках магистральной организации ЭВМ удалось разработать микроэлектронные центральные процессоры, реализованные на одной или нескольких микросхемах с числом выводов меньшим допустимого.

Такие микросхемы назвали микропроцессорами. ЭВМ с магистральной внутренней организацией и центральным процессором, построенным на микропроцессорах, стали называть микро-ЭВМ.

Магистральная организация микро-ЭВМ исключает параллельную обработку информации разными устройствами машины.

Поэтому производительность микро-ЭВМ оказывается относительно низкой. За малые размеры аппаратуры здесь заплачено ее быстродействием.

Следует указать, что за время, прошедшее с момента появления первого микропроцессора (1971 г.), технология производства и монтажа микросхем претерпела значительные изменения.

Соответственно увеличилось и допустимое число выводов микросхемы (от 40 в 1971 г. до нескольких сотен в настоящее время).

Однако это обстоятельство не стимулировало отказа от магистральной организации микро-ЭВМ, так как такая организация оказалась очень удобной для модернизации, изменения состава устройств микро-ЭВМ и приспособления микро-ЭВМ к запросам конкретного пользователя.

Говорят, что магистральная организация обеспечивает открытость и гибкость построения микро-ЭВМ. Это очень полезные качества и, поэтому, не смотря на появление технических возможностей повышения производительности за счет отказа от магистральной организации, производительность микро-ЭВМ повышают только за счет увеличения быстродействия элементов и совершенствования процесса обработки информации в микропроцессоре (конвейерная обработка, кэширование, применение сопроцессоров).

В состав простейшей микро-ЭВМ входят центральный процессор, ОЗУ и ПЗУ, порты ввода и вывода, а также дешифраторы, осуществляющие выбор запоминающего устройства и порта ввода вывода.

Построение микроЭВМ или, как часто говорят, ее «архитектуру» поясняет функциональная схема (рис.1.16).

Рис 1.16. Архитектура простейшей микро-ЭВМ

Рассматриваемая схема повторяет функциональную схему микроЭВМ с магистральной организацией (рис.1.15), отличаясь более подробной детализацией. Так общая магистраль оказывается представлена здесь совокупностью тр¨х специализированных шин: шины данных, шины адреса и шины управления.

Шина данных (ШД) является двунаправленной и предназначена для пересылки кодов обрабатываемых данных, а также машинных кодов команд между устройствами ЭВМ. Однонаправленная шина адреса (ША) нес¨т адрес (номер) той ячейки памяти или того порта ввода вывода, который взаимодействует с микропроцессором. Шина управления нес¨т сигналы управления, обеспечивающие правильное взаимодействие блоков микроЭВМ друг с другом и с внешней средой. На рис.1.16 эта шина представлена следующими сигналами:

Читайте также: Kia optima 2015 шины

MEMR «чтение из памяти»; сигнал подтверждает прием байта данных из памяти в один из регистров микропроцессора;

MEMW «запись в память»; сигнал извещает память о том, что микропроцессор выставил на шину данных байт, подлежащий записи в память;

I/OR «чтение из порта ввода»; сигнал подтверждает прием байта данных из порта ввода в определ¨нный регистр микропроцессора;

I/OW «запись в порт вывода»; сигнал извещает порты вывода о том, что микропроцессор выставил на шину данных байт, подлежащий выводу через какой-либо из портов.

Рассмотренный набор сигналов шины управления является типовым. В конкретной микро-ЭВМ он может быть, как расширен, так и сужен.

Сигнал RESET «сброс» является сигналом внешнего управления, он приводит микро ЭВМ в исходное стартовое состояние.

Центральный процессор (ЦП) микро ЭВМ выполнен на основе микропроцессора (МП). Кроме микропроцессора этот модуль содержит так называемые схемы обрамления. В состав обрамления входят разного рода вспомогательные устройства, обеспечивающие как работу микропроцессора, так и его связь с магистралью микроЭВМ.

Видео:Микро 80. Процессор. #1Скачать

Центральный процессор, ОЗУ, ПЗУ и порты ввода имеют выходы данных с тремя состояниями или открытым коллектором. Поэтому названные блоки могут либо отключаться (по выходу) от шины данных, либо, наоборот, захватывать эту шину. Центральный процессор управляет мультиплексированием шины данных по шине адреса с помощью дешифратора выбора ЗУ и дешифратора выбора порта. Дешифратор выбора ЗУ генерирует сигнал выбора соответствующего блока памяти (), анализируя старшие биты адреса ячейки памяти, выставленного микропроцессором на шине адреса. Младшие биты адреса обычно подаются параллельно на адресные входы всех блоков памяти. Рассмотренный метод гарантирует присвоение каждой из ячеек памяти своего единственного в системе, уникального адреса, а также непрерывность адресного пространства каждого из блоков памяти. Дешифратор выбора порта генерирует сигнал выбора соответствующего порта (), анализируя адрес порта, выставленный микропроцессором на шине адреса. Следует отметить, что сигналы выбора и используются в микро-ЭВМ не только для мультиплексирования шины данных (то есть для разрешения чтения из того или иного блока), но и для демультиплексирования, то есть для разрешения записи в соответствующий блок.

Представленная схема имеет некоторые отступления от общей функциональной схемы ЭВМ (рис.1.14). Так она не предусматривает прямого обмена информацией между портами ввода вывода и памятью, минуя центральный процессор (этот вид обмена называют прямым доступом к памяти (ПДП)), а также возможности прерывать выполнение основной программы в микро ЭВМ для обслуживания запросов внешних устройств. Реализация названных возможностей требует введения в функциональную схему дополнительных устройств контроллера ПДП и контроллера прерываний, связанных с соответствующими портами.

Будем считать, что простейшая микро-ЭВМ построена на основе микропроцессора INTEL8080A (отечественный аналог КР580ВМ80А), который примем в качестве учебного микропроцессора. Этот микропроцессор предназначен для арифметикологической обработки восьмиразрядных кодов. Он способен взаимодействовать с памятью общим объемом 64К, 256 портами ввода и 256 портами вывода. Взаимодействие обеспечивается двунаправленной восьмиразрядной шиной данных, шестнадцатиразрядной однонаправленной шиной адреса, а также рядом входных и выходных сигналов управления.

Построение микропроцессора или, как часто говорят, его «архитектуру» поясняет функциональная схема (рис.1.17).

Часто считают, что эта схема включает в себя три специализированных процессора: операционный, выполняющий всю арифметикологическую обработку; интерфейсный, обеспечивающий связь микропроцессора с внешней памятью и портами ввода вывода, и управляющий, обеспечивающий управление всеми узлами микропроцессора, прием и формирование управляющих сигналов.

Операционный процессор представлен здесь восьмиразрядным АЛУ и рядом восьмиразрядных регистров: регистром-аккумулятором А, регистром признаков или флагов F, регистрами общего назначения (РОН) B,C,D,E,H,L, вспомогательными регистрами Т, W, Z.

Все перечисленные регистры, кроме вспомогательных, являются программно доступными. Содержимое каждого из них доступно из программы пользователя, как для чтения, так и для записи.

Наиболее обширными функциями обладает аккумулятор А. Он используется микропроцессором при выполнении большинства команд. Регистры общего назначения могут использоваться для временного хранения как восьмиразрядных, так и шестнадцатиразрядных двоичных кодов. В последнем случае они объединяются в регистровые пары BC, DE, HL. Регистры А и F могут рассматриваться как регистровая пара PSW, которая хранит в себе слово состояния программы PSW. Регистры W и Z тоже могут объединяться в регистровую пару.

Остановимся подробнее на регистре признаков F. В нем запоминаются признаки результата, которые вырабатывает АЛУ микропроцессора при выполнении ряда команд. Формат регистра F представлен на рис.1.18.

Биты S, Z, AC, P, C называют признаками результата или флагами. Если признак равен 1, говорят, что он установлен. Если признак равен 0, говорят, что он сброшен.

S = 1, если результат отрицателен; Z = 1, если в результате получен нулевой код. C = 1, если при вычислении результата в АЛУ имел место перенос в старшие разряды или заем из старших разрядов. AC = 1, если при

Рис 1.17. Архитектура микропроцессора INTEL8080A

вычислении результата в АЛУ имел место межтетрадный перенос; P = 1, если код результата имеет четное число единичных бит.

Рис.1.18. Формат регистра признаков F

Интерфейсный процессор включает в себя шестнадцатиразрядные программно доступные регистры счетчик команд РС, указатель стека SP и программно недоступный регистр адреса. Работа этого процессора сводится к установке нужного кода на шине адреса с помощью регистра адреса.

Источниками устанавливаемого кода могут быть регистры РС, SP, регистровые пары BC, DE, HL, WZ.

Счетчик команд РС обеспечивает выборку из памяти команд программы. Обычно он содержит в себе адрес следующего байтового слова программы, подлежащего выборке. Сразу же после выборки очередного байтового слова содержимое РС увеличивается на единицу.

Указатель вершины стека (указатель стека) SP используется для организации в ОЗУ микроЭВМ, так называемой стековой памяти. Функции этого регистра и особенности стековой памяти подробно рассмотрены ниже.

Управляющий процессор состоит из регистра команд РГК и конечного автомата управления, генерирующего в ответ на команду микропрограмму ее исполнения. Этот процессор тактируется сигналами внешней синхронизации CLK1 и CLK2 и может устанавливаться в исходное состояние сигналом внешнего сброса RESET. Сигнал RESET также сбрасывает в ноль счетчик команд РС.

Управляющий процессор принимает и генерирует ряд сигналов управления. Наиболее важными из них являются импульсные сигналы DBIN «прием» и «». Первый сигнал подтверждает прием байта данных с шины данных в буферный регистр данных микропроцессора. Второй сигнал извещает внешние устройства о том, что микропроцессор выставил на шину данных очередной байтовый код.

Следует отметить, что пара сигналов DBIN и не дает возможности отличать обращения микропроцессора к памяти от обращений к портам ввода-вывода. Чтобы отличить эти обращения, приходится использовать дополнительную информацию о режиме работы микропроцессора. Такая информация содержится в так называемом слове состояния микропроцессора SW. Оно выдается управляющим процессором на шину данных в отведенные для этого интервалы времени и стробируется выходным сигналом синхронизации SYNC.

Исполнение программы в микропроцессоре может быть прервано по запросу внешнего устройства сигналом прерывания INT.

Выводы шин адреса и данных микропроцессора выполнены как выходы с тремя состояниями. Эти выходы могут переходить в высокоимпедансное состояние в результате выполнения некоторых команд или под воздействием внешних сигналов.

Функциональная схема центрального процессора, построенного на основе учебного микропроцессора, приведена на рис.1.19. На этой схеме:

МП микропроцессор (представлен множеством своих регистров);

ГТИ генератор тактовых импульсов;

ШФД шинный формирователь шины данных;

ШФА шинный формирователь шины адреса;

ШД восьмиразрядная шина данных микро ЭВМ;

ШДМ восьмиразрядная шина данных микропроцессора;

ША шестнадцатиразрядная шина адреса микро ЭВМ;

Видео:Цифровые интерфейсы и протоколыСкачать

ШАМ шестнадцатиразрядная шина адреса микропроцессора.

Рис.1.19.Архитектура центрального процессора

Тактовый генератор обеспечивает синхронизацию работы микропроцессора, шинные формирователи усиление по мощности сигналов шин, а системный контроллер считывает слово состояния процессора SW и формирует сигналы шины управления MEMR, MEMW, IOR и IOW из выходных сигналов микропроцессора DBIN и с учетом этого слова. Следует указать, что иногда включают в состав системного контроллера не только формирователь шины управления, но и шинный формирователь шины данных (показано пунктиром).

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле

- Правообладателям

- Политика конфиденциальности

🎥 Видео

Лекция 311. Шина USB - кодирование сигналовСкачать

Лекция 308. Шина I2CСкачать

Лекция 310. Шина USB - функциональная схемаСкачать

Что такое IP-адрес, маска, хост, адрес сети. ОсновыСкачать

Что такое ШИМ? Как ШИМ регулирует яркость, температуру, обороты двигателя и напряжение? Разбираемся!Скачать

Как работает ЭВМ? Собираем простейший компьютер на базе Z80, эмулятора ПЗУ и порта на D-триггере.Скачать

Системная шина процессораСкачать

Только не говори никому.. Как легко можно восстановить жидкокристаллический экран..Скачать

Шифраторы, дешифраторы. Назначение, принцип работы, типовые схемы.Скачать

Индикаторы. Разбираем и изобретаем! Часть 2.Скачать

Урок 24. Узнаём адреса устройств на шине I2CСкачать

Логический анализатор шины i2cСкачать

Ford Focus 3 - про этот пункт в меню все знают, но вдруг не все )Скачать

АПС Л14. ШиныСкачать