Интерфейс SPI — это один из самых популярных на сегодняшний день последовательных интерфейсов. Он был придуман фирмой Motorola и очень быстро завоевал популярность благодаря своей исключительной простоте и высокой скорости. При этом, SPI, наверное, нельзя назвать в полной мере интерфейсом, скорее это просто принцип связи, поскольку всё, что подразумевается под SPI, — это логика передачи данных между двумя устройствами («Ведущий»-«Ведомый»), физике же уделяется гораздо меньшее внимание, она реализуется, можно сказать, «по обстоятельствам», а никакого протокола нижнего уровня вообще нет, тут каждый производитель придумывает что-то своё.

Ну что ж, — с главного и начнём. Итак, в чём же тут логика? Логика в том, что данные передаются последовательно, побитно, при этом считывание и установка данных разделены во времени с помощью специального синхросигнала на специальной шине. Эта шина называется шиной тактирования (или шиной синхронизации), а суть разделения заключается в том, что считывание и установка данных происходят по противоположным фронтам генерируемых на шине синхроимпульсов. Такое, чётко разделённое во времени, чередование установок и считываний даёт возможность использовать один и тот же регистр и для приёма, и для передачи данных. Ранее (когда память была маленькой и дорогой, операционки хранились на дискетах, а по полям бегали мамонты ) это было серьёзным преимуществом, более того, именно под это на самом деле изначально и затачивался SPI, однако сейчас никаких проблем с обьёмом памяти нет и большинство устройств спокойно могут позволить себе иметь отдельные входной и выходной регистры.

Устройство, управляющее шиной тактирования (то есть генерирующее на ней синхроимпульсы), является «Ведущим» или «Мастером». Собственно, «Master» управляет всем обменом данными, — он решает: когда начинать обмен, когда заканчивать, сколько бит передать и т.д. Второе устройство, участвующее в обмене, является «Ведомым» или «Slave». В SPI, в отличии от, например, того же I2C, «Slave» совсем бесправен, он вообще никак не может влиять на шину тактирования и никак не может сообщить мастеру, что не успевает или, наоборот, что уже готов к обмену. То есть «Мастер» сам должен знать: когда, что и на какой скорости спросить у «Слэйва», чтобы тот смог ему ответить.

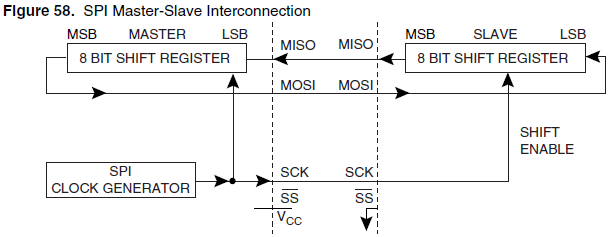

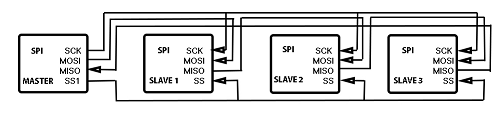

Всего, для полнодуплексного обмена (в обе стороны одновременно), в интерфейсе SPI используются 4 линии (смотрим рисунок): SCLK, MOSI, MISO и SS.

- SCLK — шина тактирования (на этой линии мастер генерирует синхроимпульсы)

- MOSI (Master Out, Slave In) — выход ведущего, вход ведомого (по этой линии мастер передаёт данные слэйву)

- MISO (Master In, Slave Out) — вход ведущего, выход ведомого (по этой линии мастер принимает данные от слэйва)

- SS (Slave Select) — выбор ведомого (с помощью этой линии мастер управляет сеансами обмена)

«1» и «0» кодируются уровнем напряжения на шинах данных (MOSI, MISO) в обычной положительной логике, то есть высокий уровень напряжения на шине соответствует «единице», а низкий уровень соответствует «нулю». При этом, то, каким образом организуется установка на шинах этих уровней, — нигде не оговаривается, то есть выходы передатчиков могут быть как «push-pull», так и «с открытым коллектором». Высокий уровень обычно соответствует напряжению питания микросхемы (то есть если мы имеем дело с пятивольтовыми микрухами, то высокий уровень — это напряжение, близкое к пяти вольтам, если речь идёт о микрухах, питающихся от 3,3В, то высокий уровень — это напряжение, близкое к 3,3В).

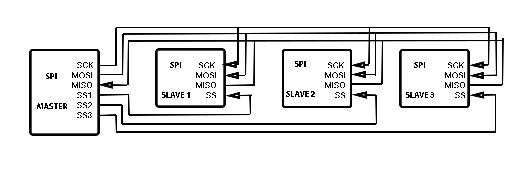

Сигнал SS отмечает начало и конец сеанса обмена. Этот сигнал обычно инверсный, то есть во время сеанса обмена данными мастер должен устанавливать на линии SS низкий уровень, а при отсутствии обмена — высокий. Наличие сигнала SS позволяет мастеру организовать подключение к нескольким слэйвам, используя один и тот же синхросигнал и одни и те же шины данных, без каких-либо дополнительных протоколов (вариант такого подключения показан на рисунке слева). Правда тут есть один минус: в этом случае мастеру придётся к каждому слэйву подключаться по отдельной линии SS (чтобы управлять сеансами обмена с каждым слэйвом независимо друг от друга), что увеличивает общее количество используемых проводов.

Читайте также: Лада шина в красноярске

Названия линий, в общем-то, не являются каким-то стандартом и могут отличаться в зависимости от производителя (например, вместо MOSI, MISO и SCLK линии могут называться DI, DO и SC, или SI, SO и CLK, линия SS может называться CS или RESET).

Более того, линий не обязательно должно быть четыре, — иногда их может быть только три, например, если данные передаются только в одном направлении или вместо двух однонаправленных шин данных используется одна двунаправленная. Очевидно, что в последнем случае возможен только полудуплексный обмен, то есть в один момент времени можно только передавать или только принимать данные (а передавать и принимать одновременно — нельзя).

То есть, ни по названию линий, ни по уровням напряжения на них, ни даже по их количеству, однозначно идентифицировать SPI нельзя, зато это отлично можно сделать по самому методу передачи данных, по тому как происходит их установка на шину и считывание.

Как я уже упоминал, — данные передаются побитно, а установка и чтение данных происходит по противоположным фронтам сигнала тактирования. Момент чтения данных в англоязычной литературе называется latch (фиксация, защёлкивание), а момент установки данных на шину — shift (сдвиг). Сдвигом момент установки называется в силу особенностей большинства последовательных интерфейсов. Обычно никто не передаёт данные по одному биту, как правило, их посылают пачками по 8 и более бит (размер пачки чаще всего всё же кратен восьми). В связи с этим, на выходе передатчика делают сдвиговый регистр, куда загружают сразу всю пачку передаваемых бит, при этом значение младшего или старшего бита этого сдвигового регистра устанавливается на шине данных (смотря как передаём — младшим или старшим битом вперёд), а для установки на шине следующего передаваемого бита — достаточно «сдвинуть» этот регистр. Так устроены передатчики и в SPI, и в I2C, и в привычном RS232, и много где ещё (так просто аппаратно удобнее). Ну, ладно, — вернёмся к нашему SPI.

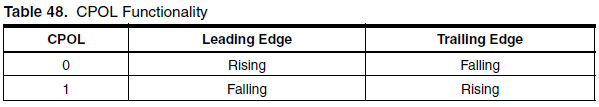

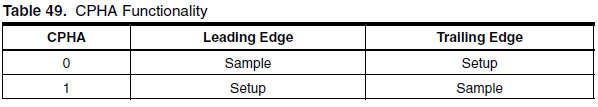

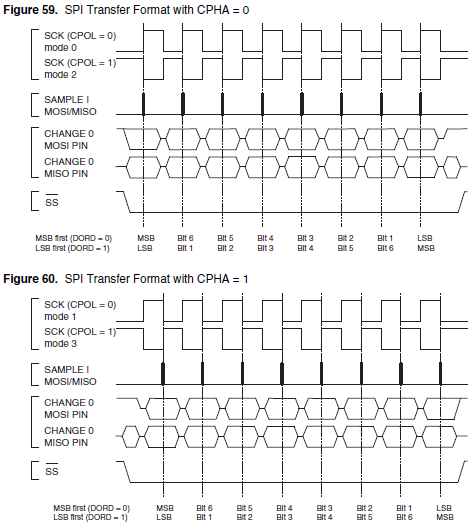

Логический уровень сигнала на шине тактирования в неактивном состоянии (когда нет передачи данных) называют полярностью и обозначают CPOL (то есть, если при отсутствии передачи на шине SCLK низкий уровень, то CPOL=0, а если в это время на шине SCLK высокий уровень, то CPOL=1). Порядок чередования считываний и сдвигов называют фазой и обозначают CPHA (если по первому фронту на SCLK происходит считывание, то CPHA=0, а если по первому фронту на SCLK происходит сдвиг, то CPHA=1).

В зависимости от сочетания значений CPOL и CPHA различают 4 режима работы интерфейса SPI, которые так и обозначают Mode0, Mode1, Mode2 и Mode3. Ниже приведена картинка, иллюстрирующая как происходит установка и чтение данных, в зависимости от выбранного режима.

Хотелось бы подчеркнуть, что SS — это именно линия управления сеансом обмена, а не просто линия выбора слэйва. Разница тут в том, что если считать SS просто линией выбора слэйва, то при подключении мастера к одному единственному слэйву возникает соблазн этой линией не управлять, а жёстко закоротить её на общий провод (типа чтоб слэйв всегда был выбран). Однако, логика слэйва обычно такова, что начало сеанса сопровождается различными подготовительными процедурами, такими как загрузка данных в выходной сдвиговый регистр и сброс счётчика импульсов, а выполнять какие-то действия (в соответствии с принятыми по SPI командами от мастера) слэйв начинает только после завершения сеанса обмена. Кроме того, вам ведь вполне может понадобиться несколько сеансов общения (например, если в первом сеансе вы посылаете команды, а в следующем хотите получить отчёт о результате их выполнения). Думаю понятно, что если жёстко притянуть линию SS к общему проводу, то ни о каком распознавании начала и конца сеанса обмена (начало распознаётся по спаду на линии SS, а конец — по подъёму) не может быть и речи, соответственно весь обмен данными будет нарушен. Так что важность сигнала SS не стоит недооценивать.

Читайте также: Давление в шинах для ниссан ноут

Ну и напоследок скажу, что наиболее популярными являются режимы Mode0 и Mode3.

Более подробно о том, как происходит обмен, что должен уметь SPI-мастер и как это программно реализовать на микроконтроллере (на примере контроллеров PIC и AVR) можно почитать в статье «Программная реализация ведущего шины SPI»

Видео:Передача данных - шина SPIСкачать

AVR Урок 24. Знакомство с шиной SPI

Видео:AVR 38# Последовательный интерфейс SPIСкачать

Знакомство с шиной SPI

Сегодня мы начинаем знакомство с шиной SPI (Serial Peripheral Interface).

Данная шина очень широко используется в электронике. Она очень удобна, являясь синхронной и полнодуплексной, поэтому, применяется во многих схемах для общения между различными цифровыми усторйствами – датчиками, контроллерами, драйверами и прочими устройствами.

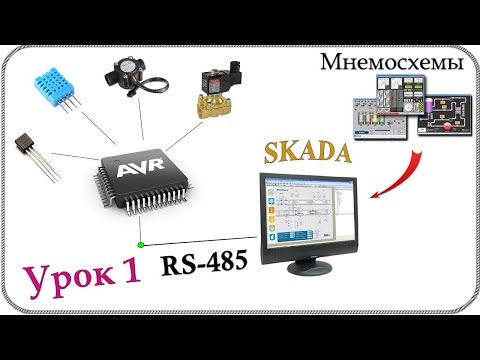

Ещё одним важнейшим фактором необходимости нашего с ней знакомства является то, что данная шина аппаратно организована в контроллерах AVR.

Мало того, хотим мы этого или не хотим, с интерфейсом SPI мы с вами общаемся уже давным давно, как только начали первый раз прошивать наш контроллер, так как прошивается он именно посредством данного интерфейса.

Поэтому хочется познакомиться с данной шиной поближе.

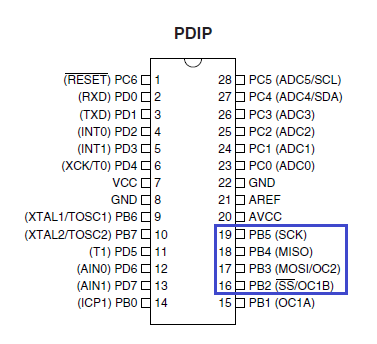

Давайте откроем техническую документацию на контроллер Atmega8, откроем страницу, где изображена распиновка данного контроллера и посмотрим, что от 16 до 19 ножки и находятся выводы шины SPI

Теперь немного подробнее о данных выводах

SS (chip select) – это ножка выбора устройства. Если на ведомом устройстве на данной ножке установится низкий уровень, то данное устройство будет откликаться и обмениваться информацией по шине SPI, если высокий, то не будет.

MOSI (master output slave input) – это ножка выхода ведущего устройства и входа ведомого устройства.

MISO (master input slave output) – наоборот, выход ведомого, вход ведущего.

SCK – ножка синхронизации. Ко всем устройствам, участвующим в обмене информации по данной шине, подаются синхроимпульсы с определённой частотой.

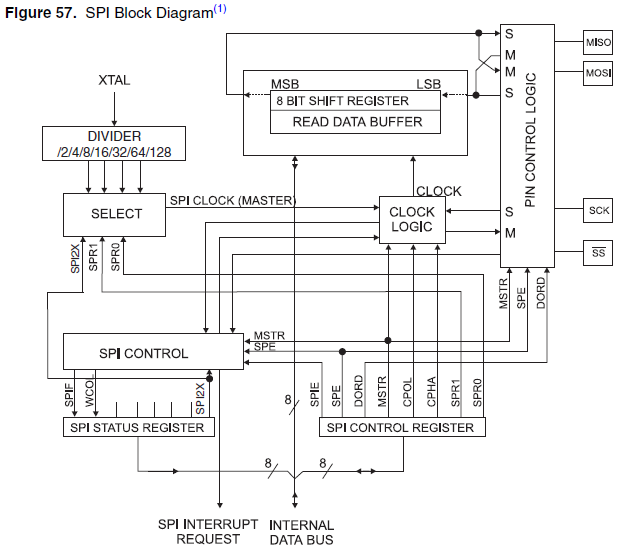

Вот схема реализации шины SPI в контроллере Atmega8

Как в любой шине, здесь имеется ряд регистров, в которых хранится определённая информация.

Нам интересен SHIFT REGISTER, через него и происходит обмен информации. Как только на ножке синхронизации будет определённый фронт, или нисходящий или восходящий, в зависимости от настройки, данные регистры у ведомого и ведущего устройства обменяются информацией, причем не всей информацией, а только одним битом. Данные регистры сдвинутся влево и старшие биты из каждого регистра уйдут в младшие биты такого же регистра сопряженного устройства. То есть ведомый передаст свой старший бит через ножку MOSI ведущему, который его запишет в освободившийся засчет сдвига влево младший бит, а ведомый свой вытесненный засчет сдвига передаст старший бит через ножку MISO в младший бит ведущего. Вот так и идёт обмен, то есть за 8 полных циклов тактирования они полностью обменяются байтами

Как только все 8 бит одного байта информации передадутся, определённый регистр нам просигнализирует о том, что данный процесс закончен. Вернее, определённый бит определённого регистра.

Также в блок-схеме мы видим делитель, на вход которого поступают тактовые импульсы и уже потом разделённые на определенное значение поступают по цепочке на ножку SCK и уже оттуда подаются на ведомое устройство на одноимённую ножку. Этим и обеспечивается синхронность работы устройств. Частота тактовых импульсов выбирается из наименьшей поддерживаемой всеми устройствами, участвующими в обмене.

Я говорю во множественном числе, так как может быть не только два устройства в данной цепи. Как это обеспечивается при условии, что у устройств нет никаких адресов, я сейчас и расскажу.

Существует несколько способов обена информацией между несколькими устройствами, то есть когда на одно ведущее устройство приходится несколько ведомых. Мы рассмотрим два самых распространённых из них.

Первый способ – радиальный (нажмите на картинку для увеличения изображения)

Читайте также: Шины для транспортных автомобилей

Здесь мастер направляет данные к определённому устройству, включая на ножке SS логический 0. При данном способе возможно выбрать только одно устройство, также потребуются несколько свободных ножек портов контроллера.

Есть ещё один интересный способ – кольцевой или каскадный (нажмите на картинку для увеличения изображения)

Здесь мы видим, что ножки выбора все запараллелены и обмен идёт по кругу. Тем самым скорость падает, засчёт того, что увеличивается круг передачи, но зато экономятся лапки портов.

Всё это мы в очередных занятиях изучим подробнее, когда будем использовать определённые устройства в наших проектах.

Ну, вроде со схемотехникой передачи данных по шине SPI мы разобрались.

Теперь разберёмся, как же данным процессом управлять на уровне аппаратных регистров контроллера AVR.

Данные регистры мы видим в блок-схеме выше на странице.

У Atmega8 существуют следующие регистры для обслуживания шины SPI.

SPDR (SPI Data Register) – регистр данных, в блок-схеме это DATA BUFFER. В этот регистр мы будем заносить байт для последующей его передачи на ведомое устройство и из него же будем читать байт информации, пришедший с ведомого устройства. Также не обязательно что у нас контроллер будет ведущим устройством. Впоследствии мы соберём схему из двух контроллеров, один из которых будет ведомым. Так что именно в этом регистре будет находиться байт и для отправки и для приёма.

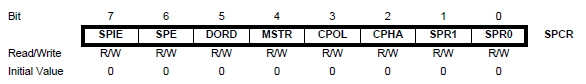

SPCR (SPI Control Register) – управляющий регистр

Данный регистр включает в себя следующие биты:

SPIE (SPI Interrupt Enable) – бит, который разрешает прерывания.

SPE (SPI Enable) – бит, включающий шину SPI.

DORD (Data Order) – бит, устанавливающий порядок отправки бит, Если он установлен в 1, то первым отправляется младший бит, если в 0 – старший.

MSTR (Master/Slave Select) – бит, который назначает устройство ведущим либо ведомым. При установке данного бита 1 устройство будет ведущим.

CPOL (Clock Polarity) – полярность синхронизации, определяет, при каком фронте синхронизирующего импульса будет инициироваться режим ожидания

Если данный бит в 1, то режим ожидания будет у нас при восходящем фронте, а если в 0, то при нисходящем.

CPHA (Clock Phase) – бит, отвечающий за фазу тактирования, то есть по какому именно фронту будет осуществляться передача бита.

Посмотрим диаграммы передачи данных в зависимости от установки CPOL и CPHA

Вот такая вот интересная зависимость. Порой мы иногда видим в технических характеристиках какого нибудь устройства, что оно, к примеру, может работать в режиме SPI 0:0 и SPI 1:1, вот это как раз и касается настройки этих битов.

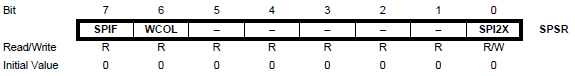

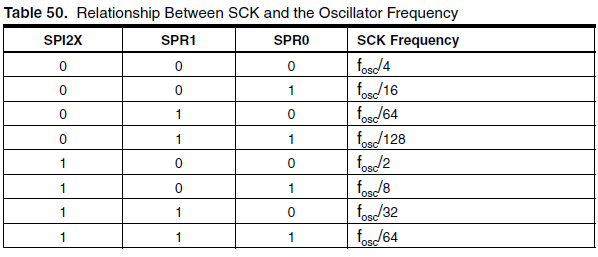

SPR1, SPR0 (SPI Clock Rate Select) – это биты, отвечающие за значение делителя частоты синхронизации, работают совместно с битом SPI2X, находящемся в регистре статуса. Он также управляющий, так как восьми бит в управляющем регистре под все настройки не хватило, а в статусном много свободных.

SPSR (SPI Status Register) – статусный регистр

SPI2X (Double SPI Speed Bit) – бит, удваивающий скорость, работающий совместно с битами SPR1 и SPR0 управляющего регистра.

Посмотрим зависимость частоты от данных трёх битов

SPIF (SPI Interrupt Flag) – Флаг прерывания. Установку данного бита в единицу мы ждём. когда принимаем байт. Как только байт от другого устройства появится полностью у нас в буфере, то данный флаг установится. Данный флаг работает только в случае установки бита, разрешающего прерывания, а также разрешения глобальных прерываний.

WCOL (Write COLlision Flag) – флаг конфликта, или коллизий, установится в том случае, если во время передачи данных будет конфликт битов, если во время передачи данных выполнится попытка записи в регистр данных.

Ну теперь мы, можно сказать, немного познакомились с интерфейсом SPI.

В следующем занятии мы уже попытаемся данную шину использовать на практике, подключив к нашему контроллеру какое-нибдуь ведомое устройство.

Купить программатор можно здесь (продавец надёжный) USBASP USBISP 2.0

Смотреть ВИДЕОУРОК (нажмите на картинку)

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле

🎦 Видео

Лекция 307. Интерфейс SPIСкачать

Лекция "Интерфейсы (часть I). RS-232/422/485. SPI"Скачать

Прерывания в микроконтроллерах? Что это, и как с ними работать. Краткий ликбез.Скачать

Лекция 308. Шина I2CСкачать

Цифровые интерфейсы и протоколыСкачать

SPI интерфейс на микроконтроллере. "урок 18"Скачать

лекция 349 Atmega8 интерфейс SPIСкачать

Интерфейсы :: SPI :: Часть 1:: Общие сведенияСкачать

Лекция 309. 1-wire интерфейсСкачать

интерфейс rs 485 и микроконтроллерыСкачать

Цифровые интерфейсы: 04. SPI (Периферийный последовательный интерфейс)Скачать

SPI интерфейс в микроконтроллерах AVRСкачать

О шине SPI и библитоеке SPI. Arduino.Скачать

Видеоуроки по Arduino. Интерфейсы SPI (8-я серия, ч1)Скачать