Компьютерная Энциклопедия

Компьютерная Энциклопедия- Архитектура ЭВМ

- Компоненты ПК

- Интерфейсы

- Мини блог

- Самое читаемое

- Системные платы

- Шина процессора

- Общие сведения о шине процессора

- Шина процессора на основе hub-архитектуры

- Пропускная способность шины процессора

- Первый взгляд на DDR3

- DDR3: некоторые технические сведения

- Табл. 1. Скоростные характеристики модулей памяти DDR3

- Конфигурация тестового стенда

- DDR3: первые результаты реального тестирования

- Табл. 2. Реальная пропускная способность памяти DDR2 и DDR3 в одноканальном режиме

- Заключение

Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

Системные платы

Шина процессора

Общие сведения о шине процессора

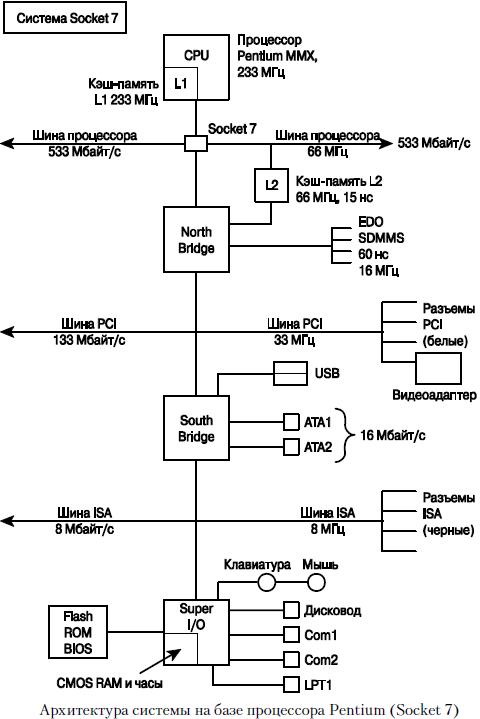

Шина процессора — соединяет процессор с северным мостом или контроллером памяти MCH. Она работает на частотах 66–200 МГц и используется для передачи данных между процессором и основной системной шиной или между процессором и внешней кэш-памятью в системах на базе процессоров пятого поколения. Схема взаимодействия шин в типичном компьютере на базе процессора Pentium (Socket 7) показано на рисунке.

На этом рисунке четко видна трехуровневая архитектура, в которой на самом верхнем уровне иерархии находится шина процессора, далее следует шина PCI и за ней шина ISA. Большинство компонентов системы подключается к одной из этих трех шин.

В системах, созданных на основе процессоров Socket 7, внешняя кэш-память второго уровня установлена на системной плате и соединена с шиной процессора, которая работает на частоте системной платы (обычно от 66 до 100 МГц). Таким образом, при появлении процессоров Socket 7 с более высокой тактовой частотой рабочая частота кэш-памяти осталась равной сравнительно низкой частоте системной платы. Например, в наиболее быстродействующих системах Intel Socket 7 частота процессора равна 233 МГц, а частота шины процессора при множителе 3,5х достигает только 66 МГц. Следовательно, кэш-память второго уровня также работает на частоте 66 МГц. Возьмем, например, систему Socket 7, использующую процессоры AMD K6-2 550, работающие на частоте 550 МГц: при множителе 5,5х ч астота шины процессора равна 100 МГц. Следовательно, в этих системах частота кэш-памяти второго уровня достигает только 100 МГц.

Проблема медленной кэш-памяти второго уровня была решена в процессорах класса P6, таких как Pentium Pro, Pentium II, Celeron, Pentium III, а также AMD Athlon и Duron. В этих процессорах использовались разъемы Socket 8, Slot 1, Slot 2, Slot A, Socket A или Socket 370. Кроме того, кэш-память второго уровня была перенесена с системной платы непосредственно в процессор и соединена с ним с помощью встроенной шины. Теперь эта шина стала называться шиной переднего плана (Front-Side Bus — FSB), однако я, согласно устоявшейся традиции, продолжаю называть ее шиной процессора.

Включение кэш-памяти второго уровня в процессор позволило значительно повысить ее скорость. В современных процессорах кэш-память расположена непосредственно в кристалле процессора, т.е. работает с частотой процессора. В более ранних версиях кэш-память второгоуровня находилась в отдельной микросхеме, интегрированной в корпус процессора, и работала с частотой, равной 1/2, 2/5 или 1/3 частоты процессора. Однако даже в этом случае скорость интегрированной кэш-памяти была значительно выше, чем скорость внешнего кэша, ограниченного частотой системной платы Socket 7.

В системах Slot 1 кэш-память второго уровня была встроена в процессор, но работала только на его половинной частоте. Повышение частоты шины процессора с 66 до 100 МГц привело к увеличению пропускной способности до 800 Мбайт/с. Следует отметить, что в большинство систем была включена поддержка AGP. Частота стандартного интерфейса AGP равна 66 МГц (т.е. вдвое больше скорости PCI), но большинство систем поддерживают порт AGP 2x, быстродействие которого вдвое выше стандартного AGP, что приводит к увеличению пропускной способности до 533 Мбайт/с. Кроме того, в этих системах обычно использовались модули памяти PC100 SDRAM DIMM, скорость передачи данных которых равна 800 Мбайт/с.

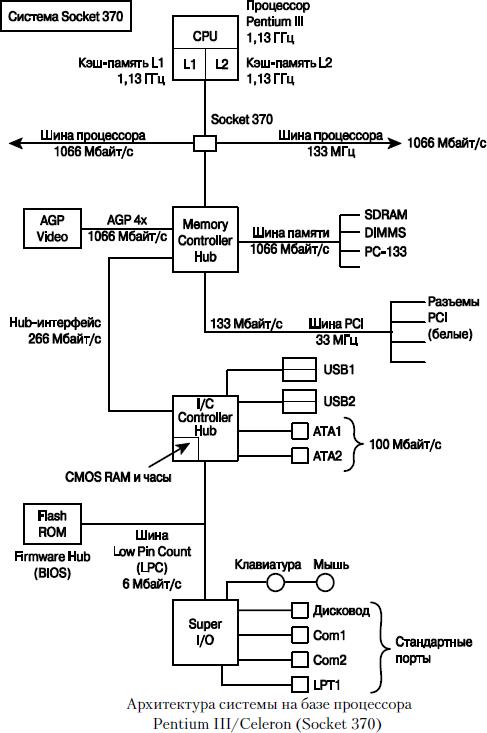

В системах Pentium III и Celeron разъем Slot 1 уступил место гнезду Socket 370. Это было связано главным образом с тем, что более современные процессоры включают в себя встроенную кэш-память второго уровня (работающую на полной частоте ядра), а значит, исчезла потребность в дорогом корпусе, содержащем несколько микросхем. Скорость шины процессора увеличилась до 133 МГц, что повлекло за собой повышение пропускной способности до 1066 Мбайт/с. В современных системах используется уже AGP 4x со скоростью передачи данных 1066 Мбайт/с.

Шина процессора на основе hub-архитектуры

Обратите внимание на hub-архитектуру Intel, используемую вместо традиционной архитектуры “северный/южный мост”. В этой конструкции основное соединение между компонентами набора микросхем перенесено в выделенный hub-интерфейс со скоростью передачи данных 266 Мбайт/с (вдвое больше, чем у шины PCI), что позволило устройствам PCI использовать полную, без учета южного моста, пропускную способность шины PCI. Кроме того, микросхема Flash ROM BIOS, называемая теперь Firmware Hub, соединяется с системой через шину LPC. Как уже отмечалось, в архитектуре “северный/южный мост” для этого использовалась микросхема Super I/O. В большинстве систем для соединения микросхемы Super I/O вместо шины ISA теперь используется шина LPC. При этом hub-архитектура позволяет отказаться от использования Super I/O. Порты, поддерживаемые микросхемой Super I/O, называются традиционными (legacy), поэтому конструкция без Super I/O получила название нетрадиционной (legacy-free) системы. В такой системе устройства, использующие стандартные порты, должны быть подсоединены к компьютеру с помощью шины USB. В этих системах обычно используются два контроллера и до четырех общих портов (дополнительные порты могут быть подключены к узлам USB).

В системах, созданных на базе процессоров AMD, применена конструкция Socket A, в которой используются более быстрые по сравнению с Socket 370 процессор и шины памяти, но все еще сохраняется конструкция “северный/южный мост”. Обратите внимание на быстродействующую шину процессора, частота которой достигает 333 МГц (пропускная способность — 2664 Мбайт/с), а также на используемые модули памяти DDR SDRAM DIMM, которые поддерживают такую же пропускную способность (т.е. 2664 Мбайт/с). Также следует заметить, что большинство южных мостов включает в себя функции, свойственные микросхемам Super I/O. Эти микросхемы получили название Super South Bridge (суперъюжный мост).

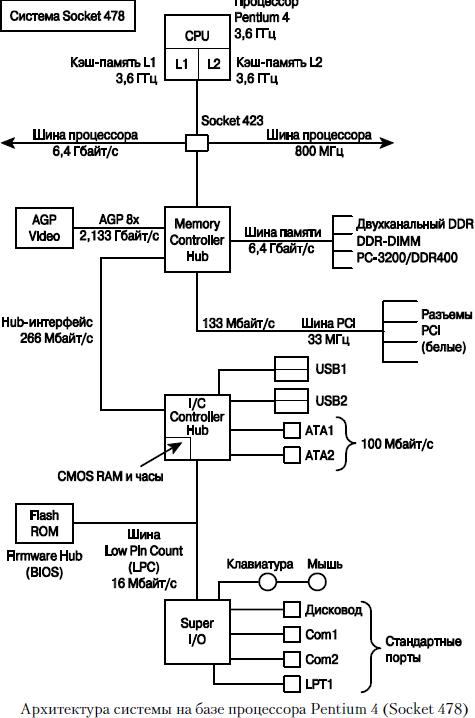

Система Pentium 4 (Socket 423 или Socket 478), созданная на основе hub-архитектуры, показана на рисунке ниже. Особенностью этой конструкции является шина процессора с тактовой частотой 400/533/800 МГц и пропускной способностью соответственно 3200/4266/6400 Мбайт/с. Сегодня это самая быстродействующая шина. Также обратите внимание на двухканальные модули PC3200 (DDR400), пропускная способность которых (3200 Мбайт/с) соответствует пропускной способности шины процессора, что позволяет максимально повысить производительность системы. В более производительных системах, включающих в себя шину с пропускной способностью 6400 Мбайт/с, используются двухканальные модули DDR400 с тактовой частотой 400 МГц, благодаря чему общая пропускная способность шины памяти достигает 6400 Мбайт/с. Процессоры с частотой шины 533 МГц могут использовать парные модули памяти (PC2100/DDR266 или PC2700/DDR333) в двухканальном режиме для достижения пропускной способности шины памяти 4266 Мбайт/с. Соответствие пропускной способности шины памяти рабочим параметрам шины процессора является условием оптимальной работы.

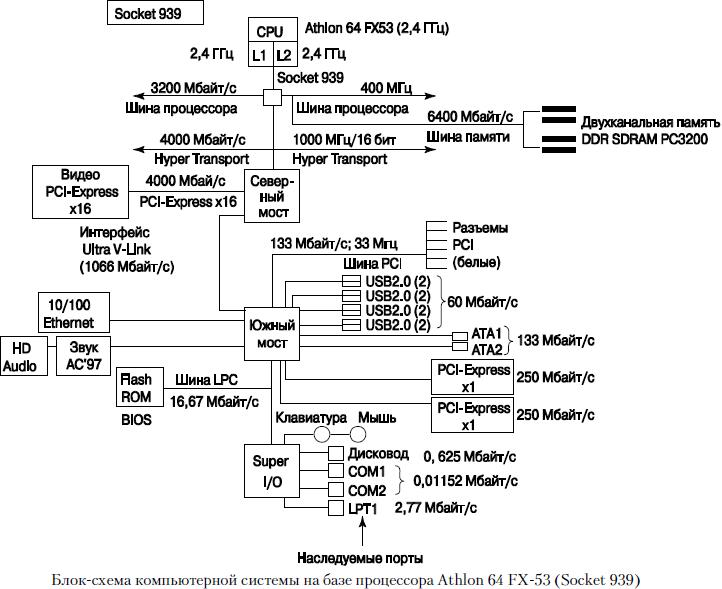

Процессор Athlon 64, независимо от типа гнезда (Socket 754, Socket 939 или Socket 940), использует высокоскоростную архитектуру HyperTransport для взаимодействия с северным мостом или микросхемой AGP Graphics Tunnel. Первые наборы микросхем для процессоров Athlon 64 использовали версию шины HyperTransport с параметрами 16 бит/800 МГц, однако последующие модели, предназначенные для поддержки процессоров Athlon 64 и Athlon 64 FX в исполнении Socket 939, используют более быструю версию шины HyperTransport с параметрами 16 бит/1 ГГц.

Наиболее заметным отличием архитектуры Athlon 64 от всех остальных архитектур ПК является размещение контроллера памяти не в микросхеме северного моста (или микросхеме MCH/GMCH), а в самом процессоре. Процессоры Athlon 64/FX/Opteron оснащены встроенным контроллером памяти. Благодаря этому исключаются многие “узкие места”, связанные с внешним контроллером памяти, что положительно сказывается на общем быстродействии системы. Главный недостаток этого подхода состоит в том, что для добавления поддержки новых технологий, например памяти DDR2, придется изменять архитектуру процессора.

Поскольку шина процессора должна обмениваться информацией с процессором с максимально возможной скоростью, в компьютере она функционирует намного быстрее любой другой шины. Сигнальные линии (линии электрической связи), представляющие шину, предназначены для передачи данных, адресов и сигналов управления между отдельными компонентами компьютера. Большинство процессоров Pentium имеют 64-разрядную шину данных, поэтому за один цикл по шине процессора передается 64 бит данных (8 байт).

Тактовая частота , используемая для передачи данных по шине процессора, соответствует его внешней частоте. Это следует учитывать, поскольку в большинстве процессоров внутренняя тактовая частота, определяющая скорость работы внутренних блоков, может превышать внешнюю. Например, процессор AMD Athlon 64 3800+ работает с внутренней тактовой частотой 2,4 ГГц, однако внешняя частота составляет всего 400 МГц, в то время как процессор Pentium 4 с внутренней частотой 3,4 ГГц имеет внешнюю частоту, равную 800 МГц. В новых системах реальная частота процессора зависит от множителя шины процессора (2x, 2,5x, 3x и выше). Шина FSB, подключенная к процессору, по каждой линии данных может передавать один бит данных в течение одного или двух периодов тактовой частоты. Таким образом, в компьютерах с современными процессорами за один такт передается 64 бит.

Пропускная способность шины процессора

Для определения скорости передачи данных по шине процессора необходимо умножить разрядность шины данных (64 бит, или 8 байт, для Celeron/Pentium III/4 или Athlon/Duron/ Athlon XP/Athlon 64) на тактовую частоту шины (она равна базовой (внешней) тактовой частоте процессора).

Например, при использовании процессора Pentium 4 с тактовой частотой 3,6 ГГц, установленного на системной плате, частота которой равна 800 МГц, максимальная мгновенная скорость передачи данных будет достигать примерно 6400 Мбайт/с. Этот результат можно получить, используя следующую формулу:

800 МГц × 8 байт (64 бит) = 6400 Мбайт/с.

Для более медленной системы Pentium 4:

533,33 МГц × 8 байт (64 бит) = 4266 Мбайт/с;

400 МГц × 8 байт (64 бит) = 3200 Мбайт/с.

Для системы Athlon XP (Socket A) получится следующее:

400 МГц × 8 байт (64 бит) = 3200 Мбайт/с;

333 МГц × 8 байт (64 бит) = 2667 Мбайт/с;

266,66 МГц × 8 байт (64 бит) = 2133 Мбайт/с.

Читайте также: Основные неисправности can шины

Для системы Pentium III (Socket 370):

133,33 МГц × 8 байт (64 бит) = 1066 Мбайт/с;

100 МГц × 8 байт (64 бит) = 800 Мбайт/с.

Максимальную скорость передачи данных называют также пропускной способностью шины (bandwidth) процессора.

Первый взгляд на DDR3

По материалам наших ежегодных iТогов по десктопной оперативной памяти (см., например, материалы за 2004, 2005 и 2006 год) легко заметить, что наиболее приоритетным направлением развития технологии оперативной памяти DDR SDRAM уже который год подряд является дальнейшее увеличение ее пропускной способности (напрямую зависящей от ее тактовой частоты) и снижение задержек. На втором месте по важности, пожалуй, располагается уменьшение ее энергопотребления и, наконец, увеличение емкости отдельных компонентов (микросхем) и модулей памяти в целом. По-видимому, реализация первого направления считается наиболее важной, в связи с чем происходит практически непрерывно (в рамках одной и той же ступени эволюции технологии — например, плавный переход от DDR2-400 к DDR2-800 и выше), тогда как реализация остальных из перечисленных выше задач, как правило, требует определенного эволюционного скачка в технологическом развитии (например, перехода от технологии DDR к технологии DDR2). Действительно, простое увеличение частоты шины памяти сказывается на ее энергопотреблении явно не положительным образом, поэтому для решения задачи снижения энергопотребления требуются иные подходы. Более того, ситуация, как правило, осложняется тем, что решение этой задачи несколько противоречит «генеральной линии» развития технологий памяти, которая, напомним, заключается в достижении все больших пропускных способностей (частот) и все меньших задержек. И правда, хорошо известно, что первые варианты памяти типа DDR2 ощутимо проигрывали их «равночастотным» аналогам типа DDR по задержкам. Тем не менее, неограниченный рост частот (и снижение задержек) в рамках одной и той же технологии памяти невозможен — он ограничен вполне определенными физическими причинами (прежде всего, тепловыделением), поэтому «эволюционные скачки» в развитии технологий памяти все же необходимы, и обусловлены они не только заботой о меньшем потреблении энергии.

Так обстояло дело при первом эволюционном скачке в развитии технологий памяти DDR SDRAM — переходе от DDR к DDR2. Первые образцы DDR функционировали на частоте всего 100 МГц (и имели рейтинг DDR-200), затем частота постепенно увеличилась до 200 МГц (DDR-400). Происходило одновременное уменьшение задержек — первоначальные схемы таймингов вида 3-3-3-8 сменились весьма низкими схемами вида 2-2-2-5. Затем появились и более высокочастотные модули памяти DDR (вплоть до 300 МГц, т.е. DDR-600), однако официально они так и не были приняты стандартом JEDEC. Увеличение частоты модулей памяти, либо снижение задержек требовало повышения питающего напряжения со стандартного уровня 2.5 В до значений порядка 2.85 В, проблема избыточного тепловыделения решалась, как правило, применением обычных теплоотводов.

Когда дальнейшее увеличение тактовых частот памяти DDR оказалось практически невозможным, на рынке десктопной оперативной памяти появилось новое, второе поколение памяти DDR SDRAM — память DDR2, которая постепенно начала доказывать свою конкурентоспособность и медленно, но верно вытеснять «старое» поколение памяти DDR. Первоначальные варианты DDR2 были представлены частотами 200 МГц (DDR2-400) и 266 МГц (DDR2-533) — так сказать, DDR2 начала свое развитие там, где (официально) закончила свое развитие DDR. Более того, первоначальный стандарт DDR2 предусматривал гораздо более высокочастотные варианты, по сравнению с привычной DDR — 333-МГц модули типа DDR2-667 и 400-МГц вариант DDR2-800. При этом микросхемы DDR2 были основаны на новом технологическом процессе, позволяющем использовать питающее напряжение всего 1.8 В (что явилось одним из факторов снижения их энергопотребления) и достигать более высоких емкостей компонентов и, следовательно, модулей памяти.

Благодаря чему удалось достичь (сначала — в теории, а затем — и на практике) больших тактовых частот (а следовательно, и пропускных способностей) памяти DDR2 при одновременном уменьшении ее энергопотребления, по сравнению с DDR? Были ли при этом у DDR2 только одни преимущества перед DDR, или имелись и недостатки? Чтобы ответить на эти вопросы, позволим себе сделать краткий экскурс в теорию. Для начала, рассмотрим предельно упрощенную схему функционирования памяти типа DDR (рис. 1).

Передача данных от микросхем памяти модуля к контроллеру памяти по внешней шине данных осуществляется по обоим полупериодам синхросигнала (восходящему — «фронту», и нисходящему — «срезу»). В этом и заключается суть технологии «Double Data Rate», именно поэтому «рейтинг», или «эффективная» частота памяти DDR всегда является удвоенной (например, DDR-400 при 200-МГц частоте внешней шины данных). Итак, «эффективная» частота внешней шины данных памяти DDR-400 составляет 400 МГц, тогда как ее истинная частота, или частота буферов ввода-вывода, составляет 200 МГц. В устройствах памяти первого поколения DDR внутренняя частота функционирования микросхем памяти приравнена к истинной частоте внешней шины (частоте буферов ввода-вывода) и составляет 200 МГц для рассматриваемой микросхемы памяти DDR-400. При этом совершенно очевидно, что для того, чтобы передавать по 1 биту данных за такт (по каждой линии данных) по внешней шине с «эффективной» частотой 400 МГц, за один такт внутренней 200-МГц шины данных необходимо передать 2 бита данных. Иными словами, можно сказать, что при прочих равных условиях внутренняя шина данных должна быть вдвое шире по сравнению с внешней шиной данных. Такая схема доступа к данным называется схемой «2n-предвыборки» (2n-prefetch).

Наиболее естественным путем решения проблемы достижения более высоких тактовых частот при переходе от DDR к DDR2 явилось снижение тактовой частоты внутренней шины данных вдвое по отношению к реальной тактовой частоте внешней шины данных (частоте буферов ввода-вывода). Так, в рассматриваемом примере микросхем памяти DDR2-800 (рис. 2) частота буферов ввода-вывода составляет 400 МГц, а «эффективная» частота внешней шины данных — 800 МГц (поскольку сущность технологии Double Data Rate остается в силе — данные по-прежнему передаются как по восходящему, так и по нисходящему полупериоду синхросигнала). При этом частота внутренней шины данных составляет всего 200 МГц, поэтому для передачи 1 бита (по каждой линии данных) за такт внешней шины данных с эффективной частотой 800 МГц на каждом такте 200-МГц внутренней шины данных требуется передача уже 4 бит данных. Иными словами, внутренняя шина данных микросхемы памяти DDR2 должна быть в 4 раза шире по сравнению с ее внешней шиной. Такая схема доступа к данным, реализованная в DDR2, называется схемой «4n-предвыборки» (4n-prefetch). Ее преимущества перед схемой 2n-prefetch, реализованной в DDR, очевидны. С одной стороны, для достижения равной пиковой пропускной способности можно использовать вдвое меньшую внутреннюю частоту микросхем памяти (200 МГц для DDR-400 и всего 100 МГц для DDR2-400, что позволяет значительно снизить энергопотребление). С другой стороны, при равной внутренней частоте функционирования микросхем DDR и DDR2 (200 МГц как для DDR-400, так и DDR2-800) последние будут характеризоваться вдвое большей теоретической пропускной способностью. Но очевидны и недостатки — функционирование микросхем DDR2 на вдвое меньшей частоте (в условиях равенства теоретической пропускной способности устройств DDR и DDR2) и использование более сложной схемы преобразования «4-1» приводит к ощутимому возрастанию задержек, что и наблюдалось на практике в ходе исследования первых образцов модулей памяти DDR2.

Естественно, применение схемы 4n-prefetch — не единственное нововведение в DDR2, однако оно является наиболее значимым отличием от предыдущего поколения памяти DDR, поэтому достаточно для нашего краткого рассмотрения. За более полными подробностями относительно DDR2 мы рекомендуем обратиться к нашей статье «DDR2 — грядущая замена DDR. Теоретические основы и первые результаты низкоуровневого тестирования».

Дальнейшее развитие технологии памяти DDR2 явилось существенно аналогичным развитию ее предыдущего поколения, памяти DDR. А именно, были достигнуты частоты в 333 и 400 МГц (т.е. реализованы официальные стандарты DDR2-667 и DDR2-800). Были значительно снижены задержки, даже официально появилась новая версия стандарта JEDEC (JESD79-2B), допускающая снижение схемы таймингов от 4-4-4 до 3-3-3 — для DDR2-533, от 5-5-5 до 4-4-4 — для DDR2-667, от 6-6-6 до 5-5-5 и даже 4-4-4 — для DDR2-800. Конечно же, следом появились и «нестандартные» разновидности DDR2, по своей частоте выходящие далеко за пределы спецификации JEDEC — вплоть до 625 МГц («DDR2-1250») при схеме таймингов 5-5-5, либо «стандартные» DDR2-800, но с экстремально низкими схемами таймингов вроде 3-3-3. Как и прежде, для достижения таких рекордов потребовалось значительное поднятие питающего напряжения модулей со стандартного уровня 1.8 В до экстремально высоких уровней порядка 2.4 В (что совсем немного уступает стандартному значению предыдущего поколения памяти DDR — 2.5 В). Разумеется, это потребовало применения более «продвинутых» способов отвода тепла от микросхем памяти — как оригинальных, патентованных фирменных конструкций теплоотводов, так и применения внешнего активного охлаждения.

Тем не менее, как и в случае с прошлым поколением памяти DDR, на сегодняшний день предел технологии памяти DDR2 (по частоте, задержкам и значительно возросшему тепловыделению вследствие значительного увеличения питающего напряжения) практически достигнут. Поэтому уже сегодня вполне закономерно ожидать очередной «эволюционный скачок» технологии памяти DDR SDRAM — переход от памяти стандарта DDR2 к новому стандарту DDR3.

Нетрудно догадаться, что основной принцип, лежащий в основе перехода от DDR2 к DDR3, в точности повторяет рассмотренную выше идею, заложенную при переходе от DDR к DDR2. А именно, DDR3 — это «все та же DDR SDRAM», т.е. передача данных по-прежнему осуществляется по обоим полупериодам синхросигнала на удвоенной «эффективной» частоте относительно собственной частоты шины памяти. Только рейтинги производительности выросли в 2 раза, по сравнению с DDR2 — типичными скоростными категориями памяти нового стандарта DDR3 будут являться разновидности от DDR3-800 до DDR3-1600 (а возможно, и выше). Очередное увеличение теоретической пропускной способности компонентов памяти в 2 раза вновь связано со снижением их внутренней частоты функционирования во столько же раз. Поэтому отныне, для достижения темпа передачи данных со скоростью 1 бит/такт по каждой линии внешней шины данных с «эффективной» частотой в 1600 МГц (как в примере, рассмотренном на рис. 3) используемые 200-МГц микросхемы должны передавать по 8 бит данных за каждый «свой» такт. Т.е. ширина внутренней шины данных микросхем памяти окажется уже в 8 раз больше по сравнению с шириной их внешней шины. Очевидно, такая схема передачи данных с рассмотренным преобразованием типа «8-1» будет называться схемой «8n-предвыборки» (8n-prefetch). Преимущества при переходе от DDR2 к DDR3 будут теми же, что и при состоявшемся ранее переходе от DDR к DDR2: с одной стороны, это снижение энергопотребления компонентов в условиях равенства их пиковой пропускной способности (DDR3-800 против DDR2-800), с другой стороны — возможность дальнейшего наращивания тактовой частоты и теоретической пропускной способности при сохранении прежнего уровня «внутренней» частоты компонентов (DDR3-1600 против DDR2-800). Теми же будут и недостатки — дальнейший разрыв между «внутренней» и «внешней» частотой шин компонентов памяти будет приводить к еще большим задержкам. Резонно ожидать, что относительное увеличение последних, при переходе от DDR2 к равночастотной DDR3, будет примерно таким же, как и при переходе от DDR к равночастотной DDR2.

Читайте также: Размер шин по марке автомобиля хендай гетц

Что ж, перейдем к несколько более детальному рассмотрению нового поколения микросхем и модулей памяти DDR3, грядущих на смену нынешней DDR2.

DDR3: некоторые технические сведения

Стандарт DDR3 на сегодняшний день еще не принят JEDEC, его принятие ожидается ближе к середине текущего года (предположительно, он будет носить имя JESD79-3). Поэтому представленная ниже информация о микросхемах и модулях памяти DDR3 пока что носит предварительный характер.

Начнем с микросхем памяти DDR3, первые прототипы которых были объявлены еще в 2005 году. Доступные сегодня образцы микросхем DDR3 основаны на 90-нм технологическом процессе и характеризуются уровнем питающего напряжения 1.5 В, что само по себе вносит примерно 30% вклад в снижение мощности, рассеиваемой этими микросхемами памяти по сравнению с микросхемами DDR2 (имеющими стандартное питающее напряжение 1.8 В). Полное снижение энергопотребления по сравнению с равночастотной DDR2 достигает примерно 40%, что особенно важно для мобильных систем. Емкости компонентов, предусмотренные предварительными спецификациями JEDEC, варьируются от 512 Мбит до 8 Гбит, тогда как типичные выпускаемые на сегодня микросхемы имеют емкость от 1 до 4 Гбит. Теоретическая пропускная способность микросхем DDR3 вдвое выше по сравнению с DDR2 благодаря использованию рассмотренной выше схемы 8n-prefetch (против 4n-prefetch в DDR2). Количество логических банков в микросхемах DDR3 также увеличено вдвое по сравнению с типичным значением для DDR2 (4 банка) и составляет 8 банков, что теоретически позволяет увеличить «параллелизм» при обращении к данным по схеме чередования логических банков и скрыть задержки, связанные с обращением к одной и той же строке памяти (tRP). Микросхемы DDR3 корпусируются в FBGA-упаковку, обладающую рядом улучшений по сравнению с DDR2, а именно (рис. 4):

- Большим количеством контактов питания и «земли»;

- Усовершенствованным распределением питающих и сигнальных контактов, позволяющим достичь лучшее качество электрического сигнала (необходимое для более устойчивого функционирования при высоких частотах);

- Полным «заселением» массива, что увеличивает механическую прочность компонента.

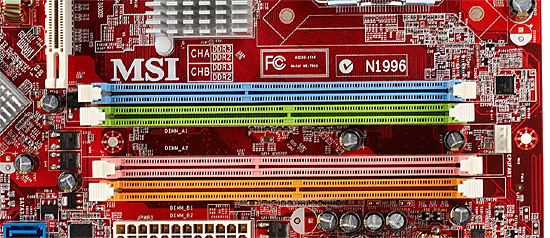

Перейдем к рассмотрению модулей памяти DDR3. Как и модули памяти DDR2, они выпускаются в виде 240-контактной печатной платы (по 120 контактов с каждой стороны модуля), однако не являются электрически совместимыми с последними, и по этой причине имеют иное расположение «ключа» (см. рис. 5а).

Рис. 5а. Внешний вид типичных модулей памяти DDR3 (сверху) и DDR2 (снизу)

Рис. 5б. Внешний вид типичных разъёмов на системной плате (комбо) для установки модулей памяти DDR3 (голубой/розовый) и DDR2 (зелёный/оранжевый)

Отличительной особенностью схемотехнического дизайна модулей памяти DDR3 является применение «сквозной», или «пролетной» (fly-by) архитектуры передачи адресов и команд, а также сигналов управления и тактовой частоты отдельным микросхемам модуля памяти с применением внешнего терминирования сигналов (резистором, расположенным на модуле памяти). Схематически эта архитектура представлена на рис. 6. Она позволяет добиться увеличения качества передачи сигналов, что необходимо при функционировании компонентов при высоких частотах, типичных для памяти DDR3 и не требуется для компонентов памяти стандарта DDR2.

Различие между способом подачи адресов и команд, сигналов управления и тактовой частоты в модулях памяти DDR2 и DDR3 (на примере модулей, физический банк которых составлен из 8 микросхем разрядностью x8) представлено на рис. 7. В модулях памяти DDR2 подача адресов и команд осуществляется параллельно на все микросхемы модуля, в связи с чем, например, при считывании данных, все восемь 8-битных элементов данных окажутся доступными в один и тот же момент времени (после подачи соответствующих команд и истечения соответствующих задержек) и контроллер памяти сможет одновременно прочитать все 64 бита данных. В то же время, в модулях памяти DDR3 вследствие применения «пролетной» архитектуры подачи адресов и команд каждая из микросхем модуля получает команды и адреса с определенным отставанием относительно предыдущей микросхемы, поэтому элементы данных, соответствующие определенной микросхеме, также окажутся доступными с некоторым отставанием относительно элементов данных, соответствующих предыдущей микросхеме в ряду, составляющем физический банк модуля памяти. В связи с этим, с целью минимизации задержек, в модулях памяти DDR3, по сравнению с модулями DDR2, реализован несколько иной подход ко взаимодействию контроллера памяти с шиной данных модуля памяти. Он называется «регулировкой уровня чтения/записи» (read/write leveling) и позволяет контроллеру памяти использовать определенное смещение по времени при приеме/передачи данных, соответствующее «запаздыванию» поступления адресов и команд (а следовательно, и данных) в определенную микросхему модуля. Этим достигается одновременность считывания (записи) данных из микросхем (в микросхемы) модуля памяти.

В заключение рассмотрим скоростные характеристики предполагаемых спецификаций модулей памяти DDR3, которые представлены в таблице 1.

Табл. 1. Скоростные характеристики модулей памяти DDR3

| Тип модулей | Рейтинг | Частота шины, МГц | Типичная схема таймингов | Теоретическая пропускная способность, ГБ/с | |

|---|---|---|---|---|---|

| Одно-канальный режим | Двух-канальный режим | ||||

| DDR3-800 | PC3-6400 | 400 | 6-6-6-18 | 6.40 | 12.80 |

| DDR3-1066 | PC3-8500 | 533 | 7-7-7-21 | 8.53 | 17.07 |

| DDR3-1333 | PC3-10667 | 667 | 8-8-8-24 | 10.67 | 21.33 |

| DDR3-1600 | PC3-12800 | 800 | 9-9-9-27 | 12.80 | 25.60 |

| DDR3-1866 | PC3-14900 | 933 | 10-10-10-30 | 14.93 | 29.87 |

Предположительно, модули памяти DDR3 будут предлагаться в вариантах от DDR3-800 до DDR3-1600 включительно, далее не исключено появление и более высокоскоростных модулей категории DDR3-1866. Рейтинг производительности модулей памяти DDR3 имеет значение вида «PC3-X», где X означает пропускную способность модуля в одноканальном режиме, выраженную в МБ/с (если быть точным — млн. байт/с). Поскольку модули памяти DDR3 имеют ту же разрядность, что и модули памяти DDR2 — 64 бита, численные значения рейтингов равночастотных модулей памяти DDR2 и DDR3 совпадают (например, PC2-6400 для DDR2-800 и PC3-6400 для DDR3-800).

Типичные схемы таймингов, предполагаемые в настоящее время для модулей памяти DDR3, выглядят весьма «внушительно» (например, 9-9-9 для DDR3-1600), однако не стоит забывать, что столь большие относительные значения таймингов, будучи переведенными в абсолютные значения (в наносекундах), учитывая все меньшее время цикла (обратно пропорциональное частоте шины памяти), становятся вполне приемлемыми. Так, например, задержка сигнала CAS# (tCL) для модулей памяти DDR3-800 со схемой таймингов 6-6-6 составляет 15 нс, что, конечно, несколько великовато по сравнению с «типичными» DDR2-800 со схемой таймингов 5-5-5, для которых tCL составляет 12.5 нс. В то же время, память типа DDR3-1600 со схемой таймингов 9-9-9 уже характеризуются величиной задержки tCL всего 11.25 нс, что находится на уровне DDR2-533 с достаточно низкими задержками (схемой таймингов 3-3-3). Таким образом, даже при предполагаемом на данный момент «раскладе» схем таймингов модулей памяти DDR3 можно ожидать постепенное снижение реально наблюдаемых задержек при доступе в память, вплоть до значений, типичных для нынешнего поколения модулей памяти DDR2. К тому же, не стоит забывать и о дальнейшем снижении задержек (и снижении таймингов) по мере развития технологии.

Конфигурация тестового стенда

- Процессор: Intel Core 2 Duo E6600, 2.4 ГГц, 4 МБ shared L2 cache

- Чипсет: Intel P35

- Материнская плата: MSI P35 Neo Combo, версия BIOS V1.0B16 от 20.04.2007

- Память DDR2: Corsair DOMINATOR XMS2-9136C5D в режиме DDR2-1066, тайминги 5-5-5-15

- Память DDR3: Corsair XMS3-1066C7 (инженерный образец), DDR3-1066, тайминги 7-7-7-21

DDR3: первые результаты реального тестирования

Перейдем, как говорится, от теории к практике. В распоряжении нашей тестовой лаборатории оказались уникальные предсерийные образцы материнской платы MSI P35 Neo Combo, основанная на новом чипсете Intel P35 и модулей памяти Corsair XMS3-1066 (CM3X1024-1066C7 ES). Материнская плата MSI P35 Neo Combo, как следует из ее названия, представляет собой «комбинированный» вариант, т.е. позволяет устанавливать как модули памяти DDR2, так и DDR3. Заметим, что «комбинирование» модулей памяти в этой материнской плате осуществляется по принципу «либо DDR2, либо DDR3», т.е. одновременное использование модулей памяти DDR2 и DDR3 (как в общем канале, так и для составления разных каналов) невозможно. На настоящее время, вследствие отсутствия официальной спецификации на новые чипсеты Intel, невозможно сказать, является ли это принципиальным ограничением чипсета Intel P35, либо просто особенностью разводки данной платы. Однако весьма вероятно, что имеет место первый вариант — чипсеты Intel, как правило, не отличаются сомнительным экзотическим преимуществом в виде одновременной поддержки разных типов памяти.

Читайте также: Шины pirelli scorpion verde 235 55 r18 100v

Модули памяти CM3X1024-1066C7 ES представляют собой инженерный образец модулей памяти DDR3-1066 со схемой таймингов 7-7-7-21 (в точности совпадающей с предполагаемой схемой для модулей памяти DDR3 данной скоростной категории, приведенной в табл. 1). Для сопоставления скоростных характеристик этих модулей памяти, как представителей нового типа памяти DDR3, со скоростными характеристиками нынешнего поколения модулей памяти DDR2 были выбраны модули памяти Corsair DOMINATOR XMS2-9136C5D примерно равной скоростной категории «DDR2-1142», использованные в режиме DDR2-1066 с номинальной для этих модулей схемой таймингов 5-5-5-15.

Режим функционирования модулей памяти DDR2 и тайминги устанавливались вручную в настройках BIOS материнской платы, питающее напряжение было увеличено до 2.3 В. Заметим, что текущая версия BIOS (V1.0B16 от 20.04.2007) материнской платы MSI P35 Neo Combo не позволяет настроить значения таймингов модулей памяти DDR3 должным образом, по-прежнему предлагая значения основных параметров (tCL, tRCD и tRP) от 3 до 6 включительно, что соответствует таймингам памяти DDR2, но не DDR3. То же касается и питающего напряжения модулей — по-прежнему предлагается выбор от 1.8 В до 2.5 В, тогда как «официальное» питающее напряжение модулей памяти DDR3 составляет всего 1.5 В. В связи с этим, для модулей памяти DDR3 были выбраны «автоматические» настройки «by SPD» при минимальном питающем напряжении 1.8 В, однако сказать что-либо определенное относительно этих настроек (как о реальной поддержки еще не утвержденного стандарта специфических расширений SPD для DDR3, так и о корректной настройке временных параметров контроллера памяти чипсета Intel P35 при использовании DDR3) невозможно. Достаточно сказать лишь главное: используемая нами связка модули памяти DDR3 Corsair XMS3-1066 и материнской платы MSI P35 Neo Combo оказались работоспособной. Так что приступим к рассмотрению результатов наших тестов, выполненных в последней доступной версии тестового пакета RightMark Memory Analyzer 3.72, включающего в себя тест многопоточного доступа к памяти RightMark Multi-Threaded Memory Test 1.0.

Начнем с тестов реальной пропускной способности памяти (ПСП) при «одноядерном» варианте доступа. Как обычно, измерение реальной ПСП проводилось в четырех режимах доступа: «простом» чтении данных (Read), «простой» записи данных (Write), чтении данных с программной предвыборкой при оптимальной дистанции предвыборки, которая для процессора Intel Core 2 Duo в составляет примерно 1024 байта (Read SW PF) и, наконец, записи данных методом прямого сохранения (Write NT). При этом первые два режима доступа позволяют оценить «среднюю» реальную ПСП при операциях чтения и записи, а два последних режима — максимальную реальную ПСП при тех же операциях.

Из приведенной на рис. 8 диаграммы с результатами тестов памяти DDR2-1066 и DDR3-1066 в однопоточном режиме доступа видно, что DDR3 если и уступает равночастотной DDR2, то весьма незначительно: отставание составляет примерно 5-8% и особенно заметно по максимальной реальной ПСП при операциях чтения. При этом и в том, и в другом случае реально наблюдаемые величины ПСП весьма далеки от максимальной теоретической ПСП DDR2/DDR3-1066, которая в двухканальном режиме составляет примерно 17.1 ГБ/с. Впрочем, последнее обстоятельство хорошо объясняется наличием «узкого места» в системе в виде 266-МГц системной шины (1066 МГц Quad-Pumped bus), пиковая пропускная способность которой — всего 8.53 ГБ/с.

Использование двухпоточного варианта доступа к памяти (одновременно с обоих ядер процессора, см. рис. 9) позволяет достичь несколько больших значений ПСП (порядка 8.0 ГБ/с, что ближе к теоретическому пределу ПС системной шины 8.53 ГБ/с), причем в данном случае DDR3-1066 в целом оказывается примерно наравне с DDR2-1066, а в случае максимальной реальной ПСП на чтение даже превосходит последнюю примерно на 2%. Итак, заключаем: что касается реальной пропускной способности, на нынешнем поколении платформ Intel оперативная память нового стандарта DDR3 как минимум не уступает, а в ряде случаев и превосходит равночастотную память стандарта DDR2. А значит, применение «сквозной» архитектуры подачи адресов и команд (fly-by architecture) и компенсирующего ее принципа регулировки уровня чтения/записи (read/write leveling), необходимых для достижения высоких частот функционирования компонентов памяти, оправдывает свое назначение, поскольку как минимум не ухудшает (а возможно, и несколько улучшает) скоростные характеристики подсистемы памяти.

Внимательный читатель вполне может возразить на эти выводы, сделанные на основании тестов памяти исключительно в двухканальном режиме. Действительно, ведь «узким местом» системы в данном случае является не шина памяти (от двух каналов контроллера к каждому из модулей памяти), а системная шина (от процессора к чипсету/контроллеру памяти). Поэтому, быть может, мы просто «не видим» разницу между DDR2 и DDR3 именно по этой причине? Поскольку такое возражение было бы вполне закономерным, мы решили проверить правомерность сделанного нами вывода, исследовав одноканальный режим работы памяти. Конечно, такой режим работы в наши дни представляет лишь чисто теоретический интерес, но именно он позволяет «приравнять» пиковую ПС системной шины и шины памяти, тем самым исключив возможное влияние первой на результаты низкоуровневого тестирования. Соответствующие результаты приведены в таблице 2.

Табл. 2. Реальная пропускная способность памяти DDR2 и DDR3

в одноканальном режиме

| Режим доступа | Реальная пропускная способность, ГБ/с | |

|---|---|---|

| DDR2-1066 | DDR3-1066 | |

| Чтение, 1 ядро | 6.47 | 5.80 |

| Запись, 1 ядро | 2.42 | 2.33 |

| Чтение с программной предвыборкой, 1 ядро | 6.90 | 6.34 |

| Запись методом прямого сохранения, 1 ядро | 4.88 | 4.88 |

| Чтение, 2 ядра | 6.83 | 6.89 |

| Запись, 2 ядра | 2.17 | 2.06 |

| Чтение с программной предвыборкой, 2 ядра | 6.96 | 7.10 |

| Запись методом прямого сохранения, 2 ядра | 4.83 | 4.84 |

Как и следовало ожидать, величины ПСП, как при «одноядерном», так и при «двухъядерном» доступе к памяти в одноканальном режиме ее работы оказываются заметно меньшими по сравнению с соответствующими значениями ПСП при двухканальном режиме работы оперативной памяти. Более того, «одноядерный» вариант доступа показывает несколько большее, но все же не столь существенное отставание DDR3 от DDR2 (4-11%), однако «двухъядерный» доступ в память вновь практически выравнивает показания DDR2 и DDR3 и также позволяет последней выиграть примерно 1-2% у равночастотной DDR2 при операциях чтении данных. Максимальная реальная ПСП как DDR2-1066, так и DDR3-1066 достигает примерно 82-83% от теоретического максимума памяти рассматриваемой скоростной категории, функционирующей в одноканальном режиме, что, на наш взгляд, является весьма неплохим результатом. А сами по себе результаты тестов DDR2 и DDR3 в одноканальном режиме подтверждают правомерность выводов относительно скоростных характеристик памяти DDR3, сделанных нами выше.

Что ж, нам остается оценить задержки при доступе к равночастотной памяти DDR2 и DDR3 (так называемую «латентность памяти»). Конечно, из общих соображений следует ожидать большую их величину для последней (учитывая, хотя бы, большую схему таймингов 7-7-7 против 5-5-5 для DDR2), однако посмотрим, какой окажется разница по задержкам на самом деле. Заметим, что в данном случае мы получили практически идентичный результат как в двухканальном, так и в одноканальном режиме работы памяти, поэтому приведем лишь результаты для двухканального режима, имеющего практический смысл (см. рис. 10).

Итак, задержки при доступе в память типа DDR3-1066, естественно, оказываются выше по сравнению с доступом в память типа DDR2-1066. Относительное увеличение задержек составляет примерно 13% при псевдослучайном доступе и примерно 16% — при истинно случайном доступе. Тем не менее, если учесть, что различие между схемами таймингов 7-7-7-21 и 5-5-5-15 составляет целых 40% (правда, как мы писали выше, в случае DDR3 мы пока не можем сказать ничего определенного относительно реально используемой схемы таймингов), реально наблюдаемое увеличение задержек при переходе от DDR2 к DDR3 выглядит более чем приемлемым.

Заключение

Результаты нашего первого низкоуровневого тестирования инженерных образцов модулей памяти DDR3 в сопоставлении с равночастотными модулями памяти DDR2 в идентичных условиях тестирования позволяют нам заключить, что память нового, еще не принятого окончательно стандарта DDR3 уже на сегодняшний день может оправдывать свое существование. Ее скоростные характеристики как минимум не уступают, а в ряде случаев и несколько превосходят характеристики аналогичных модулей памяти текущего стандарта DDR2. Сравнительно небольшим оказалось и относительное возрастание задержек (13-16%) при переходе от DDR2 к DDR3 при прочих равных условиях. А если учесть, что развитие технологий памяти в основном идет по пути одновременного роста тактовых частот и снижения задержек, будущее поколение DDR3 вполне сможет сократить указанный разрыв, а то и вовсе выигрывать по задержкам у DDR2 (уже сегодня практически прекратившей свое дальнейшее развитие).

В то же время, нельзя не заметить, что пока что новую память DDR3 ждет примерно та же участь, что и нынешнее поколение высокоскоростной DDR2 (DDR2-800 и выше). А именно — серьезное затруднение раскрытия гигантского скоростного потенциала самой оперативной памяти, которая давно перестала быть «узким местом» системы. Так, например, на участвующей в нашем сегодняшнем исследовании платформе Intel Core 2 Duo / Intel P35 приличного раскрытия потенциала памяти DDR2-1066 или DDR3-1066 можно ожидать лишь в одноканальном режиме работы последней (как мы показали, при этом реальная пропускная способность памяти достигает примерно 83% от теоретического максимума), который, согласитесь, не представляет интереса с практической точки зрения. Применение же двухканального режима работы памяти приводит к серьезному ограничению ее ПСП со стороны системной шины, вдвое более узкой по своей пропускной способности. Мы неоднократно упоминали о подобных ограничениях в нашем цикле статей по оперативной памяти (см., например, iТоги за 2006 год), и нам остается надеяться, что производители важнейших компонентов платформы — процессоров и чипсетов — осознают необходимость серьезной модернизации последних для достижения высоких стандартов скорости, диктуемых. технологиями оперативной памяти.

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле