Шина адреса – шина МПС, используемая микропроцессором или устройствами, способными формировать адрес, для указания физического адреса слова ОЗУ (или начала блока слов) либо внешнего устройства, к которому активное устройство желает обратиться для проведения операции чтения или записи.

Шина адреса АВ (Address Bus), в принципе, может быть однонаправленной. Она предназначена для передачи адреса ячейки памяти или устройства ввода/вывода. Направление передачи по шине адреса — от МП к внешним устройствам. Варианты условных обозначений однонаправленной параллельной шины показаны на рис. 1.3, где стрелка указывает направление передачи.

Рис.1.3. Варианты условных обозначений однонаправленной параллельной 16-разрядной шины

Число 16 на рис. 1.3 обозначает разрядность шины. Допускается обозначение шин и без указания разрядности.

Основной характеристикой шины адреса является её разрядность (ширина) в битах. Ширина шины адреса определяет объём адресуемой памяти. Например, если ширина адресной шины составляет 16 бит, и размер слова памяти равен одному байту (минимальный адресуемый объём данных), то объём памяти, который можно адресовать, составляет 2 16 = 65536 байтов (64 Кбайт). Количество адресуемых ячеек памяти можно рассчитать по формуле:

где I — разрядность шины адреса.

Если рассматривать структурную схему микропроцессора, то адресная шина активизирует работу всех внешних устройств по команде, которая поступает с микропроцессора.

Если шина адреса является однонаправленной, то источником адреса является только одно устройство (например, МП), но тогда один из режимов работы МПС может оказаться невозможным – прямой доступ к памяти (захват магистрали, DMA).

Шина данных

Шина данных служит для пересылки данных между ЦП и памятью или ЦП и устройствами ввода/вывода. Эти данные могут представлять собой как команды ЦП, так и информацию, которую ЦП посылает в порты ввода/вывода или принимает оттуда. Таким образом, данные по шине данных могут передаваться от одного устройства к другому в любом направлении.

Шина данных DB (Data Bus) принципиально является двунаправленной. Она предназначена для передачи данных между блоками МПС. Информация по одним и тем же линиям DB может передаваться в двух направлениях — как к МП, так и от него. Варианты условных обозначений двунаправленной шины показаны на рис. 1.4.

Рис.1.4. Варианты условных обозначений двунаправленной параллельной 8-разрядной шины

Разрядность шины данных определяется разрядностью процессора, то есть количеством двоичных разрядов, которые могут обрабатываться или передаваться процессором одновременно. Разрядность процессоров постоянно увеличивается по мере развития компьютерной техники.

В МП 8088 шина данных имеет разрядность (ширину) 8 бит. В МП 8086, 80186, 80286 ширина шины данных 16 разрядов; в МП 80386, 80486, Pentium и Pentium Pro — 32 разряда.

Подчеркнем, что ШД всегда принципиально двунаправлена (иначе либо чтение, либо запись будут запрещены).

Двунаправленность сводится к тому, что на одну и ту же линию шины в разные моменты времени должны иметь возможность выдавать данные несколько устройств (модулей).

Для того, чтобы модули не мешали друг другу при работе на общую шину, существует 2 варианта исполнения выходных каскадов элементов, работающих на линию системной магистрали:

— элемент с тремя состояниями (с z-состоянием);

— схема с открытым коллектором (рис. 1.5).

Рис.1.5 Выход с открытым коллектором

Шина управления

По шине управления передаются сигналы, определяющие характер обмена информацией по магистрали. Сигналы управления определяют, какую операцию — считывание или запись информации из памяти нужно производить, синхронизируют обмен информацией между устройствами и т.д.

Шина управления СВ (Control Bus) предназначена для передачи управляющих сигналов. Хотя направление управляющих сигналов может быть разным, однако шина управления не является двунаправленной, поскольку для сигналов разного направления используются отдельные линии.

В основу построения подавляющего большинства компьютеров положены следующие общие принципы, сформулированные в 1945 г. американским ученымДжоном фон Нейманом.

1. Принцип программного управления. Программа состоит из набора команд, выполняющихся процессором автоматически в определенной последовательности.

2. Выборка программы из памяти осуществляется с помощью счетчика команд. Этот регистр процессора последовательно увеличивает хранимый в нем адрес очередной команды на длину команды. А так как команды программы расположены в памяти друг за другом, то тем самым организуется выборка цепочки команд из последовательно расположенных ячеек памяти. Если же нужно после выполнения команды перейти не к следующей, а к какой-то другой, используются командыусловного илибезусловного перехода, которые заносят в счетчик команд номер ячейки памяти, содержащей следующую команду. Выборка команд из памяти прекращается после достижения и выполнения команды «стоп». Таким образом,процессор исполняет программу автоматически, без вмешательства человека.

3. Принцип однородности памяти. Программы и данные хранятся в одной и той же памяти, поэтому компьютер не различает, что хранится в данной ячейке памяти – число, текст или команда. Над командами можно выполнять такие же действия, как и над данными.

Это открывает целый ряд возможностей. Например,программа в процессе своего выполнения также может подвергаться переработке, что позволяет задавать в самой программе правила получения некоторых ее частей (так в программе организуется выполнение циклов и подпрограмм).

Более того, команды одной программы могут быть получены как результаты исполнения другой программы. На этом принципе основаныметоды трансляции – перевода текста программы с языка программирования высокого уровня на язык конкретной машины.

4. Принцип адресности. Структурно основная память состоит из перенумерованных ячеек. Процессору в произвольный момент времени доступна любая ячейка. Отсюда следует возможность давать имена областям памяти так, чтобы к запомненным в них значениям можно было впоследствии обращаться или менять их в процессе выполнения программ с использованием присвоенных имен.

Компьютеры, построенные на перечисленных принципах, относятся к типуфон-неймановских. Но существуют компьютеры, принципиально отличающиеся от фон-неймановских. Для них, например, может не выполняться принцип программного управления, т. е. они могут работать без счетчика команд, указывающего текущую выполняемую команду программы. Для обращения к какой-либо переменной, хранящейся в памяти, этим компьютерам необязательно давать ей имя. Такие компьютеры называются не фон-неймановскими.

Читайте также: Сборные шины для распределительных щитов

ИУ – интерфейсное устройство

Рисунок 1.7 – Типовая структура микропроцессорной системы

Системная шинасодержит несколько десятков (в сложных системах более 100) проводников, которые в соответствии с их функциональным назначением подразделяются на отдельные шины:

· шина адреса А, служит для передачи адреса, который формируется микропроцессором и позволяет выбрать необходимую ячейку памяти ОЗУ (ПЗУ) или требуемое ИУ при обращении к внешнему устройству;

· шина данных D, служит для выборки команд, поступающих из ОЗУ или ПЗУ в УУ микропроцессора, и для пересылки обрабатываемых данных (операндов) между микропроцессором и ОЗУ или ИУ (внешним устройством);

· шина управления С, служит для передачи разнообразных управляющих сигналов, определяющих режимы работы памяти (запись или считывание), интерфейсных устройств (ввод или вывод информации) и микропроцессора (запуск, запросы внешних устройств на обслуживание, информация о текущем режиме работы) и другие сигналы.

1.6.3Классификация микропроцессоров

Микропроцессоры

Рисунок 1.8 – Классификация микропроцессоров

86. Системная шина. Шина адреса, шина данных, шина управления, их назначение и разрядность. Мультиплексированная шина адреса-данных.

Системная шина содержит несколько десятков (в сложных системах более 100) проводников, которые в соответствии с их функциональным назначением подразделяются на отдельные шины – адреса А, данных D и управления С. Шина А служит для передачи адреса, который формируется микропроцессором и позволяет выбрать необходимую ячейку памяти ОЗУ (ПЗУ) или требуемое ИУ при обращении к внешнему устройству. Шина D служит для выборки команд, поступающих из ОЗУ или ПЗУ в УУ микропроцессора, и для пересылки обрабатываемых данных (операндов) между микропроцессором и ОЗУ или ИУ (внешним устройством). По шине С передаются разнообразные управляющие сигналы, определяющие режимы работы памяти (запись или считывание), интерфейсных устройств (ввод или вывод информации) и МП (запуск, запросы внешних устройств на обслуживание, информация о текущим режиме работы и другие сигналы).

Разрядность шины данных обычно соответствует разрядности операндов, обрабатываемых МП. Поэтому чаще всего шина D содержит 8, 16, или 32 линии для передачи соответствующих разрядов данных и команд. В ряде последних моделей МП используется шина D с расширенной разрядностью, чтобы обеспечить одновременную передачу нескольких команд или операндов. Например, 32-разрядные МП Pentium имеют 64-разрядную шину данных.

Разрядность шины адреса определяет максимальный объем адресуемой процессором внешней памяти. Например, 16-разрядная шина А обеспечивает адресацию памяти объемом до 64 Кбайт, а 32-разрядная шина – до 4 Гбайт. Процессоры Pentium II, Pentium III, Pentium IV имеют 36-разрядную шину адреса, обеспечивающую обращение к памяти объемом до 64 Гбайт.

Во многих микропроцессорных системах передача адреса и данных сопровождается посылкой контрольных битов четности, которые обеспечивают выявление возможных ошибок, возникающих в процессе обмена. При этом обычно реализуется побайтный контроль четности, при котором каждый байт адреса или данных сопровождается дополнительным (9-м) контрольным битом, поступающим на отдельный вывод МП.

В некоторых системах для уменьшения числа необходимых линий связи и соответствующих выводов и контактов используется мультиплексирование линий адреса и данных. В таких системах для передачи адреса и данных используются одни и те же линии связи, на которые сначала выдается адрес, а затем поступают данные. Например, 16-разрядные микроконтроллеры семейства MCS-196, выпускаемые компанией Intel, имеют мультиплексированную 16-разрядную шину адреса данных AD. Обмен информацией по мультиплексированной шине AD требует введения отдельного регистра для хранения адреса в процессе пересылки данных. При этом требуется также дополнительное время для реализации обмена, что несколько снижает производительность системы.

Разрядность шины управления С определяется организацией работы системы, возможностями реализации различных режимов ее функционирования, используемыми методами контроля микропроцессора и других устройств. Поэтому набор передаваемых по шине С управляющих сигналов является индивидуальным для каждой модели микропроцессора. Имеется ряд управляющих сигналов, которые используются в большинстве микропроцессорных систем. К ним относятся сигналы начального запуска (RESET), сигналы, задающие режим работы памяти (чтение – RD, запись – WR), сигналы, необходимые для реализации прерываний и ряд других. В простых системах для передачи управляющих сигналов может использоваться всего несколько линий, а в сложных системах число этих линий составляет несколько десятков.

87. Основные режимы работы микропроцессорной системы. Характеристики режима > работы микропроцессора.

В процессе функционирования микропроцессорной системы реализуются следующие основные режимы ее работы:

– выполнение основной программы;

– обслуживание прерываний и исключений;

Рассмотрим основные принципы реализации этих режимов.

Выполнение основной программы. В этом режиме процессор выбирает из ОЗУ очередную команду программы и выполняет соответствующую операцию. Команда представляет собой многоразрядное двоичное число (рис. 8.4), которое состоит из двух частей (полей) – кода операции (КОП) и кода адресации операндов (КАД).

Код адресации операндов (КАД)

Рис. 8.4. Формат типовой команды микропроцессора

Код операции КОП задает вид операции, выполняемой данной командой, а код адресации КАД определяет выбор операндов (способ адресации), над которыми производится заданная операция. В зависимости от типа микропроцессора команда может содержать различное число разрядов (байтов). Например, команды процессоров Pentium содержат от 1 до 15 байтов, а большинство процессоров с RISС-архитектурой используют фиксированный 4-байтный формат для любых команд.

Для хранения адреса очередной команды служит специальный регистр процессора – программный счетчик PC (Program Counter), содержимое которого автоматически увеличивается на 1 после выборки следующего байта команды. Таким образом, обеспечивается последовательная выборка команд в процессе выполнения программы. При выборке очередной команды содержимое PC поступает на шину адреса, обеспечивая считывание из ОЗУ следующей команды выполняемой программы. При реализации безусловных или условных переходов (ветвлений) или других изменений последовательности выполнения команд выполняется загрузка в PC нового содержимого, в результате чего производится переход к другой ветви программы или подпрограмме.

В процессорах Pentium и предыдущих моделях МП компании Intel (8086, 80186, 80286, 386, 486 и ряде других) реализуется сегментная организация памяти. При этом адрес выбираемой команды определяется содержимым двух регистров – указателя команды IP, указывающего положение команды в сегменте программ, и сегментного регистра CS, который задает начальный (базовый) адрес этого сегмента. Регистры IP и CS выполняют функции программного счетчика PC, и различные виды передачи управления в программе реализуются путем изменения их содержимого.

Читайте также: Volvo s40 какое давление в шинах

Принятая из ОЗУ команда поступает в регистр команд, входящий в состав УУ процессора. Затем производится дешифрация команды, в процессе которой определяется вид выполняемой операции (расшифровка КОП) и формируется адрес необходимых операндов (расшифровка КАД). В соответствии с кодом поступившей команды УУ процессора генерирует последовательность микрокоманд, обеспечивающих выполнение заданной операции. Каждая микрокоманда выполняется в течение одного машинного такта – периода тактовых импульсов, задающих рабочую частоту всех внутренних узлов и блоков микропроцессора. Таким образом, тактовая частота микропроцессора определяет время выполнения отдельных микрокоманд, последовательность которых обеспечивает получение необходимого результата операции.

Для выполнения каждой поступившей команды требуется определенное количество циклов и тактов. Командным циклом называется промежуток времени, требуемый для выполнения обращения к ОЗУ или внешнему устройству с помощью системной шины. Обычно реализация такого цикла занимает от 2 до 4 системных тактов (период синхросигналов шины), которые требуются для установки требуемого адреса, выдачи сигналов, определяющих вид цикла – чтение или запись, получение сигнала готовности к обмену (от памяти или внешних устройств) и собственно передачи данных или команд. При современной технологии изготовления системных плат частота синхросигналов шины обычно составляет десятки МГц (типичные значения 25, 33, 50, 66, 75, 100, 133 МГц).

При выполнении каждой команды в первых циклах производится ее выборка из ОЗУ по адресу, которых задается содержимым программного счетчика PC. Последующая дешифрация выбранной команды определяет необходимое число циклов для ее последующего выполнения. Если для выполнения команды не требуется считывание операндов из памяти (внешних устройств) или запись в память (вывод на внешние устройства) результатов операции, то такая команды выполняется за один цикл. При считывании операндов из памяти (внешних устройств) или записи результата в память (вывод на внешние устройства) требуется выполнение дополнительных циклов чтения (ввода) или записи (вывода). В зависимости от разрядности обрабатываемых операндов и разрядности используемой системной шины число циклов, необходимых для выполнения команд, может быть различным: от 1 (выборка команды) до 4–5 (зависит от команды, разрядности шин и операндов).

Машинным (процессорным) тактом в микропроцессорных системах является длительность периода тактовых сигналов

Текущее состояние процессора при выполнении программы определяется содержимым регистра состояния SR (State Register, в микропроцессорах Pentium данный регистр называется EFLAGS). Этот регистр содержит биты управления, задающие режим работы процессора, и биты признаков (флаги), указывающие характеристики результата выполнения операции:

N – признак знака (старший бит результата), N=0 – при положительном результате, N=1 – при отрицательном результате;

C – признак переноса, C=1, если при выполнении операции образовался перенос из старшего разряда результата;

V – признак переполнения, V=1, если при выполнении операций над числами со знаком произошло переполнение разрядной сетки процессора;

Z – признак нуля, Z=1, если результат операции равен нулю.

Некоторые микропроцессоры фиксируют также другие виды признаков: признак четности результата, признак переноса между тетрадами младшего байта. Специальные виды признаков устанавливаются по результатам операций над числами, представленными в формате с «плавающей точкой».

88. Режим > работы микропроцессора.

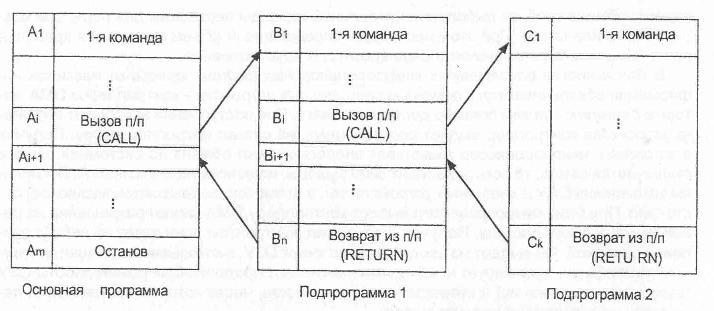

Вызов подпрограммы. Обращение к подпрограмме реализуется при поступлении в микропроцессор специальной команды CALL (в некоторых процессорах эта команда имеет мнемоническое обозначение JSR – Jump-to-Subroutine), которая указывает адрес первой команды вызываемой подпрограммы. Этот адрес загружается в PC, обеспечивая в следующем командном цикле выборку первой команды подпрограммы. Предварительно выполняется процедура сохранения в специальном регистре или ячейке памяти текущего содержимого PC, где хранится адрес следующей команды основной программы, чтобы обеспечить возвращение к ней после выполнения подпрограммы. Возврат к основной программе реализуется при поступлении команды RETURN (мнемоническое обозначение RET), завершающей подпрограмму. По этой команде сохранявшееся содержимое PC снова загружается в программный счетчик, обеспечивая выполнение команды, которая в исходной программе следовала за командой CALL.

Особенность этой процедуры состоит в том, что большинство микропроцессоров обеспечивают возможность вложения подпрограмм, т.е. реализуют при выполнении подпрограммы вызов новой подпрограммы с последующим возвращением к предыдущей подпрограмме (рис. 8.5). При вложении нескольких подпрограмм требуется сохранение нескольких промежуточных значений содержимого PC и последовательная загрузка этих значений в PC при возврате к предыдущим подпрограммам и к основной программе.

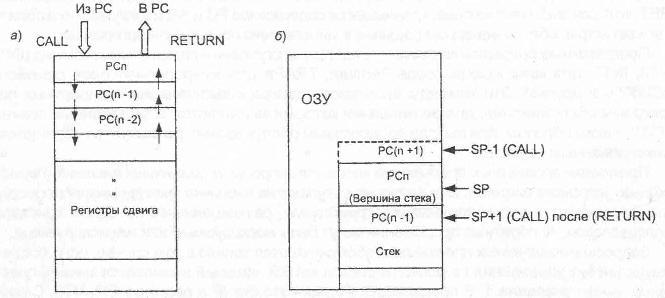

Для реализации этой процедуры используется стек – специальная память магазинного типа, работающая по принципу «последний пришел – первый ушел» (стек типа LIFO «Last In – First Out»). Существуют различные варианты реализации стека.

Рис. 8.5. Последовательный вызов (вложение) подпрограмм

Регистровый стек (рис. 8.6, а) реализуется с помощью реверсивных сдвиговых регистров. Каждая команда CALL вызывает ввод в стек очередного содержимого PC. По команде RETURN направление сдвига изменяется и производится извлечение из стека последнего поступившего содержимого PC. Таким образом обеспечивается выполнение вложенных подпрограмм. Возможное число вложенных подпрограмм определяется глубиной стека, т.е. разрядностью используемых регистров сдвига. Если число вложений превышает глубину стека, первые из введенных в стек значений PC теряются, т.е. возврат к основной программе не будет обеспечен. Поэтом при использовании регистрового стека необходим строгий контроль за числом вложений. Такая реализация стека применяется в системах, решающих задачи с ограниченным числом вложенных подпрограмм (обычно не более 10–20).

Читайте также: Год производства шины где посмотреть pirelli

Значительно более широкие возможности вложения подпрограмм обеспечивает реализация стека в ОЗУ (рис. 8.6, б). В этом случае часть ОЗУ выделяется для работы в качестве стека. Адресация к ячейкам стека производится с помощью специального регистра – указателя стека SP (Stack Pointer), который вводится в состав УУ процессора. Регистр SP содержит адрес верхней заполненной ячейки стека, в которой хранится значение PC, записанное при выполнении команды CALL. При поступлении новой команды CALL содержимое SP автоматически уменьшается на 1, адресуя следующую, еще не заполненную ячейку стека. Полученный адрес SP–1 выдается на шину А, а на шину D поступает содержимое PC, которое должно сохраняться в стеке. Таким образом, производится последовательное заполнение ячеек стека «снизу-вверх», при этом SP всегда адресует вершину стека. По команде RETURN текущее содержимое SP выдается на шину А, и по шине D производится считывание с вершины стека последнего записанного значения PC. После этого содержимое SP увеличивается на 1, адресуя предыдущее значение PС, хранящееся в стеке. Так как ОЗУ обычно имеет значительный объем, то для размещения стека можно выделить достаточно большое количество ячеек памяти, обеспечивая необходимый уровень вложения подпрограмм.

Рис. 8.6. Варианты реализации стека: регистровый стек (а) и стек в ОЗУ (б)

89. Режим > работы микропроцессора.

Обслуживание прерываний и исключений. При работе микропроцессорной системы часто возникают ситуации, когда требуется прервать выполнение текущей программы и перейти к подпрограмме, обеспечивающей необходимую реакцию системы на создавшиеся обстоятельства. Такие ситуации называются прерываниями или исключениями в зависимости от причин, вызывающих их возникновение.

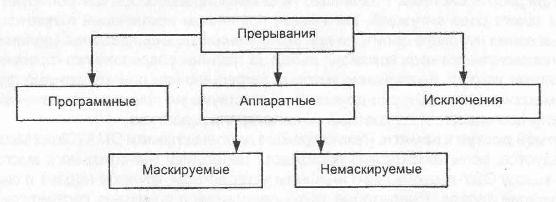

Прерываниями (interruption) являются ситуации, возникающие при поступлении соответствующих команд (программные прерывания) или сигналов от внешних устройств (аппаратные прерывания). Исключениями (exception) являются нештатные ситуации (ошибки), возникающие при работе процессора. При выявлении таких ошибок соответствующие блоки, контролирующие работу процессора, вырабатывают внутренние сигналы запроса, обеспечивающие вызов необходимой подпрограммы обслуживания. Классификация прерываний и исключений приведена на рис. 8.7.

Во всех этих ситуациях микропроцессор завершает выполнение очередной команды и заносит в стек текущее содержимое программного счетчика PC, которое является адресом возврата к прерванной программе после реализации подпрограммы обслуживания, и содержимое регистра состояния SR. Если запрос прерывания поступает от внешнего устройства, то процессор формирует сигнал подтверждения прерывания, которых информирует это устройство, что начато обслуживание данного запроса. Затем в PC загружается из памяти вектор прерывания Ve – начальный адрес соответствующей подпрограммы обслуживания. Эти вектора являются входами в подпрограммы обслуживания и хранятся в таблице векторов прерывания, которая обычно записывается в ОЗУ. Размер таблицы зависит от числа типов обслуживаемых прерываний и исключений. В простейших микропроцессорах это число составляет несколько единиц, а для микропроцессоров семейства Pentium или MC68000 обеспечивается возможность реализации до 256 различных подпрограмм обслуживания. Завершается подпрограмма обслуживания специальной командой возврата из прерывания IRET, которая выбирает из стека хранившееся содержимое PC и SR и загружает его обратно в эти регистры, обеспечивая возвращение к выполнению прерванной программы.

Рис. 8.7. Классификация прерываний и исключений

Программные прерывания реализуются при поступлении специальных команд (INTn, INT3, INTO для микропроцессоров Pentium, TRAPn для микропроцессоров семейства MC68000 и другие). Эти команды вызывают переход к выполнению стандартных подпрограмм обслуживания, для размещения которых выделяются определенные позиции в ОЗУ. Таким образом, при вызове подпрограмм обслуживания реализуется обращение к фиксированным адресам.

Причинами аппаратных прерываний являются запросы от различных внешних (периферийных) устройств системы. Эти запросы поступают на внешние выводы микропроцессора или формируются периферийными устройствами, размещенными на одном кристалле с процессором. Аппаратные прерывания могут быть маскируемые или немаскируемые.

Запросы маскируемых прерываний обслуживаются только в том случае, если соответствующий бит управления I в регистре состояния SR, который называется маской прерываний, имеет значение 1. В процессорах Pentium это бит IF в регистре EFLAGS. С помощью специальных команд значение этого бита может быть установлено в 1 или сброшено в 0. Таким образом, можно разрешить или запретить обслуживание поступивших аппаратных прерываний при выполнении определенных программ или их фрагментов. При одновременном поступлении нескольких запросов обслуживание реализуется в соответствии с их приоритетом. В ряде микропроцессорных систем для обеспечения приоритетного обслуживания запросов от многих внешний устройств включаются специальные микросхемы – контроллеры прерываний. Некоторые типы микропроцессоров имеют внутренние контроллеры для организации приоритетных прерываний.

Немаскируемые запросы прерывания обслуживаются в первоочередном порядке и не могут быть маскированы. Обычно микропроцессор имеет один вход для подачи немаскируемых запросов, которые формируются при возникновении каких-либо аварийных ситуаций. Чаще всего этот вход используется для контроля напряжения питания. Если напряжение питания выходит за допустимые пределы, то специальный датчик вырабатывает немаскируемый запрос прерывания, поступающий в микропроцессор. При этом источник питания должен некоторое время (порядка 10 мс) сохранять необходимый уровень напряжения питания, в течение которого микропроцессор выполняет подпрограмму перезаписи на магнитный диск информации, достаточной для продолжения прерванной программы после восстановления нормального режима питания.

Для передачи сигналов запроса и подтверждения прерывания между микропроцессором и внешними устройствами или контроллером прерываний используются соответствующие линии шины управления С.

Причинами исключений могут быть различные ошибки и нештатные ситуации, возникающие при работе системы. Различные типы микропроцессоров контролируют разные варианты такого рода ситуаций. Типичными причинами исключений являются, например, использование нулевого делителя при выполнении команды деления (деление на 0); выборка неправильного кода команды; выход за границы разрешенного фрагмента памяти; поступление команд, выполнение которых запрещено при данном режиме функционирования микропроцессора и ряд других.

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле