Шина адреса – шина МПС, используемая микропроцессором или устройствами, способными формировать адрес, для указания физического адреса слова ОЗУ (или начала блока слов) либо внешнего устройства, к которому активное устройство желает обратиться для проведения операции чтения или записи.

Шина адреса АВ (Address Bus), в принципе, может быть однонаправленной. Она предназначена для передачи адреса ячейки памяти или устройства ввода/вывода. Направление передачи по шине адреса — от МП к внешним устройствам. Варианты условных обозначений однонаправленной параллельной шины показаны на рис. 1.3, где стрелка указывает направление передачи.

Рис.1.3. Варианты условных обозначений однонаправленной параллельной 16-разрядной шины

Число 16 на рис. 1.3 обозначает разрядность шины. Допускается обозначение шин и без указания разрядности.

Основной характеристикой шины адреса является её разрядность (ширина) в битах. Ширина шины адреса определяет объём адресуемой памяти. Например, если ширина адресной шины составляет 16 бит, и размер слова памяти равен одному байту (минимальный адресуемый объём данных), то объём памяти, который можно адресовать, составляет 2 16 = 65536 байтов (64 Кбайт). Количество адресуемых ячеек памяти можно рассчитать по формуле:

где I — разрядность шины адреса.

Если рассматривать структурную схему микропроцессора, то адресная шина активизирует работу всех внешних устройств по команде, которая поступает с микропроцессора.

Если шина адреса является однонаправленной, то источником адреса является только одно устройство (например, МП), но тогда один из режимов работы МПС может оказаться невозможным – прямой доступ к памяти (захват магистрали, DMA).

Шина данных

Шина данных служит для пересылки данных между ЦП и памятью или ЦП и устройствами ввода/вывода. Эти данные могут представлять собой как команды ЦП, так и информацию, которую ЦП посылает в порты ввода/вывода или принимает оттуда. Таким образом, данные по шине данных могут передаваться от одного устройства к другому в любом направлении.

Шина данных DB (Data Bus) принципиально является двунаправленной. Она предназначена для передачи данных между блоками МПС. Информация по одним и тем же линиям DB может передаваться в двух направлениях — как к МП, так и от него. Варианты условных обозначений двунаправленной шины показаны на рис. 1.4.

Рис.1.4. Варианты условных обозначений двунаправленной параллельной 8-разрядной шины

Разрядность шины данных определяется разрядностью процессора, то есть количеством двоичных разрядов, которые могут обрабатываться или передаваться процессором одновременно. Разрядность процессоров постоянно увеличивается по мере развития компьютерной техники.

В МП 8088 шина данных имеет разрядность (ширину) 8 бит. В МП 8086, 80186, 80286 ширина шины данных 16 разрядов; в МП 80386, 80486, Pentium и Pentium Pro — 32 разряда.

Подчеркнем, что ШД всегда принципиально двунаправлена (иначе либо чтение, либо запись будут запрещены).

Двунаправленность сводится к тому, что на одну и ту же линию шины в разные моменты времени должны иметь возможность выдавать данные несколько устройств (модулей).

Для того, чтобы модули не мешали друг другу при работе на общую шину, существует 2 варианта исполнения выходных каскадов элементов, работающих на линию системной магистрали:

— элемент с тремя состояниями (с z-состоянием);

— схема с открытым коллектором (рис. 1.5).

Рис.1.5 Выход с открытым коллектором

Шина управления

По шине управления передаются сигналы, определяющие характер обмена информацией по магистрали. Сигналы управления определяют, какую операцию — считывание или запись информации из памяти нужно производить, синхронизируют обмен информацией между устройствами и т.д.

Шина управления СВ (Control Bus) предназначена для передачи управляющих сигналов. Хотя направление управляющих сигналов может быть разным, однако шина управления не является двунаправленной, поскольку для сигналов разного направления используются отдельные линии.

В основу построения подавляющего большинства компьютеров положены следующие общие принципы, сформулированные в 1945 г. американским ученымДжоном фон Нейманом.

1. Принцип программного управления. Программа состоит из набора команд, выполняющихся процессором автоматически в определенной последовательности.

2. Выборка программы из памяти осуществляется с помощью счетчика команд. Этот регистр процессора последовательно увеличивает хранимый в нем адрес очередной команды на длину команды. А так как команды программы расположены в памяти друг за другом, то тем самым организуется выборка цепочки команд из последовательно расположенных ячеек памяти. Если же нужно после выполнения команды перейти не к следующей, а к какой-то другой, используются командыусловного илибезусловного перехода, которые заносят в счетчик команд номер ячейки памяти, содержащей следующую команду. Выборка команд из памяти прекращается после достижения и выполнения команды «стоп». Таким образом,процессор исполняет программу автоматически, без вмешательства человека.

3. Принцип однородности памяти. Программы и данные хранятся в одной и той же памяти, поэтому компьютер не различает, что хранится в данной ячейке памяти – число, текст или команда. Над командами можно выполнять такие же действия, как и над данными.

Это открывает целый ряд возможностей. Например,программа в процессе своего выполнения также может подвергаться переработке, что позволяет задавать в самой программе правила получения некоторых ее частей (так в программе организуется выполнение циклов и подпрограмм).

Более того, команды одной программы могут быть получены как результаты исполнения другой программы. На этом принципе основаныметоды трансляции – перевода текста программы с языка программирования высокого уровня на язык конкретной машины.

4. Принцип адресности. Структурно основная память состоит из перенумерованных ячеек. Процессору в произвольный момент времени доступна любая ячейка. Отсюда следует возможность давать имена областям памяти так, чтобы к запомненным в них значениям можно было впоследствии обращаться или менять их в процессе выполнения программ с использованием присвоенных имен.

Компьютеры, построенные на перечисленных принципах, относятся к типуфон-неймановских. Но существуют компьютеры, принципиально отличающиеся от фон-неймановских. Для них, например, может не выполняться принцип программного управления, т. е. они могут работать без счетчика команд, указывающего текущую выполняемую команду программы. Для обращения к какой-либо переменной, хранящейся в памяти, этим компьютерам необязательно давать ей имя. Такие компьютеры называются не фон-неймановскими.

ШИНЫ АДРЕСА, ДАННЫХ И УПРАВЛЕНИЯ

Шина адреса. Микропроцессор КР580ИК80А имеет 16-разрядную шину адреса А0-А15. Эта шина выполняет две функции. Первая функция состоит в передаче адреса ячейки памяти (стека) при обращении к памяти (стеку). С помощью 16 разрядов шины адреса можно адресовать 2 16 ячеек памяти (т. е. 64 Кбайта). Вторая функция шины адреса — это передача адреса внешнего устройства при выполнении команд IN и OUT. В этом случае адрес внешнего устройства появляется на линиях АО-А7 и дублируется на линиях А8-А15. Так как для передачи адреса внешнего устройства используется фактически только восемь разрядов, то можно адресовать 256 (2 s ) различных внешних устройств ввода/вывода.

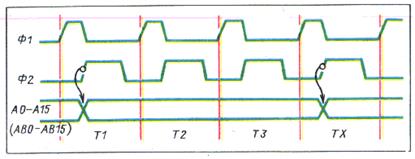

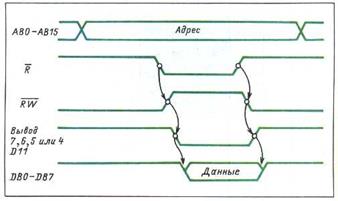

Временная диаграмма работы шины адреса приведена на рис. 6.3. Адрес появляется на шине по фронту сигнала Ф2 в такте Т1 и поддерживается три такта до фронта сигнала Ф2 в такте ТХ. Такт ТХ может быть четвертым тактом (Т4) машинного цикла, если цикл имеет более трех тактов, и может быть тактом Т1 следующего машинного цикла, если данный цикл имеет три такта.

Рис. 6.3. Временная анаграмма работы шины адреса

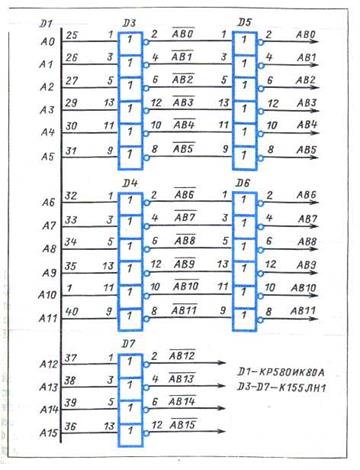

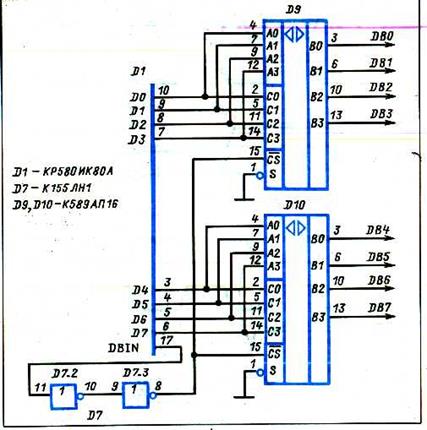

Каждая линия шины адреса является ТТЛ-выходом с тремя состояниями и нагрузочной способностью, равной единице. Так как шину адреса необходимо подавать на многие блоки ПМ-ЭВМ, то необходимо буферизовать ее линии, т. е. увеличить их нагрузочную способность. Для этого каждая линия подключается к входу схемы, состоящей из двух последовательно включенных инверторов (рис. 6.4). В результате на выходе второго инвертора имеется сигнал такого же уровня, как и на входе первого, но выход инвертора микросхемы К155ЛН1 имеет нагрузочную способность, равную 10.

Шина данных. Микропроцессор КР580ИК80А имеет 8-разрядную двунаправленную шину данных DO — D7. Шина данных выполняет две функции. Первая функция — передача управляющего слова, вторая — обмен информацией между регистрами микропроцессора и блоками микро-ЭВМ. Шина данных — единственная двунаправленная шина микропроцессора. Ее выходы также являются выходами с тремя состояниями.

Рассмотрим функцию передачи управляющего слова. Известно (см. § 6.2), что микропроцессор КР580ИК80А имеет 10 типов машинных циклов. Информация о том, какого типа цикл будет выполняться, передается в начале каждого цикла по линиям шины данных и называется управляющим словом. Все управляющие слова перечислены в табл. 6.2. Управляющее слово или только его часть можно запомнить с помощью дополнительных триггеров и использовать затем для формирования сигналов шины управления. Как это делается, будет описано ниже.

Рис. 6.4. Шина адреса

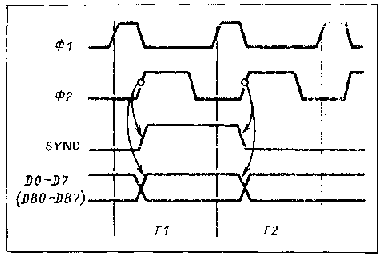

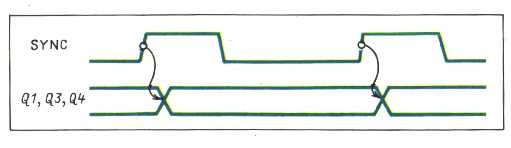

Для того чтобы показать, что идет процесс передачи управляющего слова, используется выход микропроцессора SYNC. Временная диаграмма приводится на рис. 6.5. Из нее видно, что передача управляющего слова по шине данных начинается по фронту сигнала Ф2 в такте Т1 и заканчивается по тому же фронту сигнала Ф2 в такте Т2.

Рис. 6.5. Временная диаграмма процесса передачи управляющего слова

Рассмотрим вторую функцию шины данных — обмен информацией между регистрами микропроцессора и блоками микро-ЭВМ. Во время циклов ВЫБОРКА КОМАНДЫ, ЧТЕНИЕ ИЗ ПАМЯТИ, ЧТЕНИЕ ИЗ СТЕКА, ВВОД С ВНЕШНЕГО УСТРОЙСТВА, ПРЕРЫВАНИЕ информация передается по шине данных в один из внутренних регистров микропроцессора из какого-либо блока микро-ЭВМ, а во время циклов ЗАПИСЬ В ПАМЯТЬ, ЗАПИСЬ В СТЕК, ВЫВОД НА ВНЕШНЕЕ УСТРОЙСТВО — из внутреннего регистра в какой-либо блок.

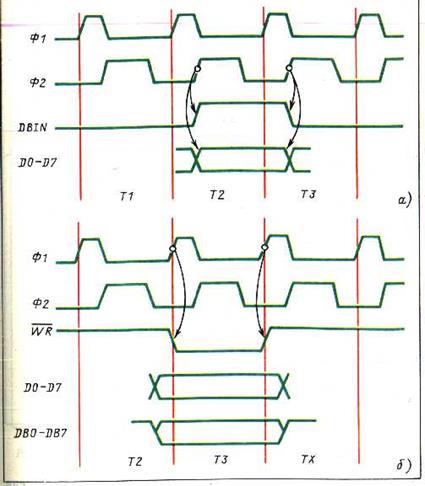

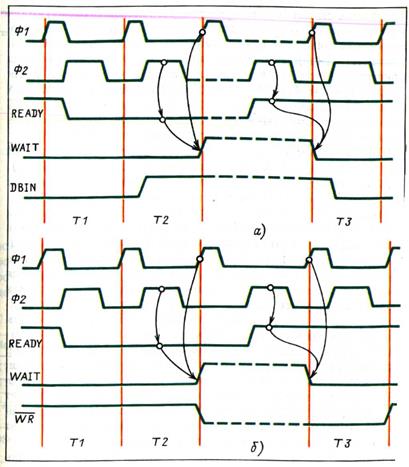

Читайте также: Внедорожные шины из китая

Для указания направления передачи информации по шине данных микропроцессор имеет два выхода: DBIN и WR. Когда информация передается в микропроцессор, то в этом машинном цикле на выходе DBIN появляется высокий уровень (рис. 6.6,а). Сигнал DBIN появляется по фронту сигнала Ф2 в такте Т2 и снимается по фронту Ф2 в такте ТЗ. Именно в это время внешние схемы должны поместить на шину данных код, который должен быть записан в один из внутренних регистров. Когда информация передается из микропроцессора, то в этом машинном цикле вырабатывается сигнал WR низкого уровня (рис. 6.6,6). Этот сигнал вырабатывается по фронту сигнала Ф1 в такте Т2 и снимается по фронту Ф1 в такте Т4 этого же машинного цикла (если цикл состоит более чем из трех тактов) или в такте Т1 следующего машинного цикла (если данный цикл состоит из трех тактов). На шине данных ЕЮ — D7 немного ранее появления сигнала WR микропроцессор помещает данные и снимает их позднее снятия сигнала WR, поэтому внешние схемы могут использовать этот сигнал для управления записью информации.

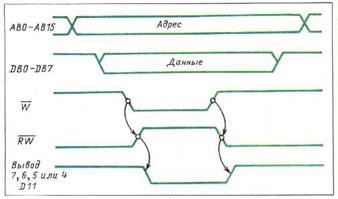

Рис. 6.6. Временная диаграмма работы шины данных

Каждая линия шины данных имеет единичную нагрузочную способность и поэтому нуждается в буферизации. Поскольку линии шины данных двунаправленны, необходим и двунаправленный буфер. Схема такого буфера, состоящая из двух микросхем К589АП16 (D9, D10), приводится на рис. 6.7. На входы 1 микросхем D9, D10 подан низкий уровень, и поэтому они работают все время в режиме передачи информации. Направление передачи определяется уровнем буферизованного сигнала DBIN, который подключен к входам 15 микросхем D9, D10. 3аметим, что направление передачи не управляется сигналами WR и SYNC .

Если уровень сигнала DBIN высокий, то шинные формирователи передают информацию в направлении к микропроцессору (от DBO — DB7 к DO — D7), если нет — то в обратном направлении (от ЕЮ — D7 к DBO — DB7), т. е. направление передачи шинных формирователей при низком уровне сигнала DBIN соответствует тому, которое должно быть при выработке сигналов WR и SYNC.

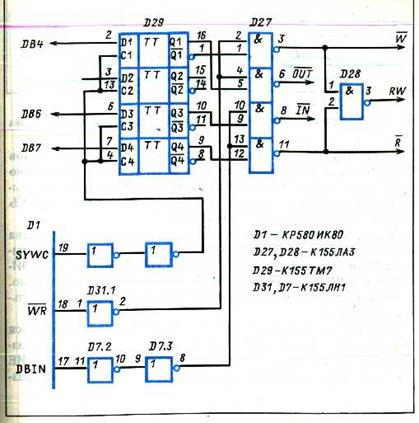

Шина управления. Микропроцессор КР580ИК80А не обладает готовой шиной управления, как шиной адреса и шиной данных. Поэтому эта шина организуется с помощью дополнительной внешней схемы (микросхемы D27, D29), называемой иногда системным контроллером (СК), которая использует управляющее слово и управляющие сигналы микропроцессора (рис. 6.8). Часть разрядов управляющего слова (D4, D6, D7) фиксируется в триггерах микросхемы К155ТМ7 (D29) по срезу сигнала SYNC (рис. 6.9). Сигнал SYNC пропущен через два инвертора для увеличения нагрузочной способности (эта схема, хотя и работоспособна, не будет применяться в ПМ-ЭВМ). Позднее будет приведена схема для фиксации управляющего слова, где сигнал на управляющие входы триггеров будет вырабатываться с помощью микросхемы КР580ГФ24. Сигналы шины управления вырабатываются с помощью сигналов с выходов триггеров микросхем D29 и сигналов DBIN и WR.

Рис. 6.9. Временная диаграмма работы фиксаторов управляющего слова

В ПМ-ЭВМ команды, данные и содержимое стека хранятся в едином блоке памяти, состоящем из ОЗУ и ПЗУ. Поэтому Для управления чтением из блока достаточно иметь один сигнал R, который будет вырабатываться при выполнении машинных циклов ВЫБОРКА КОМАНДЫ, ЧТЕНИЕ ИЗ ПАМЯТИ, ЧТЕНИЕ ИЗ СТЕКА. Назовем условно эту группу циклов ЧТЕНИЕ. Для управления записью в блок также достаточно иметь один сигнал W, который будет вырабатываться при выполнении машинных циклов ЗАПИСЬ В ПАМЯТЬ, ЗАПИСЬ В СТЕК. Эту группу назовем ЗАПИСЬ.

Для управления вводом и выводом на внешние устройства необходимы два сигнала OUT и IN, которые будут вырабатываться при выполнении циклов ВЫВОД НА ВНЕШНЕЕ УСТРОЙСТВО и ВВОД С ВНЕШНЕГО УСТРОЙСТВА соответственно.

Формирование сигналов шины управления поясним, пользуясь табл. 6.3.

| Тип цикла или группы циклов | Вырабатываемый сигнал DBIN или WR | Используемый разряд | Уровень напряжения на выхо дах триггеров D29 микросхемы | Вырабаты- ваемый сигнал шины управ- ления | |||

| ЧТЕНИЕ | DBIN | D7 | Н | Н | L | L | R, RW |

| ЗАПИСЬ | WR | D4 | L | Н | L | L | W, RW |

| ВЫВОД НА ВНЕШНЕЕ УСТРОЙСТВО | WR | D4 | L | L | Н | L | OUT |

| вводе ВНЕШНЕГО УСТРОЙ- СТВА | DBIN | D6 | L H | L | H | IN |

Рис. 6.10. Временная диаграмма циклов чтения и записи с переходом в режим ожидания:

а — цикл чтения; б — цикл записи

Для формирования сигнала R естественно воспользоваться разрядом D7 управляющего слова, так как именно в этом разряде имеется сигнал высокого уровня в циклах группы ЧТЕНИЕ (см. табл. 6.2), а для формирования сигналов OUT и IN — разрядами D4 и D6, потому что именно в этих разрядах сигнал имеет высокий уровень при выполнении соответствующих циклов и низкий уровень во всех остальных циклах. Сложнее дело обстоит с формированием сигнала W для циклов группы

ЗАПИСЬ. Казалось, было бы естественно воспользоваться разрядом D1 управляющего слова, в котором передается сигнал низкого уровня для циклов группы ЗАПИСЬ. Но в этом разряде сигнал низкого уровня бывает также и в цикле ВЫВОД НА ВНЕШНЕЕ УСТРОЙСТВО, и так как в этом цикле также вырабатывается сигнал WR, то пришлось бы усложнять схему, чтобы сформировать два разных сигнала W и OUT. Поэтому для формирования сигнала W используется инвертированный разряд D4. Соответствующий ему сигнал снимается с инверсного выхода триггера (вывод 7). Этот сигнал имеет высокий уровень и для циклов группы ЧТЕНИЕ и ВВОД С ВНЕШНЕГО УСТРОЙСТВА (см. табл. 6.2), но при этом не формируются сигналы W и OUT (так как не в ырабатывается сигнал WR), а формируются лишь сигналы R и IN (так как вырабатывается сигнал DBIN).

Сигнал высокого уровня RW формируется из сигнала R или W и управляет работой дешифратора адреса (см. § 7.2). В заключение опишем еще некоторые управляющие сигналы микропроцессора КР580ИК80А и их функции.

Вход READY используется для того, чтобы удлинить циклы ввода и вывода информации в микропроцессор и обеспечить таким образом возможность его работы с менее быстродействующими устройствами. Если во время высокого уровня сигнала Ф2 в такте Т2 какого-либо цикла на вход READY подается высокий уровень, то происходит нормальный цикл ввода или вывода информации. Если же подается низкий уровень, то микропроцессор с этого момента прекращает свою работу, сохраняя на всех выходах имеющиеся уровни сигналов (рис. 6.10). Такой режим называется режимом ожидания. Микропроцессор сигнализирует о том, что он находится в режиме ожидания, выработкой сигнала WAIT высокого уровня. В режиме ожидания микропроцессор не выполняет никаких операций и может находиться как угодно долго — до тех пор, пока не будет подан сигнал READY высокого уровня. После этого он завершает начатую операцию и продолжает далее свою работу.

Вход RESET используется для начального запуска микропроцессора и для повторных перезапусков. При подаче высокого уровня на этот вход микропроцессор прекращает свою работу, помещает во все разряды счетчика команд нули и бездействует до тех пор, пока на входе RESET остается высокий уровень. Как только высокий уровень снимается, он начинает выполнять команду, расположенную в ячейке памяти с нулевым адресом.

И СХЕМА ПОШАГОВОГО ИСПОЛНЕНИЯ ПРОГРАММ

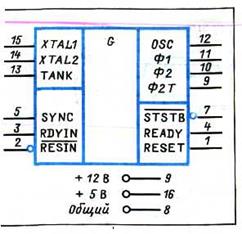

Для того чтобы получить тактовые импульсы с необходимыми для микропроцессора КР580ИК80А параметрами (см. § 6.2, рис. 6.2), можно использовать микросхему КР580ГФ24 (рис. 6.11, табл. 6.4). Эта микросхема является тактовым генератором, специально сконструированным для данного микропроцессора, и выполняет еще ряд дополнительных функций.

Рис. 6.11. Тактовый генератор КР580ГФ24

| Название | Назначение вывода |

| XTAL1 XTAL2 | Выводы для подключения кварцевого резонатора |

| TANK | Вывод, используемый при применении кварцевого резонатора с обертоном |

| OSC | Выход для синусоидального сигнала с частотой кварцевого резонатора |

| Ф1.Ф2 | Выходы для тактовых импульсов |

| Ф2Т | Выход для тактовых импульсов Ф2, но ТТЛ-уровня |

| SYNC | Вход для сигнала SYNC микропроцессора |

| STSTB | Выход для синхронизированного сигнала SYNC |

| — | Вход для асинхронного сигнала сброса |

| RESIN | |

| RESET | Выход для синхронизированного сигнала RESET микропроцессора |

| RDYIN | Вход для асинхронного сигнала готовности |

| READY | Выход для синхронизированного сигнала READY микропроцессора |

Рис. 6.12. Временные диаграммы синхронизации сигналов при помощи КР580ГФ24:

а — сигнал RESET; б — сигнал READY; в — сигнал SYNC

Опишем более подробно функции выводов тактового генератора. Выводы XTAL1 и XTAL2 предназначены для подключения кварцевого резонатора для стабилизации частоты генератора. При этом частота тактовых импульсов Ф1 иФ2 равняется 1/9 частоты кварцевого резонатора (так, в ПМ-ЭВМ при резонаторе на частоту 9 МГц частота тактовых импульсов равна 1 МГц). На выходах Ф1 и Ф2 вырабатываются тактовые импульсы, удовлетворяющие всем предъявляемым для микропроцессора КП580ИК80А требованиям. На выходе OSC вырабатывается синусоидальный сигнал с частотой, которую имеет кварцевый резонатор. Все оставшиеся выводы (т. е. кроме Ф1, Ф2 и OSC) работают с сигналами, имеющими ТТЛ-уровни. На выходе Ф2Т вырабатывается сигнал, идентичный Ф2, но имеющий ТТЛ-уровень, который может быть использован для синхронизации каких-либо устройств в микро-ЭВМ.

Рис. 6.13. Схема подключения тактового генератора к микропроцессору

Три входа SYNC, RESIN, RDYIN являются входами для асинхронных сигналов. Эти сигналы могут менять свой уровень в любой момент времени. Внутри КР580ГФ24 с помощью специальных схем из этих сигналов формируются три выходных сигнала STSTB, RESET, READY, синхронизированных с тактовыми импульсами (рис. 6.12).

Читайте также: Can шина магнитола поло седан

Тактовый генератор подключается к микропроцессору, как показано на рис. 6.13. К входу RESIN подключена кнопка СБРОС. Параллельно кнопке СБРОС подключен конденсатор С1, Если эта кнопка не нажата, то конденсатор С1 заряжен и на вход HESIN поступает высокий уровень. Следовательно, на вход RESET микропроцессора поступает низкий уровень, что позволяет ему нормально работать. Если нажать кнопку СБРОС, то на вход RESET поступит высокий уровень и работа микропроцессора будет прервана (см. § 6.3). Конденсатор С1 служит для начального запуска микропроцессора после включения питания. После включения питания С1 разряжен и на вход RESIN поступает низкий уровень. Затем конденсатор заряжается, напряжение на входе RESIN экспоненциально возрастает и в какой-то момент времени достигает высокого уровня. Это приводит к выработке сигнала RESET низкого уровня, разрешающего работу микропроцессора. Вход RESIN имеет специальную схему (триггер Шмидта), которая перерабатывает медленно меняющийся при заряде конденсатора входной сигнал в нормальный ТТЛ-фронт.

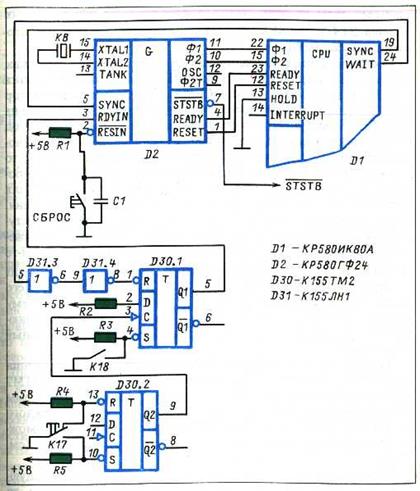

ПМ-ЭВМ можно снабдить схемой пошагового выполнения программы (рис. 6.13), построенной на микросхеме К155ТМ2 (D30) и двух инверторах (D31.3, D31.4). С помощью этой схемы выполнение программы приостанавливается в середине каждого машинного цикла. Состояния шины данных в этот момент можно наблюдать на индикаторах одного из портов вывода (см. §7.3).

Схема пошагового выполнения программы работает следующим образом. Если контакты выключателя К18 замкнуты, то на вход 4 триггера D30.1 подается низкий уровень. На вход 1 также подается низкий уровень с выхода WAIT через буфер, состоящий из двух инверторов. В результате этого на выходе 5 триггера имеется высокий уровень, который, поступая на вход RDYIN, обеспечивает сигнал READY высокого уровня, что позволяет микропроцессору работать в нормальном режиме. Для перехода в режим пошагового выполнения программы необходимо разомкнуть контакты выключателя К18. Тогда на входе 4 триггера D30.1 будет высокий уровень, а на входе 1 — низкий уровень. Это приведет к тому, что на выходе 5 появится низкий уровень и микропроцессор перейдет в режим ожидания. После перехода в режим ожидания на выходе WAIT и на входе 1 триггера установится высокий уровень. В этом состоянии схема может находиться неограниченно долго. Если теперь подать на вход 3 триггера D30.1 фронт, то на выходе 5 появится высокий уровень. Микропроцессор снимет сигнал WAIT высокого уровня, закончит начатый машинный цикл и начнет выполнять следующий машинный цикл. Сигнал WAIT низкого уровня вновь установит на выходе 5 триггера низкий уровень, что приведет к переходу микропроцессора в режим ожидания в середине следующего машинного цикла.

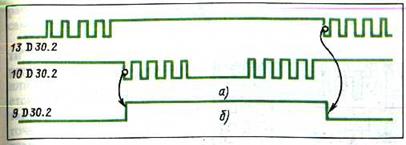

Рис. 6.14. Явление дребезга контактов:

а — реальная временная диаграмма, дребезг контактов; б — идеальная временная диаграмма

Для подачи импульсов на вход 3 триггера D30.1 используются кнопка К17 и схема для подавления дребезга контактов. Явление дребезга контактов происходит при замыкании любых механических контактов вследствие неидеальности их поверхности. Вместо однократного замыкания или размыкания контакты замыкаются и размыкаются несколько раз. Так, при нажатии на кнопку К17 на выводах 13, 10 микросхемы D30.2 сигнал имеет форму, изображенную на рис. 6.i4. Чтобы сформировать сигнал, имеющий один срез, используется кнопка с двумя контактами: замыкающимся и размыкающимся при нажатии на нее. Когда один из контактов кнопки, соединенный с входами 10 и 13 микросхемы D30.2, замыкается, то первый из возникающих импульсов перебрасывает триггер, а остальные импульсы уже не влияют на его состояние. Таким образом, на выходе 9 формируются фронт при нажатии на кнопку К17 и срез при отпускании этой кнопки.

И ОСОБЕННОСТИ

РАБОТЫ ОСНОВНЫХ

БЛОКОВ ПМ-ЭВМ

ОБЩИЕ ПОЛОЖЕНИЯ

Выше была рассмотрена шинная архитектура, на основе которой строятся все современные микро-ЭВМ. Составные части или блоки микро-ЭВМ подключаются к шинам адреса, данных и управления. Эти шины служат для передачи информации от одного блока к другому, причем в определенный момент времени передатчиком может быть лишь один из блоков. В гл. 6 было рассмотрено устройство микропроцессорного блока, который хотя и является «сердцем» микро-ЭВМ, но не может самостоятельно работать без блока памяти и устройств ввода/вывода. Поэтому в данной главе рассматриваются функционирование и подключение к микропроцессорному блоку блока памяти (§ 7.2), устройств вывода — светодиодов и устройств ввода — клавиатуры (§ 7.3). Далее, в § 7.4, приводится полный текст программы-монитора, которая управляет работой микро-ЭВМ, в том случае, когда она не решает какую-либо задачу и позволяет пользователю с помощью кнопок клавиатуры и индикаторов вводить, отлаживать и запускать свои программы.

СТРУКТУРА ПАМЯТИ

Блок памяти состоит, как правило, из ОЗУ и ПЗУ. В ОЗУ и ПЗУ хранятся данные и программы пользователя. В ПЗУ помешаются те данные и программы, которые должны сохраняться при выключении питания. Во-первых, в ячейки ОЗУ информация может попадать, в результате работы какой-либо программы, во-вторых, пользователь может сам изменить их содержание при помощи клавиатуры.

Максимальное количество ячеек памяти (или «объем памяти»), к которым может обращаться при помощи своей 16-разрядной шины адреса микропроцессор КР580ИК80А, равно 2 16 , или 65 536. Обычно говорят: не 65 536 ячеек, а 64 К (1 К равняется 1024). Для решения некоторых задач оказывается мало и такого объема памяти, но для большинства применений достаточно использовать лишь его часть. С другой стороны, объем памяти, содержащейся в одной микросхеме, может быть меньше, чем максимальный объем, который может адресовать микропроцессор. Эти два обстоятельства, а также и то, что в составе памяти микро-ЭВМ необходимо иметь память с разными свойствами (ОЗУ и ПЗУ), приводят к специальным техническим решениям при конструировании памяти микро-ЭВМ.

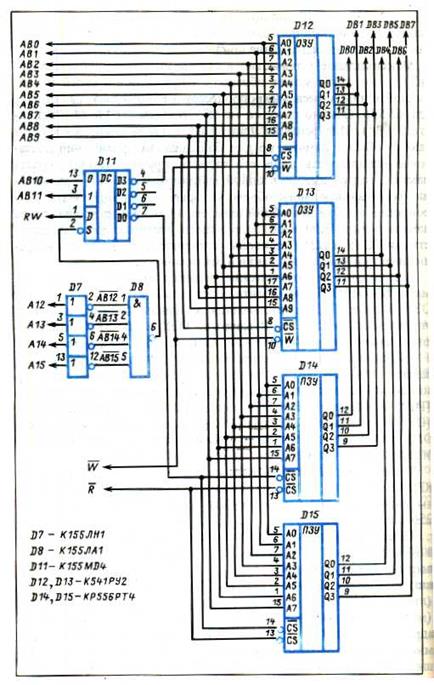

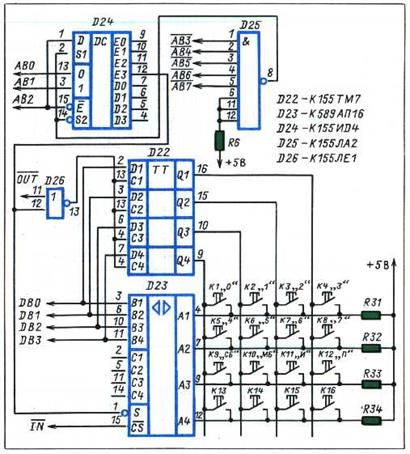

Рассмотрим эти технические решения на примере блока памяти ПМ-ЭВМ. Блок памяти, состоящий из двух микросхем ОЗУ и двух ПЗУ, подключается к шинам данных, адреса и управления (рис. 7.1). В качестве ОЗУ в ПМ-ЭВМ используются микросхемы статической памяти КР541РУ2 (см. гл. 4) с организацией 1024×4 бита. Поэтому для получения объема памяти 1 Кбайт (1024 байта) необходимо подключить две микросхемы, присоединив выводы данных одной микросхемы (D12) к линиям DBO-DB3 шины данных, а выводы другой (D13) — к линиям DB4 — DB7. Остальные выводы микросхем D12 и D13 подключаются к одним и тем же линиям. Таким образом составляется блок ОЗУ емкостью 1 Кбайт.

В качестве ПЗУ в ПМ-ЭВМ используются две микросхемы КР556РТ4 (D14, D15) с организацией 256×4 бит. Они включены аналогично микросхемам ОЗУ, т. е. организованы в блок 25 6 байтов.

Рис. 7.1. Схема блока памяти

Теперь рассмотрим, как размещается блок ОЗУ объемом 1 Кбайт и блок ПЗУ объемом 256 байт в пространстве адресов, вырабатываемых микропроцессором. Для того чтобы осуществить привязку блоков ОЗУ и ПЗУ, старшие разряды адреса (линии АВ10-АВ15) подаются на схему дешифрации адреса (микросхемы D8, D11, рис. 7.1). Шесть старших разрядов адреса АВ10-АВ15 определяют, к какому килобайту памяти микропроцессора будет произведено обращение. Десять младших разрядов адреса АВО-АВ9 адресуют байты памяти в пределах каждого килобайта. Каждому коду на АВ10-АВ15 соответствует один килобайт памяти, но вследствие того, что инвертированные линии АВ12-АВ15 шины адреса поступают на микросхему D8, сигнал с выхода которой разрешает или запрещает работу дешифратора D11, дешифратор D11 будет работать только при нулевых кодах на этих линиях. В зависимости от кода на линиях АВ10 — АВ15 низкий уровень будет появляться на одном из выходов 7, 6, 5 или 4 дешифратора D11 при условии, что на втором управляющем входе дешифратора (вывод 1) будет высокий уровень. В табл. 7.1 дается соответствие кода на линиях АВ 10 — АВ 15 номеру вывода D11.

В табл. 7.1 приводятся адрес первого байта, адрес последнего байта и условный номер килобайта памяти, к которому происходит обращение при определенном коде на линиях АВ10 — АВ15. Из пятой строки табл. 7.1 также видно, что если адрес, вырабатываемый микропроцессором, лежит в диапазоне от 010000Q до 177 OOOQ, то ни на одном из выходов дешифратора не будет низкого уровня, т. е. с помощью выходов этого дешифратора нельзя адресоваться к килобайтам с 4-го по 63-й.

Выходы дешифратора используются для привязки отдельных блоков памяти емкостью 1 Кбайт к определенным областям в пространстве адресов микропроцессора; для этого они соединены со входами микросхемы памяти, разрешающими их работу, а на адресные входы микросхемы памяти подаются младшие разряды адреса, которые осуществляют адресацию ячеек памяти внутри микросхем.

| Код на линиях АВ10— АВ1 5 | Номер вывода D11.на котором низкий уровень напряжения | Диапазон адресов области памяти в восьмеричном коде | Номер адресуемого ки- | |||||

| А15 | А14 | А13 | А12 | All | А10 | от адреса | до адреса | лобайта |

| 000 000 | 001 777 | |||||||

| 002 000 | 003 777 | |||||||

| 005 777 | ||||||||

| 006 000 | 007 777 | |||||||

| Любой другой код | — | 010 000 | 4-63 |

Рис. 7.1. Схема блока памяти

Блок из микросхем ПЗУ подключен так, что он занимает самые младшие адреса, начиная с 000 000Q. Это сделано для размещения программы-монитора, которая должна начинать работать сразу после включения микро-ЭВМ, или нажатия кнопки СБРОС, в результате чего вырабатывается сигнал RESET, по которому микропроцессор начинает выполнять команду, расположенную по адресу 000 OOOQ (т. е. в ПЗУ). Заметим,что для адресации 256 байтов ПЗУ достаточно восьми адресных линий ABO — AB7; линии АВ8, АВ9 излишни и поэтому к ПЗУ не подсоединены. В результате этого независимо от кода на линиях АВ8 и АВ9 адресуется байт ПЗУ, определяемый адресом на линиях ABO — AB7. Это приводит к тому, что один и тот же байт ПЗУ можно считывать по адресам, в разрядах АВ8, АВ9 которых находятся коды 00, 01, 10 или 11. Область памяти ПЗУ, состоящая из 256 байт, повторяется 4 раза в нулевом килобайте памяти. Ясно, что это повторение не мешает работе микропроцессора.

Читайте также: Шины якохама 215 70 r16 лето

Такая схема адресации с неиспользованием части разрядов адреса называется схемой с неполной дешифрацией адреса. При необходимости использовать весь нулевой килобайт и поместить в пространство его адресов еще три блока памяти по 256 байт в каждом нужно использовать для разрядов АВ8 и АВ9 полный дешифратор, устроенный так же, как для разрядов АВ10 и АВ11. Схема с неполной дешифрацией адреса приводит к тому, что используется не все адресное пространство, но зато требуется меньше микросхем для ее реализации, и поэтому такая схема часто применяется в простых микро-ЭВМ.

Блок из микросхем ОЗУ подключен к выходу 4 дешифратора D11, и поэтому килобайт ОЗУ адресуется как 3-й килобайт в адресном пространстве микропроцессора. На рис. 7.2 приведена карта распределения памяти в ПМ-ЭВМ.

Этого объема памяти достаточно для нормальной работы, но его можно при необходимости увеличить. Объем используемого ОЗУ можно увеличить до 3 Кбайт, ничего не переделывая в схеме дешифрации адреса, а просто подключением дополнительных блоков ОЗУ емкостью по 1 Кбайт к выходам 6 и 5 дешифратора D11 (рис. 7.1). Можно также увеличить объем используемого ПЗУ, если построить его из микросхем большей емкости, например из микросхем К573РФ1 с организацией 1024×8 бит (1 Кбайт) или микросхем КР556РТ5 емкостью 4 Кбита и с организацией 512×8 бит (0,5 Кбайта). В первом случае будет использоваться весь 0-й килобайт, а во 2-м ячейки ПЗУ будут повторяться во второй половине 0-го килобайта.

| 000 000 | |

| ПЗУ | |

| 000 377 | |

| 000 400 000 777 | Повторяется ПЗУ |

| 001 000 001 377 | Повторяется ПЗУ |

Рис. 7.2. Карта распределения памяти

Осталось рассмотреть подключение блока памяти к линиям шины управления. Линия R (рис. 7.1) подключена к входам 13 микросхем ПЗУ и разрешает их работу во время цикла считывания байта из ПЗУ. Линия W подключена к входам 10 микросхем ОЗУ и управляет записью байта в ОЗУ. Если на ней во время цикла обращения к ОЗУ поддерживается высокий уровень, то происходит считывание, а если низкий — то запись байта. Сигнал RW, вырабатывающийся и сигналом R, и сигналом W, служит Для того, чтобы разрешать работу дешифратора D11 только во время низкого уровня сигналов R и W. Это необходимо, чтобы считывание и запись в блок памяти происходили во время выра ботки сигналов R и W, которые формируются сигналами DBIN и WR микропроцессора, определяющими момент передачи информации по шине данных.

Рис. 7.3. Временная диаграмма работы блока памяти при чтении

Рис. 7.4. Временная диаграмма работы блока памяти при записи

Считывание из ОЗУ микропроцессор может выполнить в циклах ВЫБОРКА КОМАНДУ, ЧТЕНИЕ ИЗ ПАМЯТИ, ЧТЕНИЕ ИЗ СТЕКА а считывание из ПЗУ — только в циклах ВЫБОРКА КОМАНДЫ И ЧТЕНИЕ ИЗ ПАМЯТИ. Временные диаграммы сигналов шины адреса, данных и управления приведены на рис. 7.3. Запись информации в ОЗУ микропроцессор может выполнить в циклах ЗАПИСЬ В ПАМЯТЬ, ЗАПИСЬ В СТЕК. Временные диаграммы записи приведены на рис. 7.4.

КЛАВИАТУРА И ИНДИКАЦИЯ

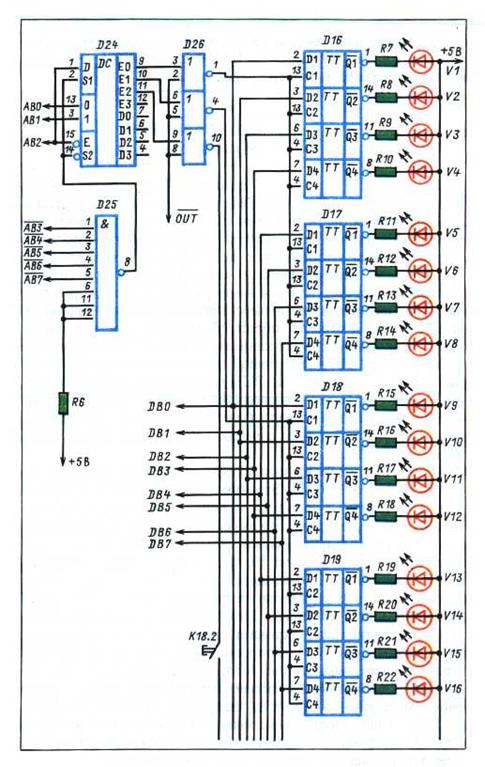

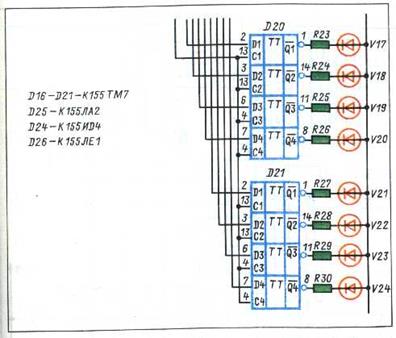

Устройства ввода/вывода необходимы для связи микро-ЭВМ с внешним миром. Без такой связи ее работа была бы бессмысленной. Устройства ввода/вывода бывают самые различные по конструкции и особенностям работы. Отличительной особенностью всех этих устройств является их способность перекодировать информацию из той формы, в которой она представляется в микро-ЭВМ, в форму, необходимую для связи с какими-либо приборами (для устройства вывода), и осуществлять обратный процесс для устройства ввода. Схема индикации и клавиатура микро-ЭВМ подключаются к линиям DBO-DJB7 шины данных, линиям ABO — AB7 шины адреса и линиям IN и OUT шины управления (рис. 7.5, 7.6). Схема индикации выполнена на базе трех байтовых (8-разрядных) портов вывода (микросхемы D16-D21), а схема клавиатуры — на базе одного 4-разрядного порта ввода (микросхемы D23).

Каждый из портов вывода схемы индикации выполнен из двух микросхем К155ТМ7. Эта микросхема представляет собой четыре D-триггера с прямыми и инверсными выходами (см. гл. 4). Входы триггеров подключены к линиям шины данных. Каждый выход D-триггера микросхемы К155ТМ7 имеет нагрузочную способность, равную 10, т. е. к нему можно подсоединить 10 стандартных ТТЛ-входов, а это значит, что при низком уровне на выходе (напряжение меньше или равно 0,4 В) в него может втекать ток до 16 мА. Это позволяет подключать свето-Диоды для индикации состояний триггеров непосредственно к их выходам (рис. 7.7). Сопротивление включается последовательно с светодиодом для того, чтобы ограничить ток до 5-10 мА. Для индикации можно использовать любые диоды с рабочим током 5 — 15 мА, например АЛ102А, АЛ102Г, АЛ112А-М. Светодиоды подключены к инверсным выходам триггеров, поэтому они зажигаются, если в соответствующий триггер записывается 1, и гаснут, если записывается 0.

В схему индикации и клавиатуры входит микросхема К155ИД4 (D24). Эта микросхема представляет собой два дешифратора-мультиплексора (см. гл. 5), объединенные в один дешифратор трехразрядного двоичного кода в код «один из восьми». Это достигается соединением входов 1 и 75, а также входов 2 и 14 микросхемы. На вход 13 подается первый разряд кода, на вход 3 — второй, а на объединенные входы 1и 15 —третий разряд двоичного кода, предназначенного для преобразования в код «один из восьми». Объединенные входы 2 и 14 служат для запрещения работы дешифратора. При этом на них должен быть подан высокий уровень. Такой режим работы микросхемы К155ТД4 представлен в табл. 7.2.

Рис. 7.5. Схема индикации (продолжение)

Микросхема К155ИД4 (D24) вместе с микросхемой К155ЛА2 (D25) составляет схему дешифрации адреса для выбора внешних устройств ввода и вывода. Эта схема функционирует следующим образом. Входы 13, 3 и 1/15 микросхемы D24 подсоединены к линиям ABO, AB1, АВ2 шины адреса, а входы микросхемы D25 — подсоединены к инвертированным линиям шины адреса АВЗ, АВ4, АВ5, АВ6, АВ7. Поэтому когда во время выполнения команд IN или OUT на линиях шины адреса появляется адрес внешнего устройства (см. гл. 6), на одном из выходов микросхемы U24 появляется низкий уровень. Соответствие выполняемой команды IN или OUT тем выходам D24, на которых появляется низкий уровень, приведено в табл. 7.3.

Рис. 7.7. Схема подключения све-тодиода к выходу порта вывода

| Таблица | 7.2 | ||||||||||

| Входы | Выходы | ||||||||||

| 2/14 | 1/15 | ||||||||||

| Н | X | X | X | Н | Н | Н | Н | Н | Н | Н | Н |

| Т | L | L | L | L | Н | Н | Н | Н | Н | Н | Н |

| Т | L | L | Н | Н | L | Н | Н | Н | Н | Н | Н |

| т | L | Н | L | Н | Н | L | Н | Н | № | Н | Н |

| I, | L | Н | Н | Н | Н | Н | L | Н | Н | Н | Н |

| т, | Н | L | L | Н | Н | Н | Н | L | Н | Н | Н |

| т, | Н | L | Н | Н | Н | Н | Н | Н | L | Н | Н |

| т, | Н | Н | L | Н | Н | Н | Н | Н | Н | L | Н |

| L | Н | Н | Н | Н | Н | Н | Н | Н | Н | Н | L |

| Таблица | 7.3 | ||||||||||

| Команда | Код на линиях шины адреса во время выполнения команды | Вывод микросхемы D24 с низким уровнем | |||||||||

| АВ7 | АВ6 | АВ5 | АВ4 | АВЗ АВ2 | АВ1 | АВО | |||||

| IN 000Q или 1 1 OUT 000 Q | 1 1 | ||||||||||

| IN 001 Q или 1 1 OUT 001Q | 1 1 | ||||||||||

| IN 002 Qили 1 1 OUT 002 Q | 1 1 | ||||||||||

| IN 003 Q или 1 1 OUT 003 Q | 1 1 | ||||||||||

| IN 004 Q или 1 1 OUT 004 Q | 1 1 | ||||||||||

| IN 005 Q или 1 1 OUT 005 Q | 1 1 | ||||||||||

| IN 00бQили 1 1 OUT 006 Q | Г 1 | ||||||||||

| IN 007Qили 1 1 OUT 00 7 Q | 1 1 |

| Таблица 7.4 | ||

| Команда | Микросхемы, составляющие порт ввода или вывода | Функция порта ввода или вывода |

| OUT 000 Q | D16, D17 | Индикация одного байта |

| OUT 001 Q | D18, D19 | То же |

| OUT 002 Q | D20, D21 | То же |

| OUT003Q | D22 | Вывод четырех битов для обслуживания клавиатуры |

| IN 003 Q | D23 | Ввод четырех битов для обслуживания клавиатуры |

Заметим, что если выполнить команду IN или OUT с отличным от перечисленных в табл. 7.3 адресом внешнего устройства, то ни на одном из выходов микросхемы D24 не появится низкого уровня. Из восьми возможных адресов для портов ввода и вывода в схеме индикации и клавиатуры используются три адреса 000 Q, 001Q и 002 Q, которые присвоены портам вывода, служащим для индикации, и один адрес 003 Q, который присвоен одновременно 4-битовым портам ввода и вывода, обслуживающим клавиатуру (табл. 7.4).

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле