Компьютерная Энциклопедия

Компьютерная Энциклопедия- Архитектура ЭВМ

- Компоненты ПК

- Интерфейсы

- Мини блог

- Самое читаемое

- Ввод-вывод

- Шина ISA

- Описание сигналов шины

- Временные диаграммы

- Чтение из порта ввода

- Запись в порт вывода

- Структурная схема модуля на базе шины ISA

- Буферизация содержимого системной шины. Схема декодирования адреса порта

- Буферизация содержимого системной шины

- Схема декодирования адреса порта

- ПК «Сплайн-Технолоджис»

- Профессиональный подход. Разумность решений.

- Новости

- Шина ISA

Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

Ввод-вывод

Шина ISA

Описание сигналов шины

OSC: Генератор. Высокочастотные импульсы с периодом 70 нс(14.31818 МГц).

CLOCK : Системная частота (от процессора).

RESET DRV : Этот сигнал используется для сброса или инициализации системной логики при включении питания или при низком уровне напряжения на линии. Он синхронизирован с задним фронтом CLOCK и имеет активный высокий уровень (от процессора ).

SA0-SA19: Биты адреса с 0 по 19. Эти линии используются для адресации памяти и устройств ввода/вывода в системе. 20 адресных линий позволяют адресовать до 1 Мбайта памяти. SA0 — это младший значащий разряд, а SA19 — старший значащий разряд. Сигналы генерируются либо процессором или устройством ПДП. Они имеют активный высокий уровень. (от процессора ).

SD0-SD15: Биты данных с 0 по 15. Эти сигналы служат для передачи данных между процессором, памятью и внешними устройствами. D0 — это младший разряд, а D15- старший. Они имеют активный высокий уровень (двунаправлен).

BALE :Разрешение селекции адреса. Этот сигнал вырабатывается контроллером шины 82288 и используется на системной плате для защелкивания верного значения адреса от процессора. Он доступен на канале ввода/вывода как индикатор того, что значение адреса на магистрали верное (если используется вместе с AEN). Адрес защелкивается по заднему фронту сигнала (двунаправлен).

I/ O CH CK: Проверка канала. Этот сигнал обеспечивает процессор информацией об ошибках четности памяти или внешних устройств в канале. Когда этот сигнал переходит в низкое состояние, регистрируется ошибка четности (в процессор).

I /O CHRDY : Готовность канала. Этот сигнал, обычно высокий, — переводится в низкое состояние памятью или внешним устройством для продления цикла обращения. Он дает возможность с минимальными затратами присоединять к системе устройства с низким быстродействием. Любое медленное устройство, используя этот сигнал, должно держать его в низком состоянии до тех пор, пока оно не проведет операцию распознавания адреса и не выполнит команду чтения или записи. Однако этот сигнал не должен оставаться в низком состоянии дольше 10 циклов синхронизации системы. Цикл обращения к памяти или внешнему уст-ройству увеличивается на целое число циклов синхронизации (в процессор).

IRQ3- IRQ15: Запрос на прерывание 3-15. Эти сигналы используются для передачи сообщения процессору о том, что устройство требует обслуживания. Они имеют разный приоритет. IRQ3 — с наивысшим приоритетом, а IRQ15 — с низшим. Запрос на прерывание вырабатывается при переходе сигнала из низкого состояния в высокое и удержании его до распознавания процессором (в процессор ).

IOR : Команда чтения из устройства. Данный сигнал указывает внешнему устройству на необходимость выставить свои данные на шину данных. Он может вырабатываться процессором или устройством ПДП. Активный уровень сигнала — низкий (от процессора ).

IOW: Команда записи в устройство. Этот сигнал сообщает устройству о необходимости ввода данных с магистрали. Он может вырабатываться как процессором, так и внешним устройством. Активный уровень сигнала — низкий (от процессора ).

SMEMR: Команда чтения памяти из пространства 1 Мбайт. Этот сигнал указывает памяти, что она должна выставить свои данные на шину. Он может вырабатываться как процессором, так и устройством ПДП. Активный уровень сигнала — низкий (от процессора ).

SMEMW: Команда записи в память из пространства 1 Мбайт. Данный сигнал указывает памяти на необходимость прочитать данные, выставленные на шину данных. Он может вырабатываться как процессором, так и устройством ПДП . Активный уровень сигнала -низкий (от процессора ).

MEMR : Команда чтения памяти: Этот сигнал указывает памяти, что она должна выставить свои данные на шину. Он может вырабатываться как процессором, так и устройством ПДП. Активный уровень сигнала — низкий (от процессора ).

MEMW: Команда записи в память. Данный сигнал указывает памяти на необходимость прочитать данные, выставленные на шину данных. Он может вырабатываться как процессором, так и устройством ПДП. Активный уровень сигнала — низкий (от процессора ).

D RQ0-DRQ3 DRQ5-DRQ7: Запрос ПДП 0-7. Данные сигналы являются асинхронными запросами канала периферийными устройствами для выполнения операций ПДП. Они имеют различный приоритет. DRQ7 — низший, а DRQ0 — высший. Запрос генерируется переводом соответствующего сигнала в активное (высокое) состояние. Сигнал должен удерживаться в высоком состоянии до тех пор, пока не станет активной соответствующая линия DACK (в процессор).

DACK0 — DACK7: Подтверждение ПДП 0-7. Эти сигналы используются для ответа на соответствующие запросы ПДП (0-7). Они имеют низкий активный уровень (от процессора).

AEN: Разрешение адреса. Данный сигнал используется для отключения процессора и других устройств от канала для проведения цикла ПДП. Когда этот сигнал активен (высокий), контроллер ПДП получает шину адреса, шину данных, а также линии чтения и записи (от процессора).

T/C: Счетчик завершения. На этой линии появляется импульс, когда достигнуто состояние счетчика завершения какого-либо устройства ПДП (от процессора).

REFRESH: Запрос на регенерацию динамической памяти (от процессора).

LA17-LA23: Незащелкиваемые адресные линии А17-А23 (двунаправлен).

SBHE: Показывает что старший байт данных находится на старшей шине данных SD8-SD15 (двунаправлен).

0WS: Сигнал показывает процессору что текущий цикл шины может быть выполнен без дополнительных тактов ожидания (в процессор).

MASTER: Сигнал перехвата управления внешним устройством системной магистрали (в процессор).

MEM CS16 : Сигнал, подтверждающий то, что процессор может работать с этой памятью 16-разрядными словами без побайтовой распаковки (в процессор).

IO CS16: Аналогично, только с устройствами ввода/вывода (в процессор).

Помимо описанных сигналов, в канале ввода/вывода имеется ряд линий питания для устройств, подключенных к каналу.

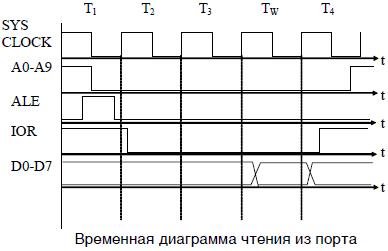

Временные диаграммы

Чтение из порта ввода

Временная диаграмма операции чтения из порта (in port) занимает четыре такта опорной частоты и один такт ожидания (см. рисунок ниже). Само чтение данных происходит в начале четвертого периода. При необходимости удлинения времени чтения подают сигнал I/O CH RDY готовности канала, который увеличивает такт ожидания. Максимальное время ожидания определяется необходимостью регенерации памяти.

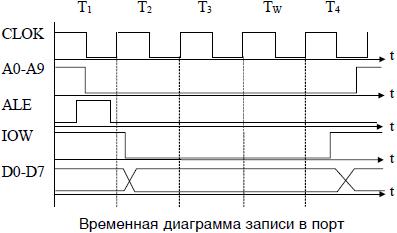

Запись в порт вывода

Временная диаграмма операции записи в порт (out port) занимает то же время, что и чтения из порта (см. рисунок ниже). Данные на шине находятся в течение всей длительности синхросигнала IOW.

В порт можно записывать и соответственно считывать как байт так и слово (два байта). Второй байт может появиться на старших разрядах шины данных или после первого — на младших разрядах. В первом случае внешнее устройство должно сформировать сигнал IO CS16, а процессор записать в (считать из) четный адрес порта. Если сигнал IO CS16 отсутствует, то запись первого и второго байта происходит в последовательные адреса портов, причем увеличение адреса порта на шине адреса происходит автоматически. При обращении к нечетным адресам считывается и записывается младший байт.

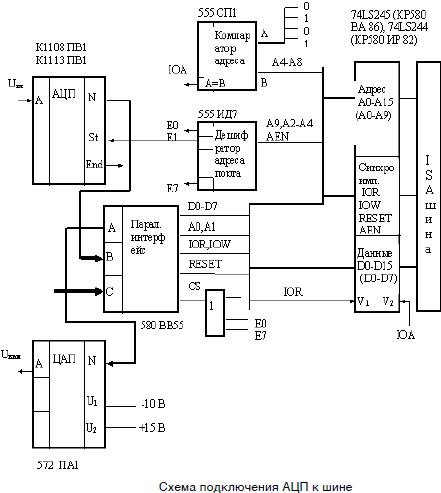

Структурная схема модуля на базе шины ISA

Подробная структурная схема модуля Plug in Data Acquisition Board приведена на рисунке (см. рисунок ниже). На рисунке показаны не только составляющие модуль элементы, но и перечислены микросхе-мы для их реализации.

В модуле можно выделить следующие элементы:

•буфер системной ши-ны,

•схему декодирования адреса порта,

•параллельный ввод-вывод КР580 ВВ55 (Intel 8255),

•микросхемы АЦП и ЦАП.

Буферизация содержимого системной шины. Схема декодирования адреса порта

Буферизация содержимого системной шины

Необходимость буферизации определяется следующими причинами:

•Защита канала от больших напряжений, замыканий на землю;

•Защита от большой нагрузки при подключении к каналу большого числа потребителей (более 5), которые увеличивают емкостную нагрузку, вследствие чего изменяют временные параметры.

В качестве буфера можно использовать шинные приемо-передатчики, подключенные к соответствующим линиям канала.

Читайте также: Can шина для магнитолы андроид что это такое

В модуле используются следующие микросхемы:

•однонаправленные приемо-передатчики — 74LS245 (КР580 ВА 86),

•двунаправленные приемо-передатчики — 74LS244 (КР580 ИР 82). Последние применены для буферизации шины данных и включаются по сигналу AEN, а направление передачи определяет сигнал IOW.

Схема декодирования адреса порта

Элемент декодирования адреса порта предназначен для определения порта модулем. Номер порта в модуле задан аппаратно, и при совпадении в процессе декодирования этого номера с пришедшим (по шине адреса) модуль откликается на команду ввода-вывода (происходят те или иные действия).

На рисунке ниже (схема подключения АЦП к шине) представлена двухкаскадная схема декодирования адреса. Она включает цифровой компаратор (555 СП1) и дешифратор (555 ИД7). На входе А компаратора жестко задан код 0101, а код адреса дешифратора определяется номером используемого выхода. Разряд А9 включает дешифратор. Младшие разряды А0, А1 задают номер канала параллельного интерфейса.

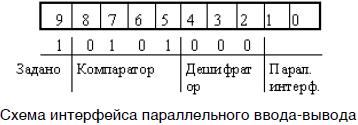

Адрес порта можно определить в соответствии с приведенной ниже схемой (схема интерфейса параллельного ввода-вывода).

Схема предназначена для подключения нескольких источников (приемников) данных к шине, а также для организации двунаправленного и стробируемого ввода-вывода (см. таблица ниже).

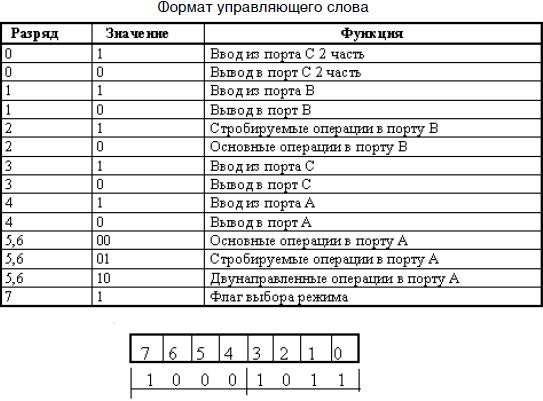

Микросхема параллельного интерфейса поддерживает несколько режимов работы по каждому выходу (А, В, С), выбор режима проводится подачей управляющего слова. Ниже приведен формат управляющего слова ().

Последняя картинка для того, чтобы порт А работал на вывод, а порты В,С — на ввод, необходимо записать управляющее слово.

В результате при работе со схемой (Схема подключения АЦП к шине) необходимо первоначально запрограммировать конфигурацию внутренних портов, а лишь затем считывать из АЦП или выводить в ЦАП информацию. Команды чтения и вывода аналогового сигнала будут иметь вид:

ПК «Сплайн-Технолоджис»

Профессиональный подход.

Разумность решений.

Новости

Шина ISA

Шина ISA ( I ndustrial S tandart A rhitecture) является фактически стандартной шиной для персональных компьютеров типа IBM PC/AT и совместимых с ними. Шина EISA , с которой ряд фирм выпускал персональные компьютеры, уступила шине PCI и в настоящее время используется редко.

шина AT компьютеров позволяет использовать на внешних платах как 16-разрядные устройства ввода/вывода, так и 16-разрядную память;

цикл доступа к 16-разрядной памяти на внешней плате может быть выполнен без вставки тактов ожидания;

объем непосредственно адресуемой памяти на внешних платах может достигать 16 Мб;

внешняя плата может становиться хозяином (задатчиком) на шине и самостоятельно осуществлять доступ ко всем ресурсам как на шине, так и на материнской плате.

При описании шины целесообразно представить компьютер как состоящий из материнской платы (motherboard) и внешних плат, которые взаимодействуют между собой и ресурсами материнской платы через шину. Все пассивные устройства (не могущие стать задачиками) на шине можно разделить на две группы — память и устройства ввода/вывода (порты). Циклы доступа для каждой из групп отличаются друг от друга как по временным характеристикам, так и по вырабатываемым на шине сигналам.

Чисто условно, для удобства понимания функционирования шины ISA , будем считать, что на материнской плате компьютера существуют следующие устройства, способные быть владельцами (задатчиками) шины: центральный процессор (ЦП), контроллер прямого доступа в память (ПДП), контроллер регенерации памяти (КРП). Кроме этого, задатчиком на шине может быть и внешняя плата. При выполнении цикла доступа на шине задатчиком может быть только одно из устройств. Рассмотрим подробнее функции этих устройств на шине ISA .

Центральный процессор (ЦП) — является основным задатчиком на шине. По умолчанию именно ЦП будет считаться задатчиком на шине. Контроллер ПДП, а также контроллер регенерации памяти запрещают работу ЦП на время своей работы.

Контроллер ПДП — это устройство связано с сигналами запроса на режим ПДП и сигналами подтверждения режима ПДП. Активный сигнал запроса на ПДП будет разрешать последующий захват шины контроллером ПДП для передачи данных из памяти в порты вывода или из портов ввода в память.

Контроллер регенерации памяти — становится владельцем шины и генерирует сигналы адреса и чтения памяти для регенерации информации в микросхемах динамической памяти как на материнской памяти, так и внешних платах.

Внешняя плата — взаимодействует с остальными устройствами через разъем на шине ISA. Может становиться задатчиком на шине для доступа к памяти или устройствам ввода/вывода.

Кроме этого, на материнской плате компьютера имеется ряд устройств, которые не могут быть задатчиками на шине, но тем не менее взаимодействуют с ней. Это следующие устройства:

Часы реального времени (Таймер-счетчик) — это устройство состоит из часов реального времени для поддержки даты и времени и таймера, как правило на базе микросхемы Intel 8254A. Один из таймеров-счетчиков этой микросхемы вырабатывает импульсы с периодом 15 микросекунд для запуска контроллера регенерации памяти на регенерацию.

Кросс материнской платы — часть материнской платы, которая соединяет разъемы шины ISA для подключения внешних плат с другими ресурсами на материнской плате.

Память на материнской плате — часть или все микросхемы памяти прямого доступа (ОЗУ), используемые для хранения информации ЦП. На внешних платах также могут быть размещены микросхемы дополнительной памяти.

Контроллер прерываний — это устройство связано с линиями запросов прерываний на шине. Прерывания требуют дальнейшего обслуживания ЦП.

Устройства ввода/вывода — часть или все устройства ввода/вывода (такие как параллельные или последовательные порты) могут размещаться как на материнской плате, так и на внешних платах.

Перестановщик байтов данных — это устройство позволяет обмениваться данными между собой 16-разрядными и 8-разрядными устройствами.

Архитектура персонального компьютера IBM PC/AT с точки зрения использования шины ISA показана на рисунке.

Внешние платы, устанавливаемые в разъемы шины, могут быть 8- и/или 16-разрядными. 8-разрядная плата имеет только один интерфейсный разъем и может оперировать только с 8-разрядными данными. 8-разрядный слот также не может быть задатчиком на шине. 16-разрядная плата обязательно имеет два интерфейсных разъема — один основной, такой же как в 8-разрядных платах, и один дополнительный. Такая плата может оперировать как с 8-, так и с 16-разрядными данными и, кроме этого, она может быть задатчиком на шине. Общее число устанавливаемых в разъемы шины плат ограничивается как нагрузочной способностью шины, так и конструктивным исполнением материнской платы. Как правило, допускается устанавливать не более 8 (пять 16-разрядных и три 8-разрядных) внешних плат на шину. Такое ограничение вызвано также и относительно небольшим количеством свободных линий запросов на ПДП и запросов на прерывания, имеющихся на шине.

Центральный процессор по умолчанию является основным владельцем шины, контроллер ПДП и контроллер регенерации памяти могут стать задатчиками на шине, только предварительно запретив работу ЦП. Процесс запрещения работы ЦП состоит в выработке сигнала запроса на ПДП и приема сигнала подтверждения ПДП.

Центральный процессор может быть источником как 16-разрядных операций, так и 32-разрядных. Когда ЦП является 16-разрядным ресурсом, он может выполнять операции как с 16-, так и с 8-разрядными ресурсами на шине. При выполнении ЦП команды, оперирующей с 16-разрядными данными, если ресурс доступа 8- разрядный, то специальными аппаратными средствами на материнской плате в этом случае выполняются два цикла доступа. Если же ЦП является 32-разрядным, то аппаратно на материнской плате компьютера один 32-разрядный цикл работы ЦП с внешним ресурсом должен быть преобразован в два индивидуальных 16-разрядных цикла доступа.

Особенности для внешних плат. Если ЦП является задатчиком на шине, то внешние платы могут функционировать только в режиме памяти или устройства ввода/вывода.

Читайте также: Наконечник для подкачки грузовых шин двойной

Сигналы для поддержки ПДП заводятся с разъема непосредственно на контроллер ПДП, выполненный, как правило, на микросхеме Intel 8237A. Когда режим ПДП запрашивается каким-либо устройством (хотя бы один из сигналов DRQ становится активным), контроллер ПДП осуществляет захват шины у ЦП. Выдача затем соответствующего сигнала -DACK означает, что контроллер ПДП начал передачу данных. Циклы ПДП не будут выполняться на шине, если сигнал -MASTER будет разрешен с какой-либо внешней платы.

Если запрос на ПДП требуется устройству ввода/вывода, то следует учесть, что каналы 0. 3 ПДП поддерживают передачу только 8-разрядных данных; все данные должны передаваться только по линиям SD . Перестановка байтов в этом случае выполняется аппаратно на материнской плате в соответствии с сигналами SA0 и -SBHE . Такая перестановка может потребоваться, например, при передаче данных из старшего байта 16-разрядной памяти в 8-разрядный порт. Каналы ПДП 5. 7 поддерживают передачу только 16-разрядных данных; все данные должны передаваться как 16-разрядные по линиям SD . Память, участвующая в работе в режиме ПДП по этим каналам, должна быть только 16-разрядной. Перестановщик байтов на материнской плате не будет корректировать несоответствие размеров данных.

ПРИМЕЧАНИЕ: 8-разрядная память со своей стороны может передавать данные в режиме ПДП только 8-разрядным устройствам ввода/вывода; использование 8-разрядной памяти с 16-разрядными устройствами ввода/вывода не допускается.

ВНИМАНИЕ! Контроллер регенерации памяти не может захватить шину до тех пор, пока контроллер ПДП ей владеет. Это означает, что любой цикл ПДП не должен превышать 15 мкс. В противном случае может произойти потеря информации в микросхемах динамической памяти.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Сигналы запроса и подтверждения режима ПДП заведены на все внешние платы и эти сигналы вырабатываются обычными ТТЛ выходами, поэтому все внешние платы должны использовать и анализировать различные каналы ПДП. В противном случае возможен конфликт внешних слотов между собой или с устройствами на материнской плате.

Внешние слоты могут быть или памятью прямого доступа или устройством ввода/вывода, когда они взаимодействуют с контроллером ПДП.

Внешние платы могут функционировать в 5 различных режимах: задатчика шины, памяти и устройств ввода/вывода прямого доступа, памяти и устройств ввода/вывода, регенерации памяти или сброса. Платы могут поддерживать любую комбинацию из первых четырех режимов; сигналу сброса должны подчиниться все платы одновременно.

Только 16-разрядные платы с двумя интерфейсными разъемами могут становиться задатчиками на шине . Для захвата шины внешняя плата должна разрешить сигнал -DRQ и, получив сигнал -DACK от контроллера ПДП, разрешить сигнал -MASTER . На этом процедура захвата шины заканчивается.

Внешняя плата, захватив шину, может выполнять любые циклы доступа, так же как центральный процессор. Единственное ограничение — невозможность выполнять циклы ПДП, так как все интерфейсные сигналы, управляющие работой контроллера ПДП, заведены на материнскую плату и не могут быть использованы контроллером ПДП, находящимся на внешней плате. Когда внешняя плата является задатчиком на шине, контроллер ПДП запрещает сигнал AEN и это позволяет устройствам ввода/вывода нормально дешифрировать адрес и быть доступными для внешней платы. При запрещенном сигнале AEN циклы передачи ПДП невозможны (подробнее в разделе описания сигнала AEN , в гл. 3). Кроме этого, циклы ПДП не могут быть выполнены на шине также и потому, что у контроллера ПДП канал, через который был осуществлен захват шины, занят, а другие каналы контроллера ПДП не могут быть использованы до освобождения ранее занятого, т.е. до освобождения шины захватившей ее внешней платой.

ПРИМЕЧАНИЕ: Программное обеспечение, поддерживающее работу внешней платы в качестве задатчика шины, должно обеспечивать использование каналов ПДП только в режиме каскадирования. В противном случае внешняя плата не сможет осуществить захват шины.

ПРИМЕЧАНИЕ: Внешняя плата начинает любой цикл доступа как 16-разрядная, однако если сигнал -MEM CS16 или -I/O CS16 не будет разрешен, цикл будет завершен как 8-разрядный. При этом перестановщик байтов на материнской плате будет определять, по каким линиям данных ( SD или SD ) передается байт информации, исходя из анализа сигналов -SBHE и SA0 .

ВНИМАНИЕ! Захватившая шину внешняя плата обязана не реже, чем через 15 мкс, вырабатывать сигнал -REFRESH для запроса контроллеру регенерации на регенерацию памяти. Контроллер регенерации при выполнении цикла регенерации памяти вырабатывает сигналы адреса, команд и анализирует сигнал I/O CH RDY , но внешняя плата, выработавшая сигнал -REFRESH , по завершении цикла регенерации снимает этот сигнал и продолжает оставаться задатчиком на шине. При необходимости выполнить несколько циклов регенерации сигнал -REFRESH может быть удержан внешней платой на все время требуемого количества циклов регенерации.

Контроллер регенерации памяти не может захватить шину сам до тех пор, пока контроллер ПДП (а именно через него внешняя плата становится задатчиком на шине) не освободит ее на время регенерации по сигналу -REFRESH.

Внешняя плата может работать в режиме ПДП только в том случае, если контроллер ПДП является задатчиком на шине. В режиме прямого доступа к памяти данные всегда передаются между устройством ввода/вывода и памятью на внешней плате. В режиме прямого доступа к устройству ввода/вывода данные передаются между памятью и устройством ввода/вывода на внешней плате. Внешняя плата, отвечающая на шине как 8- или 16-разрядное устройство, должна соответственно использовать 8- или 16- разрядные каналы контроллера ПДП. В табл. 2.2 показано состояние сигналов на шине для режима ПДП.

ВНИМАНИЕ! Следует специально обратить внимание на некоторые особенности при выполнении циклов передачи данных между 8-разрядными устройствами ввода/вывода и 16-разрядной памятью на внешней плате. Во-первых, внешняя плата должна анализировать сигналы -SBHE и SA0 для правильного определения передаваемых данных.

Во-вторых, при записи в УВВ из памяти на внешней плате перестановщик байтов на материнской плате будет определять, по какой половине шины данных ( SD или SD ) следует направить байт; внешняя плата после анализа -SBHE и SA0 должна определить, по какой половине шины данных ей направить байт данных. В-третьих, при чтении УВВ в память на внешней плате перестановшик байтов направляет в память байт данных также либо по старшей половине шины данных SD , либо по младшей половине SD . Внешняя плата по сигналам -SBHE и SA0 должна определять, когда следует переводить в третье состояние свои выходы по младшей половине шины данных SD во избежание столкновений на шине.

Внешняя плата может как 16-разрядная память обмениваться в режиме ПДП как с 8-ми разрядными устройствами ввода/вывода, так и с 16-разрядными. Но, если внешняя плата является 8-разрядной памятью, то в режиме ПДП она может обмениваться данными только с 8-разрядными устройствами ввода/вывода. Другая особенность относится к тому случаю, когда контроллер ПДП выполняет запись данных в 8- разрядное устройство вывода на внешней плате из 16-разрядной памяти. Если такая внешняя плата установлена в 16-разрядный слот и может работать в 16-разрядном режиме, она должна для такого случая поддерживать старшую половину шины данных SD в третьем состоянии во избежание столкновения сигналов на шине.

ВНИМАНИЕ! Когда контроллер ПДП является задатчиком на шине, он игнорирует сигнал -0WS, поэтому если внешняя плата используется как 16-разрядная память и обмен с ней выполняется контроллером ПДП, применение быстрых микросхем памяти в такой плате лишено смысла.

Обычный доступ к внешней плате как к памяти или устройству ввода/вывода . Внешняя плата становится обычным ресурсом памяти или ввода/вывода, если задатчиком на шине является центральный процессор или другая внешняя плата.

ВНИМАНИЕ! Существуют особенности такого использования внешней платы, если она устанавливается в [8/16] слот, а участвует в обмене данными как 8-разрядная память или УВВ в течении всего цикла доступа. При чтении данных в такую внешнюю плату перестановщик байтов будет переставлять данные между шинами SD или SD для правильного приема данных внешней платой. Внешняя плата при этом должна поддерживать свои выходы SD в третьем состоянии, так как иначе неизбежно столкновение сигналов на шине данных.

Читайте также: Шина периферийных устройств что это

ВНИМАНИЕ! Когда некоторые внешние платы становятся задатчиками на шине, они могут игнорировать сигнал I/O CH RDY или -0WS и выполнять цикл доступа как цикл обращения к 8- или 16-разрядной памяти. Но любые внешние платы обязаны возвращать задатчику на шине ISA эти сигналы при необходимости, так как если центральный процессор является задатчиком на шине, то он использует эти сигналы для определения продолжительности цикла доступа.

Все внешние платы оказываются в режиме сброса при разрешенном сигнале RESET DRV ; иначе этот режим невозможен. Все выходы с тремя состояниями на плате должны быть в третьем состоянии и все выходы с открытым коллектором должны быть в состоянии логической единицы на время не менее 500 нс после разрешения сигнала RESET DRV . Все внешние платы должны завершить свою инициализацию за время не более 1 мс после разрешения сигнала RESET DRV и быть готовыми к выполнению циклов доступа на шине. Любые операции на шине возможны только после запрещения сигнала RESET DRV .

Контроллер регенерации памяти выполняет циклы чтения памяти по специальным адресам на материнской плате и внешних платах для регенерации информации в микросхемах динамической памяти. Каждые 15 мкс контроллер пытается овладеть шиной для запуска цикла регенерации. Если в этот момент задатчиком на шине является центральный процессор, то он освобождает шину для контроллера регенерации. Если в этот момент шина захвачена внешней платой, то контроллер регенерации выполнит цикл регенерации только при выработке внешней платой сигнала -REFRESH . Если в этот момент задатчиком на шине являлся контроллер ПДП, то до освобождения им шины цикл регенерации не может быть выполнен.

Когда выполняется цикл регенерации, контроллер регенерации вырабатывает сигналы адреса SA с одним из 256 возможных адресов регенерации. Другие адресные линии неопределены и могут находиться в третьем состоянии. Этот цикл может выполняться с задержкой по сигналу I/O CH RDY с разрешенными сигналами -SMEMR и -MEMR .

ВНИМАНИЕ! Циклы регенерации должны выполняться каждые 15 мкс для перебора всех 256 адресов за 4 мс. Если это условие не выполняется, данные, хранящиеся в динамической памяти, могут быть утеряны.

В данной главе рассматриваются характеристики шины, не зависящие от типа устройства, захватившего шину.

Максимальное адресное пространство при обращении к памяти, поддерживаемое шиной ISA , 16 Мб (24 линии адреса), но не все слоты поддерживают полностью это адресное пространство. Когда задатчик на шине осуществляет доступ к памяти на материнской плате или к памяти, установленной в слот, он должен разрешать сигналы -MEMR или -MEMW ; аппаратно на материнской плате дополнительно разрешаются сигналы -SMEMR и -SMEMW , если требуемый адрес находится в пределах первого мегабайта адресного пространства. К 8-разрядным слотам подведены только линии -SMEMR и -SMEMR , SD и SA ; поэтому внешние платы, установленные в 8-разрядные слоты, могут быть либо только 8-разрядными устройствами ввода/вывода, либо 8-ми разрядной памятью в первом мегабайте адресного пространства. Внешние платы, устанавливаемые в 8/16-разрядные слоты, принимают все командные сигналы, адреса и данные; они могут быть как 8-, так и 16-разрядными и адресное пространство памяти на них может быть любым в пределах 16 Мб. Цикл доступа к таким внешним платам завершается как 16-разрядный, если плата разрешает сигнал -I/O CS16 или -MEM CS16 .

ПРИМЕЧАНИЕ: Память на материнской плате или внешней плате считается 16- разрядным ресурсом только в том случае, если разрешается сигнал -MEM CS16 . Этот сигнал вырабатывается из сигналов адреса LA ; поэтому 16-разрядная память может быть выбрана только блоками по 128 Кб; внутри такого блока память не может быть частично 8-разрядной, а частично 16-разрядной, так как невозможно по обращению к меньшему блоку однозначно выработать сигнал -MEM CS16 . Разрядность внутри такого блока должна быть одинаковой при обращении по любому адресу внутри 128 Кб.

ВНИМАНИЕ! Микросхемы динамической памяти требуют циклов регенерации через каждые 15 мкс. Если циклы регенерации выполняются реже, чем через 15 мкс, то данные в памяти могут быть потеряны.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Динамическая память на материнской плате может иметь два вида своей организации — 16- или 32-разрядная. Но разрядность памяти на материнской плате принимается во внимание только центральным процессором, для внешних плат динамическая память на материнской плате всегда только 16-разрядная. ПЗУ на материнской плате, содержащее BIOS (Base Input/Output System — Базовая Система Ввода/Вывода), также всегда 16-разрядное.

Максимально адресное пространство для устройств ввода/вывода, поддерживаемое шиной ISA составляет 64 Кб (16 адресных линий). Все слоты поддерживают 16 адресных линий. Первые 256 адресов зарезервированы для устройств, расположенных, как правило, на материнской плате — регистры контроллера ПДП, контроллера прерываний, часов реального времени, таймера-счетчика и других устройств, требующихся для AT совместимости различных компьютеров.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Несмотря на то, что для выбора адреса УВВ доступны все 16 сигналов адреса, традиционно для адресов УВВ в компьютерах серии IBM PC/XT/AT использовались только первые 10 разрядов адреса. Это означает, что адреса из следующих килобайтных блоков будут декодироваться также как адреса в первом килобайте адресов УВВ. Поэтому для вновь разрабатываемых внешних плат следует использовать «окна» в существующем сейчас распределении адресов стандартных УВВ для компьютеров IBM PC/AT. Для увеличения количества используемых адресов УВВ (при необходимости) можно использовать адресное пространство выбранного окна со сдвигом на 1 Кб или кратное ему значение. Очевидно, что внешняя плата в этом случае должна декодировать более чем 10 линий адреса.

Линии запроса на прерывания непосредственно заведены на контроллеры прерываний типа Intel 8259A. Контроллер прерываний будет реагировать на запрос по такой линии в случае, если сигнал на ней перейдет из низкого уровня в высокий. Шина ISA не имеет линий, подтверждающих прием запроса на прерывание, поэтому запрашивающее прерывание устройство должно само определять по реакции ЦП подтверждение приема своего запроса.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Линии запроса на прерывания заведены на все слоты и обрабатываются контроллером прерывания по нарастающему фронту сигнала. До установки новой внешней платы, если она использует в своей работе контроллер прерываний, следует определить, есть ли свободная линия запроса на прерывание и именно ее использовать для новой внешней платы. При не соблюдении этого условия возможно возникновение конфликтных ситуаций на шине.

Центральный процессор или внешняя плата могут выполнить как 8- так и 16-разрядные циклы доступа, причем все циклы всегда начинаются как 16-разрядные, а завершаются как 8- или 16-разрядные. Цикл доступа будет завершен как 8-разрядный, если устройство, к которому осуществляется доступ, запретит сигнал -I/O CS16 или -MEM CS16 .

Перестановщик байтов всегда находится на материнской плате. Его задача — точно согласовать размер данных, которыми обмениваются устройства. На рис. 3.1 показано место перестановщика байтов при пересылке данных между задатчиком и ресурсом, к которому осуществляется доступ. В табл. 3.1 суммируется вся информация по перестановке байтов во время циклов доступа. Перестановка байтов осуществляется с шины SD (HIGH BYTE — старший байт) на SD (LOW BYTE — младший байт) или наоборот. В таблице перенос байта с шины SD на SD обозначается как H > L, наоборот — L -SBHE

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле