Компьютерная Энциклопедия

Компьютерная ЭнциклопедияАрхитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

Системные платы

Шина процессора

Общие сведения о шине процессора

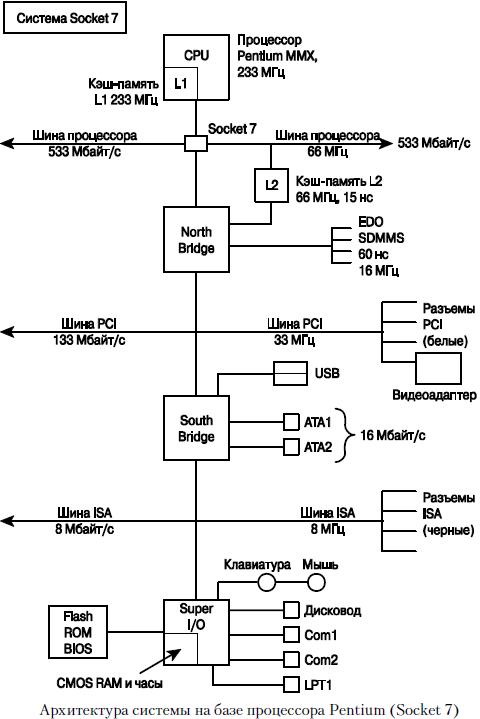

Шина процессора — соединяет процессор с северным мостом или контроллером памяти MCH. Она работает на частотах 66–200 МГц и используется для передачи данных между процессором и основной системной шиной или между процессором и внешней кэш-памятью в системах на базе процессоров пятого поколения. Схема взаимодействия шин в типичном компьютере на базе процессора Pentium (Socket 7) показано на рисунке.

На этом рисунке четко видна трехуровневая архитектура, в которой на самом верхнем уровне иерархии находится шина процессора, далее следует шина PCI и за ней шина ISA. Большинство компонентов системы подключается к одной из этих трех шин.

В системах, созданных на основе процессоров Socket 7, внешняя кэш-память второго уровня установлена на системной плате и соединена с шиной процессора, которая работает на частоте системной платы (обычно от 66 до 100 МГц). Таким образом, при появлении процессоров Socket 7 с более высокой тактовой частотой рабочая частота кэш-памяти осталась равной сравнительно низкой частоте системной платы. Например, в наиболее быстродействующих системах Intel Socket 7 частота процессора равна 233 МГц, а частота шины процессора при множителе 3,5х достигает только 66 МГц. Следовательно, кэш-память второго уровня также работает на частоте 66 МГц. Возьмем, например, систему Socket 7, использующую процессоры AMD K6-2 550, работающие на частоте 550 МГц: при множителе 5,5х ч астота шины процессора равна 100 МГц. Следовательно, в этих системах частота кэш-памяти второго уровня достигает только 100 МГц.

Проблема медленной кэш-памяти второго уровня была решена в процессорах класса P6, таких как Pentium Pro, Pentium II, Celeron, Pentium III, а также AMD Athlon и Duron. В этих процессорах использовались разъемы Socket 8, Slot 1, Slot 2, Slot A, Socket A или Socket 370. Кроме того, кэш-память второго уровня была перенесена с системной платы непосредственно в процессор и соединена с ним с помощью встроенной шины. Теперь эта шина стала называться шиной переднего плана (Front-Side Bus — FSB), однако я, согласно устоявшейся традиции, продолжаю называть ее шиной процессора.

Включение кэш-памяти второго уровня в процессор позволило значительно повысить ее скорость. В современных процессорах кэш-память расположена непосредственно в кристалле процессора, т.е. работает с частотой процессора. В более ранних версиях кэш-память второгоуровня находилась в отдельной микросхеме, интегрированной в корпус процессора, и работала с частотой, равной 1/2, 2/5 или 1/3 частоты процессора. Однако даже в этом случае скорость интегрированной кэш-памяти была значительно выше, чем скорость внешнего кэша, ограниченного частотой системной платы Socket 7.

В системах Slot 1 кэш-память второго уровня была встроена в процессор, но работала только на его половинной частоте. Повышение частоты шины процессора с 66 до 100 МГц привело к увеличению пропускной способности до 800 Мбайт/с. Следует отметить, что в большинство систем была включена поддержка AGP. Частота стандартного интерфейса AGP равна 66 МГц (т.е. вдвое больше скорости PCI), но большинство систем поддерживают порт AGP 2x, быстродействие которого вдвое выше стандартного AGP, что приводит к увеличению пропускной способности до 533 Мбайт/с. Кроме того, в этих системах обычно использовались модули памяти PC100 SDRAM DIMM, скорость передачи данных которых равна 800 Мбайт/с.

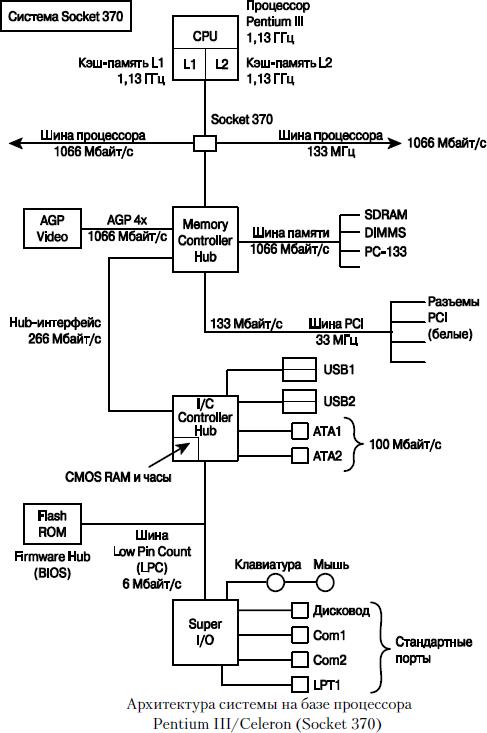

В системах Pentium III и Celeron разъем Slot 1 уступил место гнезду Socket 370. Это было связано главным образом с тем, что более современные процессоры включают в себя встроенную кэш-память второго уровня (работающую на полной частоте ядра), а значит, исчезла потребность в дорогом корпусе, содержащем несколько микросхем. Скорость шины процессора увеличилась до 133 МГц, что повлекло за собой повышение пропускной способности до 1066 Мбайт/с. В современных системах используется уже AGP 4x со скоростью передачи данных 1066 Мбайт/с.

Шина процессора на основе hub-архитектуры

Обратите внимание на hub-архитектуру Intel, используемую вместо традиционной архитектуры “северный/южный мост”. В этой конструкции основное соединение между компонентами набора микросхем перенесено в выделенный hub-интерфейс со скоростью передачи данных 266 Мбайт/с (вдвое больше, чем у шины PCI), что позволило устройствам PCI использовать полную, без учета южного моста, пропускную способность шины PCI. Кроме того, микросхема Flash ROM BIOS, называемая теперь Firmware Hub, соединяется с системой через шину LPC. Как уже отмечалось, в архитектуре “северный/южный мост” для этого использовалась микросхема Super I/O. В большинстве систем для соединения микросхемы Super I/O вместо шины ISA теперь используется шина LPC. При этом hub-архитектура позволяет отказаться от использования Super I/O. Порты, поддерживаемые микросхемой Super I/O, называются традиционными (legacy), поэтому конструкция без Super I/O получила название нетрадиционной (legacy-free) системы. В такой системе устройства, использующие стандартные порты, должны быть подсоединены к компьютеру с помощью шины USB. В этих системах обычно используются два контроллера и до четырех общих портов (дополнительные порты могут быть подключены к узлам USB).

В системах, созданных на базе процессоров AMD, применена конструкция Socket A, в которой используются более быстрые по сравнению с Socket 370 процессор и шины памяти, но все еще сохраняется конструкция “северный/южный мост”. Обратите внимание на быстродействующую шину процессора, частота которой достигает 333 МГц (пропускная способность — 2664 Мбайт/с), а также на используемые модули памяти DDR SDRAM DIMM, которые поддерживают такую же пропускную способность (т.е. 2664 Мбайт/с). Также следует заметить, что большинство южных мостов включает в себя функции, свойственные микросхемам Super I/O. Эти микросхемы получили название Super South Bridge (суперъюжный мост).

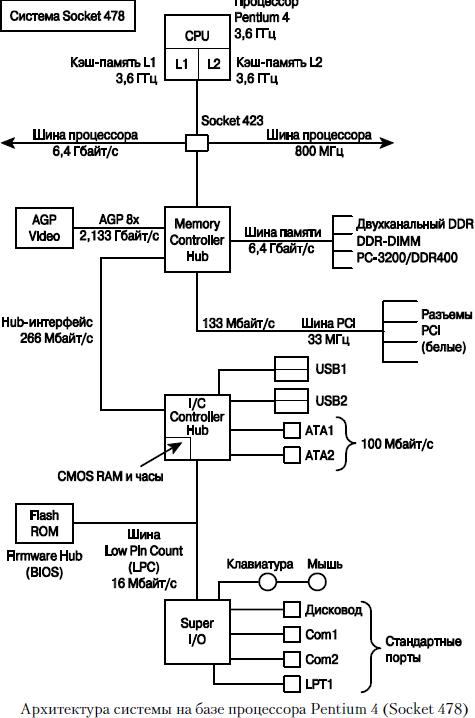

Система Pentium 4 (Socket 423 или Socket 478), созданная на основе hub-архитектуры, показана на рисунке ниже. Особенностью этой конструкции является шина процессора с тактовой частотой 400/533/800 МГц и пропускной способностью соответственно 3200/4266/6400 Мбайт/с. Сегодня это самая быстродействующая шина. Также обратите внимание на двухканальные модули PC3200 (DDR400), пропускная способность которых (3200 Мбайт/с) соответствует пропускной способности шины процессора, что позволяет максимально повысить производительность системы. В более производительных системах, включающих в себя шину с пропускной способностью 6400 Мбайт/с, используются двухканальные модули DDR400 с тактовой частотой 400 МГц, благодаря чему общая пропускная способность шины памяти достигает 6400 Мбайт/с. Процессоры с частотой шины 533 МГц могут использовать парные модули памяти (PC2100/DDR266 или PC2700/DDR333) в двухканальном режиме для достижения пропускной способности шины памяти 4266 Мбайт/с. Соответствие пропускной способности шины памяти рабочим параметрам шины процессора является условием оптимальной работы.

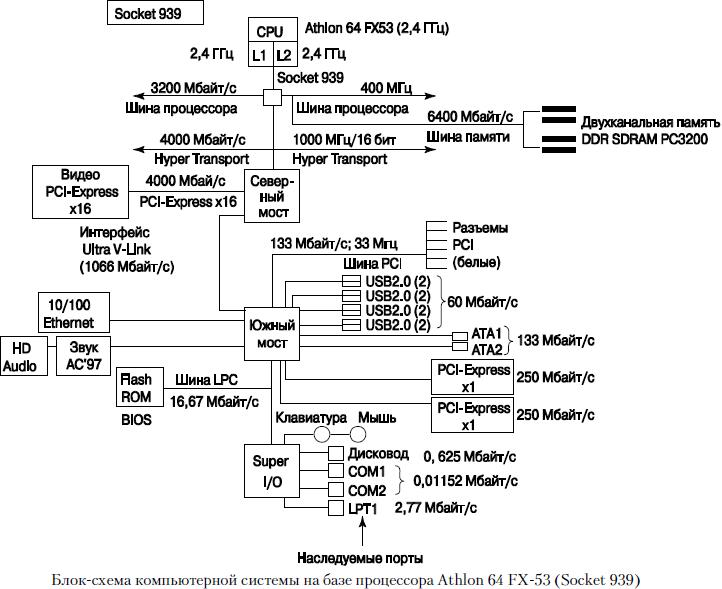

Процессор Athlon 64, независимо от типа гнезда (Socket 754, Socket 939 или Socket 940), использует высокоскоростную архитектуру HyperTransport для взаимодействия с северным мостом или микросхемой AGP Graphics Tunnel. Первые наборы микросхем для процессоров Athlon 64 использовали версию шины HyperTransport с параметрами 16 бит/800 МГц, однако последующие модели, предназначенные для поддержки процессоров Athlon 64 и Athlon 64 FX в исполнении Socket 939, используют более быструю версию шины HyperTransport с параметрами 16 бит/1 ГГц.

Наиболее заметным отличием архитектуры Athlon 64 от всех остальных архитектур ПК является размещение контроллера памяти не в микросхеме северного моста (или микросхеме MCH/GMCH), а в самом процессоре. Процессоры Athlon 64/FX/Opteron оснащены встроенным контроллером памяти. Благодаря этому исключаются многие “узкие места”, связанные с внешним контроллером памяти, что положительно сказывается на общем быстродействии системы. Главный недостаток этого подхода состоит в том, что для добавления поддержки новых технологий, например памяти DDR2, придется изменять архитектуру процессора.

Поскольку шина процессора должна обмениваться информацией с процессором с максимально возможной скоростью, в компьютере она функционирует намного быстрее любой другой шины. Сигнальные линии (линии электрической связи), представляющие шину, предназначены для передачи данных, адресов и сигналов управления между отдельными компонентами компьютера. Большинство процессоров Pentium имеют 64-разрядную шину данных, поэтому за один цикл по шине процессора передается 64 бит данных (8 байт).

Тактовая частота , используемая для передачи данных по шине процессора, соответствует его внешней частоте. Это следует учитывать, поскольку в большинстве процессоров внутренняя тактовая частота, определяющая скорость работы внутренних блоков, может превышать внешнюю. Например, процессор AMD Athlon 64 3800+ работает с внутренней тактовой частотой 2,4 ГГц, однако внешняя частота составляет всего 400 МГц, в то время как процессор Pentium 4 с внутренней частотой 3,4 ГГц имеет внешнюю частоту, равную 800 МГц. В новых системах реальная частота процессора зависит от множителя шины процессора (2x, 2,5x, 3x и выше). Шина FSB, подключенная к процессору, по каждой линии данных может передавать один бит данных в течение одного или двух периодов тактовой частоты. Таким образом, в компьютерах с современными процессорами за один такт передается 64 бит.

Читайте также: Цветы в шинах во дворе

Пропускная способность шины процессора

Для определения скорости передачи данных по шине процессора необходимо умножить разрядность шины данных (64 бит, или 8 байт, для Celeron/Pentium III/4 или Athlon/Duron/ Athlon XP/Athlon 64) на тактовую частоту шины (она равна базовой (внешней) тактовой частоте процессора).

Например, при использовании процессора Pentium 4 с тактовой частотой 3,6 ГГц, установленного на системной плате, частота которой равна 800 МГц, максимальная мгновенная скорость передачи данных будет достигать примерно 6400 Мбайт/с. Этот результат можно получить, используя следующую формулу:

800 МГц × 8 байт (64 бит) = 6400 Мбайт/с.

Для более медленной системы Pentium 4:

533,33 МГц × 8 байт (64 бит) = 4266 Мбайт/с;

400 МГц × 8 байт (64 бит) = 3200 Мбайт/с.

Для системы Athlon XP (Socket A) получится следующее:

400 МГц × 8 байт (64 бит) = 3200 Мбайт/с;

333 МГц × 8 байт (64 бит) = 2667 Мбайт/с;

266,66 МГц × 8 байт (64 бит) = 2133 Мбайт/с.

Для системы Pentium III (Socket 370):

133,33 МГц × 8 байт (64 бит) = 1066 Мбайт/с;

100 МГц × 8 байт (64 бит) = 800 Мбайт/с.

Максимальную скорость передачи данных называют также пропускной способностью шины (bandwidth) процессора.

Шина объединяющая процессор память называется

В вычислительной системе, состоящей из множества подсистем, необходим механизм для их взаимодействия. Эти подсистемы должны быстро и эффективно обмениваться данными. Например, процессор, с одной стороны, должен быть связан с памятью, с другой стороны, необходима связь процессора с устройствами ввода/вывода. Одним из простейших механизмов, позволяющих организовать взаимодействие различных подсистем, является единственная центральная шина, к которой подсоединяются все подсистемы. Доступ к такой шине разделяется между всеми подсистемами. Подобная организация имеет два основных преимущества: низкая стоимость и универсальность. Поскольку такая шина является единственным местом подсоединения для разных устройств, новые устройства могут быть легко добавлены, и одни и те же периферийные устройства можно даже применять в разных вычислительных системах, использующих однотипную шину. Стоимость такой организации получается достаточно низкой, поскольку для реализации множества путей передачи информации используется единственный набор линий шины, разделяемый множеством устройств.

Главным недостатком организации с единственной шиной является то, что шина создает узкое горло, ограничивая, возможно, максимальную пропускную способность ввода/вывода. Если весь поток ввода/вывода должен проходить через центральную шину, такое ограничение пропускной способности весьма реально. В коммерческих системах, где ввод/вывод осуществляется очень часто, а также в суперкомпьютерах, где необходимые скорости ввода/вывода очень высоки из-за высокой производительности процессора, одним из главных вопросов разработки является создание системы нескольких шин, способной удовлетворить все запросы.

Одна из причин больших трудностей, возникающих при разработке шин, заключается в том, что максимальная скорость шины главным образом лимитируется физическими факторами: длиной шины и количеством подсоединяемых устройств (и, следовательно, нагрузкой на шину). Эти физические ограничения не позволяют произвольно ускорять шины. Требования быстродействия (малой задержки) системы ввода/ввывода и высокой пропускной способности являются противоречивыми. В современных крупных системах используется целый комплекс взаимосвязанных шин, каждая из которых обеспечивает упрощение взаимодействия различных подсистем, высокую пропускную способность, избыточность (для увеличения отказоустойчивости) и эффективность.

Традиционно шины делятся на шины, обеспечивающие организацию связи процессора с памятью, и шины ввода/вывода. Шины ввода/вывода могут иметь большую протяженность, поддерживать подсоединение многих типов устройств, и обычно следуют одному из шинных стандартов. Шины процессор-память, с другой стороны, сравнительно короткие, обычно высокоскоростные и соответствуют организации системы памяти для обеспечения максимальной пропускной способности канала память-процессор. На этапе разработки системы, для шины процессор-память заранее известны все типы и параметры устройств, которые должны соединяться между собой, в то время как разработчик шины ввода/вывода должен иметь дело с устройствами, различающимися по задержке и пропускной способности.

Как уже было отмечено, с целью снижения стоимости некоторые компьютеры имеют единственную шину для памяти и устройств ввода/вывода. Такая шина часто называется системной. Персональные компьютеры, как правило, строятся на основе одной системной шины в стандартах ISA, EISA или MCA. Необходимость сохранения баланса производительности по мере роста быстродействия микропроцессоров привела к двухуровневой организации шин в персональных компьютерах на основе локальной шины. Локальной шиной называется шина, электрически выходящая непосредственно на контакты микропроцессора. Она обычно объединяет процессор, память, схемы буферизации для системной шины и ее контроллер, а также некоторые вспомогательные схемы. Типичными примерами локальных шин являются VL-Bus и PCI.

Рассмотрим типичную транзакцию на шине. Шинная транзакция включает в себя две части: посылку адреса и прием (или посылку) данных. Шинные транзакции обычно определяются характером взаимодействия с памятью: транзакция типа «Чтение» передает данные из памяти (либо в ЦП, либо в устройство ввода/вывода), транзакция типа «Запись» записывает данные в память. В транзакции типа «Чтение» по шине сначала посылается в память адрес вместе с соответствующими сигналами управления, индицирующими чтение. Память отвечает, возвращая на шину данные с соответствующими сигналами управления. Транзакция типа «Запись» требует, чтобы ЦП или устройство в/в послало в память адрес и данные и не ожидает возврата данных. Обычно ЦП вынужден простаивать во время интервала между посылкой адреса и получением данных при выполнении чтения, но часто он не ожидает завершения операции при записи данных в память.

Разработка шины связана с реализацией ряда дополнительных возможностей (рисунок 5.43). Решение о выборе той или иной возможности зависит от целевых параметров стоимости и производительности. Первые три возможности являются очевидными: раздельные линии адреса и данных, более широкие (имеющие большую разрядность) шины данных и режим групповых пересылок (пересылки нескольких слов) дают увеличение производительности за счет увеличения стоимости.

Следующий термин, указанный в таблице, — количество главных устройств шины (bus master). Главное устройство шины — это устройство, которое может инициировать транзакции чтения или записи. ЦП, например, всегда является главным устройством шины. Шина имеет несколько главных устройств, если имеется несколько ЦП или когда устройства ввода/вывода могут инициировать транзакции на шине. Если имеется несколько таких устройств, то требуется схема арбитража, чтобы решить, кто следующий захватит шину. Арбитраж часто основан либо на схеме с фиксированным приоритетом, либо на более «справедливой» схеме, которая случайным образом выбирает, какое главное устройство захватит шину.

В настоящее время используются два типа шин, отличающиеся способом коммутации: шины с коммутацией цепей (circuit-switched bus) и шины с коммутацией пакетов (packet-switched bus), получившие свои названия по аналогии со способами коммутации в сетях передачи данных. Шина с коммутацией пакетов при наличии нескольких главных устройств шины обеспечивает значительно большую пропускную способность по сравнению с шиной с коммутацией цепей за счет разделения транзакции на две логические части: запроса шины и ответа. Такая методика получила название «расщепления» транзакций (split transaction). (В некоторых системах такая возможность называется шиной соединения/разъединения (connect/disconnect) или конвейерной шиной (pipelined bus). Транзакция чтения разбивается на транзакцию запроса чтения, которая содержит адрес, и транзакцию ответа памяти, которая содержит данные. Каждая транзакция теперь должна быть помечена (тегирована) соответствующим образом, чтобы ЦП и память могли сообщить что есть что.

Шина с коммутацией цепей не делает расщепления транзакций, любая транзакция на ней есть неделимая операция. Главное устройство запрашивает шину, после арбитража помещает на нее адрес и блокирует шину до окончания обслуживания запроса. Большая часть этого времени обслуживания при этом тратится не на выполнение операций на шине (например, на задержку выборки из памяти). Таким образом, в шинах с коммутацией цепей это время просто теряется. Расщепленные транзакции делают шину доступной для других главных устройств пока память читает слово по запрошенному адресу. Это, правда, также означает, что ЦП должен бороться за шину для посылки данных, а память должна бороться за шину, чтобы вернуть данные. Таким образом, шина с расщеплением транзакций имеет более высокую пропускную способность, но обычно она имеет и большую задержку, чем шина, которая захватывается на все время выполнения транзакции. Транзакция называется расщепленной, поскольку произвольное количество других пакетов или транзакций могут использовать шину между запросом и ответом.

Читайте также: Давление в шинах уаз хантер дизель

Последний вопрос связан с выбором типа синхронизации и определяет является ли шина синхронной или асинхронной. Если шина синхронная, то она включает сигналы синхронизации, которые передаются по линиям управления шины, и фиксированный протокол, определяющий расположение сигналов адреса и данных относительно сигналов синхронизации. Поскольку практически никакой дополнительной логики не требуется для того, чтобы решить, что делать в следующий момент времени, эти шины могут быть и быстрыми, и дешевыми. Однако они имеют два главных недостатка. Все на шине должно происходить с одной и той же частотой синхронизации, поэтому из-за проблемы перекоса синхросигналов, синхронные шины не могут быть длинными. Обычно шины процессор-память синхронные.

| Возможность | Высокая производительность | Низкая стоимость | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Общая разрядность шины | Отдельные линии адреса и данных | Мультиплексирование линий адреса и данных | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Ширина (рязрядность) данных | Чем шире, тем быстрее (например, 32 бит) | Чем уже, тем дешевле (например, 8 бит) | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Размер пересылки | Пересылка нескольких слов имеет меньшие накладные расходы | Пересылка одного слова дешевле | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Главные устройства шины | Несколько (требуется арбитраж) | Одно (арбитраж не нужен) | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Расщепленные транзакции? | Да — отдельные пакеты Запроса и Ответа дают большую полосу пропускания (нужно несколько главных устройств) | Нет — продолжающееся соединение дешевле и имеет меньшую задержку | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Тип синхронизации | Синхронные | Асинхронные | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Рис. 5.43. Основные возможности шин

Асинхронная шина, с другой стороны, не тактируется. Вместо этого обычно используется старт-стопный режим передачи и протокол «рукопожатия» (handshaking) между источником и приемником данных на шине. Эта схема позволяет гораздо проще приспособить широкое разнообразие устройств и удлинить шину без беспокойства о перекосе сигналов синхронизации и о системе синхронизации. Если может использоваться синхронная шина, то она обычно быстрее, чем асинхронная, из-за отсутствия накладных расходов на синхронизацию шины для каждой транзакции. Выбор типа шины (синхронной или асинхронной) определяет не только пропускную способность, но также непосредственно влияет на емкость системы ввода/вывода в терминах физического расстояния и количества устройств, которые могут быть подсоединены к шине. Асинхронные шины по мере изменения технологии лучше масштабируются. Шины ввода/вывода обычно асинхронные.

Обычно количество и типы устройств ввода/вывода в вычислительных системах не фиксируются, что позволяет пользователю самому подобрать необходимую конфигурацию. Шина ввода/вывода компьютера может рассматриваться как шина расширения, обеспечивающая постепенное наращивание устройств ввода/вывода. Поэтому стандарты играют огромную роль, позволяя разработчикам компьютеров и устройств ввода/вывода работать независимо. Появление стандартов определяется разными обстоятельствами.

Иногда широкое распространение и популярность конкретных машин становятся причиной того, что их шина ввода/вывода становится стандартом де факто. Примерами таких шин могут служить PDP-11 Unibus и IBM PC-AT Bus. Иногда стандарты появляются также в результате определенных достижений по стандартизации в некотором секторе рынка устройств ввода/вывода. Интеллектуальный периферийный интерфейс (IPI — Intelligent Peripheral Interface) и Ethernet являются примерами стандартов, появившихся в результате кооперации производителей. Успех того или иного стандарта в значительной степени определяется его принятием такими организациями как ANSI (Национальный институт по стандартизации США) или IEEE (Институт инженеров по электротехнике и радиоэлектронике). Иногда стандарт шины может быть прямо разработан одним из комитетов по стандартизации: примером такого стандарта шины является FutureBus.

На рисунке 5.44 представлены характеристики нескольких стандартных шин. Заметим, что строки этой таблицы, касающиеся пропускной способности, не указаны в виде одной цифры для шин процессор-память (VME, FutureBus, MultibusII). Размер пересылки, из-за разных накладных расходов шины, сильно влияет на пропускную способность. Поскольку подобные шины обычно обеспечивают связь с памятью, то пропускная способность шины зависит также от быстродействия памяти. Например, в идеальном случае при бесконечном размере пересылки и бесконечно быстрой памяти (время доступа 0 нсек) шина FutureBus на 240% быстрее шины VME, но при пересылке одиночных слов из 150-нсекундной памяти шина FutureBus только примерно на 20% быстрее, чем шина VME.

| VME bus | FutureBus | Multibus II | IPI | SCSI | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Ширина шины (кол-во сигналов) | 128 | 96 | 96 | 16 | 8 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Мультиплексирование адреса/данных | Нет | Да | Да | ( | ( | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Разрядность данных | 16/32 бит | 32 бит | 32 бит | 16 бит | 8 бит | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Размер пересылки (слов) | Одиночная или групповая | Одиночная или групповая | Одиночная или групповая | Одиночная или групповая | Одиночная или групповая | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Количество глав- ных устройств шины | Несколько | Несколько | Несколько | Одно | Несколько | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Расщепление транзакций | Нет | Доп. возможность | Доп. возможность | Доп. возможность | Доп. возможность | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Полоса пропускания (время доступа — 0 нс — 1 слово) | 25.9 Мб/c | 37.0 Мб/c | 20.0 Мб/c | 25.0 Мб/c | 5.0 Мб/c | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Полоса пропускания (время доступа — 150 нс — 1 слово) | 12.9 Мб/c | 15.5 Мб/c | 10.0 Мб/c | 25.0 Мб/c | 5.0 Мб/c | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Полоса пропускания (время доступа — 0 нс — неогр. размер блока) | 27.9 Мб/c | 95.2 Мб/c | 40.0 Мб/c | 25.0 Мб/c | 5.0 Мб/c | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Полоса пропускания (время доступа — 150 нс — неогр. размер блока) | 13.6 Мб/c | 20.8 Мб/c | 13.3 Мб/c | 25.0 Мб/c | 5.0 Мб/c | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Максимальное количество устройств | 21 | 20 | 21 | 8 | 7 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Максимальная длина шины | 0.5 м | 0.5 м | 0.5 м | 50 м | 25 м | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Стандарт | IEEE 1014 | IEEE 896.1 | ANSI/ IEEE 1296 | ANSI X3.129 | ANSI X3.131 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Рис. 5.44. Примеры стандартных шин

Одной из популярных шин персональных компьютеров была системная шина IBM PC/XT, обеспечивавшая передачу 8 бит данных. Кроме того, эта шина включала 20 адресных линий, которые ограничивали адресное пространство пределом в 1 Мбайт. Для работы с внешними устройствами в этой шине были предусмотрены также 4 линии аппаратных прерываний (IRQ) и 4 линии для требования внешними устройствами прямого доступа к памяти (DMA). Для подключения плат расширения использовались специальные 62-контактные разъемы. При этом системная шина и микропроцессор синхронизировались от одного тактового генератора с частотой 4.77 МГц. Таким образом теоретическая скорость передачи данных могла достигать немногим более 4 Мбайт/с.

Системная шина ISA (Industry Standard Architecture) впервые стала применяться в персональных компьютерах IBM PC/AT на базе процессора i286. Эта системная шина отличалась наличием второго, 36-контактного дополнительного разъема для соответствующих плат расширения. За счет этого количество адресных линий было увеличено на 4, а данных — на 8, что позволило передавать параллельно 16 бит данных и обращаться к 16 Мбайт системной памяти. Количество линий аппаратных прерываний в этой шине было увеличено до 15, а каналов прямого доступа — до 7. Системная шина ISA полностью включала в себя возможности старой 8-разрядной шины. Шина ISA позволяет синхронизировать работу процессора и шины с разными тактовыми частотами. Она работает на частоте 8 МГц, что соответствует максимальной скорости передачи 16 Мбайт/с.

С появлением процессоров i386, i486 и Pentium шина ISA стала узким местом персональных компьютеров на их основе. Новая системная шина EISA (Extended Industry Standard Architecture), появившаяся в конце 1988 года, обеспечивает адресное пространство в 4 Гбайта, 32-битовую передачу данных (в том числе и в режиме DMA), улучшенную систему прерываний и арбитраж DMA, автоматическую конфигурацию системы и плат расширения. Устройства шины ISA могут работать на шине EISA.

Шина EISA предусматривает централизованное управление доступом к шине за счет наличия специального устройства — арбитра шины. Поэтому к ней может подключаться несколько главных устройств шины. Улучшенная система прерываний позволяет подключать к каждой физической линии запроса на прерывание несколько устройств, что снимает проблему количества линий прерывания. Шина EISA тактируется частотой около 8 МГц и имеет максимальную теоретическую скорость передачи данных 33 Мбайт/с.

Шина MCA также обеспечивает 32-разрядную передачу данных, тактируется частотой 10 МГц, имеет средства автоматического конфигурирования и арбитража запросов. В отличие от EISA она не совместима с шиной ISA и используется только в компьютерах компании IBM.

Читайте также: Шины в алматы екар

Шина VL-bus, предложенная ассоциацией VESA (Video Electronics Standard Association), предназначалась для увеличения быстродействия видеоадаптеров и контроллеров дисковых накопителей для того, чтобы они могли работать с тактовой частотой до 40 МГц. Шина VL-bus имеет 32 линии данных и позволяет подключать до трех периферийных устройств, в качестве которых наряду с видеоадаптерами и дисковыми контроллерами могут выступать и сетевые адаптеры. Максимальная скорость передачи данных по шине VL-bus может составлять около 130 Мбайт/с. После появления процессора Pentium ассоциация VESA приступила к работе над новым стандартом VL-bus версии 2, который предусматривает использование 64-битовой шины данных и увеличение количества разъемов расширения. Ожидаемая скорость передачи данных — до 400 Мбайт/с.

Шина PCI (Peripheral Component Interconnect) также, как и шина VL-bus, поддерживает 32-битовый канал передачи данных между процессором и периферийными устройствами, работает на тактовой частоте 33 МГц и имеет максимальную пропускную способность 120 Мбайт/с. При работе с процессорами i486 шина PCI дает примерно те же показатели производительности, что и шина VL-bus. Однако, в отличие от последней, шина PCI является процессорно независимой (шина VL-bus подключается непосредственно к процессору i486 и только к нему). Ee легко подключить к различным центральным процессорам. В их числе Pentium, Alpha, R4400 и PowerPC.

Шина VME приобрела большую популярность как шина ввода/вывода в рабочих станциях и серверах на базе RISC-процессоров. Эта шина высоко стандартизована, имеется несколько версий этого стандарта. В частности, VME32 — 32-битовая шина с производительностью 30 Мбайт/с, а VME64 — 64-битовая шина с производительностью 160 Мбайт/с.

В однопроцессорных и многопроцессорных рабочих станциях и серверах на основе микропроцессоров SPARC одновременно используются несколько типов шин: SBus, MBus и XDBus, причем шина SBus применяется в качестве шины ввода/вывода, а MBus и XDBus — в качестве шин для объединения большого числа процессоров и памяти.

Шина SBus (известная также как стандарт IEEE-1496) имеет 32-битовую и 64-битовую реализацию, работает на частоте 20 и 25 МГц и имеет максимальную скорость передачи данных в 32-битовом режиме равную соответственно 80 или 100 Мбайт/с. Шина предусматривает режим групповой пересылки данных с максимальным размером пересылки до 128 байт. Она может работать в двух режимах передачи данных: режиме программируемого ввода/вывода и в режиме прямого доступа к виртуальной памяти (DVMA). Последний режим особенно эффективен при передаче больших блоков данных.

Шина MBus работает на тактовой частоте 50 МГц в синхронном режиме с мультиплексированием адреса и данных. Общее число сигналов шины равно 100, а разрядность шины данных составляет 64 бит. По шине передаются 36-битовые физические адреса. Шина обеспечивает протокол поддержания когерентного состояния кэш-памяти нескольких (до четырех) процессоров, имеет максимальную пропускную способность в 400 Мбайт/с, а типовая скорость передачи составляет 125 Мбайт/с. Отличительными свойствами шины MBus являются: возможность увеличения числа процессорных модулей, поддержка симметричной мультипроцессорной обработки, высокая пропускная способность при обмене с памятью и подсистемой ввода/вывода, открытые (непатентованные) спецификации интерфейсов.

Шина MBus была разработана для относительно небольших систем (ее длина ограничивается десятью дюймами, что позволяет объединить до четырех процессоров с кэш-памятью второго уровня и основной памятью). Для построения систем с большим числом процессоров нужна большая масштабируемость шины. Одна из подобного рода шин — XDBus, используется в серверах SPARCserver 1000 (до 8 процессоров) и SPARCcenter 2000 (до 20 процессоров) компании Sun Microsystems и SuperServer 6400 компании Cray Research (до 64 процессоров). XDBus представляет собой шину, работающую в режиме расщепления транзакций. Это позволяет ей, имея пиковую производительность в 400 Мбайт/с, поддерживать типовую скорость передачи на уровне более 310 Мбайт/с.

В современных компьютерах часто применяются и фирменные (запатентованные) шины, обеспечивающие очень высокую пропускную способность для построения многопроцессорных серверов. Одной из подобных шин является системная шина POWERpath-2, которая применяется в суперсервере Chellenge компании Silicon Graphics. Она способна поддерживать эффективную работу до 36 процессоров MIPS R4400 (9 процессорных плат с четырьмя 150 МГц процессорами на каждой плате) с общей расслоенной памятью объемом до 16 Гбайт (коэффициент расслоения памяти равен восьми). POWERpath-2 имеет разрядность данных 256 бит, разрядность адреса 40 бит, и работает на частоте 50 МГц с пониженным напряжением питания. Она поддерживает методику расщепления транзакций, причем может иметь до восьми отложенных транзакций чтения одновременно. При этом арбитраж шины адреса и шины данных выполняется независимо. POWERpath-2 поддерживает протокол когерентного состояния кэш-памяти каждого процессора в системе.

Одной из наиболее популярных шин ввода-вывода в настоящее время является шина SCSI.

Под термином SCSI — Small Computer System Interface (Интерфейс малых вычислительных систем) обычно понимается набор стандартов, разработанных Национальным институтом стандартов США (ANSI) и определяющих механизм реализации магистрали передачи данных между системной шиной компьютера и периферийными устройствами. На сегодняшний день приняты два стандарта (SCSI-1 и SCSI-2). Стандарт SCSI-3 находится в процессе доработки.

Начальный стандарт 1986 года, известный теперь под названием SCSI-1, определял рабочие спецификации протокола шины, набор команд и электрические параметры. В 1992 году этот стандарт был пересмотрен с целью устранения недостатков первоначальной спецификации (особенно в части синхронного режима передачи данных) и добавления новых возможностей повышения производительности, таких как «быстрый режим» (fast mode), «широкий режим» (wide mode) и помеченные очереди. Этот пересмотренный стандарт получил название SCSI-2 и в настоящее время используется большинством поставщиков вычислительных систем.

Первоначально SCSI предназначался для использования в небольших дешевых системах и поэтому был ориентирован на достижение хороших результатов при низкой стоимости. Характерной его чертой является простота, особенно в части обеспечения гибкости конфигурирования периферийных устройств без изменения организации основного процессора. Главной особенностью подсистемы SCSI является размещение в периферийном оборудовании интеллектуального контроллера.

Для достижения требуемого высокого уровня независимости от типов периферийных устройств в операционной системе основной машины, устройства SCSI представляются имеющими очень простую архитектуру. Например, геометрия дискового накопителя представляется в виде линейной последовательности одинаковых блоков, хотя в действительности любой диск имеет более сложную многомерную геометрию, содержащую поверхности, цилиндры, дорожки, характеристики плотности, таблицу дефектных блоков и множество других деталей. В этом случае само устройство или его контроллер несут ответственность за преобразование упрощенной SCSI модели в данные для реального устройства.

Стандарт SCSI-2 определяет в частности различные режимы: Wide SCSI, Fast SCSI и Fast-and-Wide SCSI. Стандарт SCSI-1 определяет построение периферийной шины на основе 50-жильного экранированного кабеля, описывает методы адресации и электрические характеристики сигналов. Шина данных SCSI-1 имеет разрядность 8 бит, а максимальная скорость передачи составляет 5 Мбайт/сек. Fast SCSI сохраняет 8-битовую шину данных и тем самым может использовать те же самые физические кабели, что и SCSI-1. Он отличается только тем, что допускает передачи со скоростью 10 Мбайт/сек в синхронном режиме. Wide SCSI удваивает либо учетверяет разрядность шины данных (либо 16, либо 32 бит), допуская соответственно передачи со скоростью либо 10, либо 20 Мбайт/сек. В комбинации Fast-and-Wide SCSI возможно достижение скоростей передачи 20 и 40 Мбайт/сек соответственно.

Однако поскольку в обычном 50-жильном кабеле просто не хватает жил, комитет SCSI решил расширить спецификацию вторым 66-жильным кабелем (так называемый B-кабель). B-кабель имеет дополнительные линии данных и ряд других сигнальных линий, позволяющие реализовать режим Fast-and-Wide.

В реализации режима Wide SCSI предложена также расширенная адресация, допускающая подсоединение к шине до 16 устройств (вместо стандартных восьми). Это значительно увеличивает гибкость подсистемы SCSI, правда приводит к появлению дополнительных проблем, связанных с эффективностью ее использования.

Реализация режимов Wide-SCSI и Fast-and-Wide SCSI до 1994 года редко использовалась, поскольку эффективность их применения не была достаточно высокой. Однако широкое распространение дисковых массивов и дисковых накопителей со скоростью вращения 7200 оборотов в минуту делают эту технологию весьма актуальной.

Следует отметить некоторую путаницу в терминологии. Часто стандартный 50-контактный разъем также называют разъемом SCSI-1, а более новый микроразъем — разъемом SCSI-2. Стандарт SCSI определяет только количество жил в кабеле, и вообще не определяет тип разъема.

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле