Введение

PCI (Peripheral Component Interconnect bus) — шина для подсоединения периферийных устройств. Стала массово применяться для Pentium-систем, но используется и с 486 процессорами. Частота шины от 20 до 33 МГц, теоретически максимальная скорость 132/264 Мбайт/с для 32/64 бит. В современных материнских платах частота на шине PCI задается как 1/2 входной частоты процессора, т.е при частоте 66 MHz на PCI будет 33 MHz, при 75 MHz — 37.5 MHz.

Имеет версии с питанием 5V, 3.3V и универсальную (с переключением линий +VI/O c 5V на 3,3V). Ключами являются пропущенные ряды контактов 12, 13 и 50, 51. Для слота с питанием 5V ключ расположен на месте контактов 50, 51, для 3,3 В — 12, 13, а для универсального — два ключа: 12, 13 и 50,51. 32-битный слот заканчивается контактами А62/В62, 64-битный — А94/В94.

Слот PCI самодостаточен для подключения любого контроллера (VLB не работала без ISA), на системной плате может сосуществовать с любой из других шин ввода-вывода.

Шина PCI — первая шина в архитектуре IBM PC, которая не привязана к этой архитектуре. Она является процессорно-независимой и применяется, например, в компьютерах Macintosh.

В отличие от остальных шин, компоненты расположены на левой поверхности плат PCI-адаптеров. По этой причине крайний PCI-слот обычно разделяет использование посадочного места с соседним ISA-слотом (Shared slot).

Процессор через так называемые мосты (PCI Bridge) может быть подключен к нескольким каналам PCI, обеспечивая возможность одновременной передачи данных между независимыми каналами PCI (возможно только в спецификации 2.1).

Автоконфигурирование устройств (выбор запросов прерывания, каналов DMA) поддерживается средствами BIOS материнской платы по образу и подобию стандарта Plug & Play. В настоящее время действует спецификация PCI 2.1.

Стандарт PCI определяет для каждого слота конфигурационное пространство размером до 256 восьмибитных регистров, не приписанных ни к пространству памяти, ни к пространству ввода-вывода. Доступ к ним осуществляется по специальным циклам шины Configuration Read и Configuration Write, вырабатываемым контроллером при обращении процессора к регистрам контроллера шины PCI, расположенным в его пространстве ввода-вывода.

На PCI определены два основных вида устройств — инициатор (по ГОСТ — задатчик), т.е. устройство, получившее от арбитра шины разрешение на захват ее и устройство назначения, цель (target) с которым инициатор выполняет цикл обмена данными.

Сигналы шины PCI

Знак — (минус) перед названием сигнала означает, что активный уровень этого сигнала логический ноль, обозначение означает группу сигналов с номерами от 0 до XX.

AD — мультиплексированная шина адреса/данных. Адрес передается по сигналу — FRAME, в последующих тактах передаются данные.

-C/ BE — команда/разрешение обращения к байтам. Команда, определяющая тип очередного цикла шины (чтение-запись памяти, ввода/вывода или чтение/запись конфигурации, подтверждение прерывания и другие) задается четырехбитным кодом в фазе адреса по сигналу — FRAME.

-FRAME — индикатор фазы адреса (иначе — передача данных).

-DEVSEL — выбор инициатором устройства назначения.

-IRDY — готовность инициатора к обмену данными.

-TRDY — готовность устройства назначения к обмену данными.

-STOP — запрос устройства назначения к инициатору на останов текущей транзакции.

-LOCK — используется для установки, обслуживания и освобождения захвата ресурса на PCI.

-REQ — запрос от PCI-устройства на захват шины (для слотов 3:0).

-GNT — разрешение мастеру на использование шины.

PAR — общий бит четности для линий AD и C/BE .

-ParityER — сигнал об ошибке по четности (от устройства, ее обнаружившего).

-RST — сброс всех устройств.

IDSEL — выбор устройства назначения в циклах считывания и записи конфигурации.

-SERR — системная ошибка, активизируется любым устройством PCI и вызывает немаскируемое прерывание процессора (NMI).

-REQ64 — запрос на 64-битный обмен.

-ASK64 — подтверждение 64-битного обмена.

-INTR A,B,C,D — линии запросов прерывания, направляются на доступные линии IRQ BIOS компьютера. Запрос по низкому уровню допускает разделяемое использование линий прерывания.

Clock — сигнал синхронизации на тактовой частоте шины.

Test Clock, -TSTRES, TestDO, TestDI — сигналы для тестирования адаптеров по интерфейсу JTAG (на системной плате обычно не задействованы).

TSTMSLCT — перевод в режим тестирования.

Видео:03. Основы устройства компьютера. Память и шина. [Универсальный программист]Скачать

![03. Основы устройства компьютера. Память и шина. [Универсальный программист]](https://i.ytimg.com/vi/mjiJutISb6U/0.jpg)

Компьютерная Энциклопедия

Компьютерная Энциклопедия

Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

Растворитель 4 в канистрах гост: растворитель р 4 гост НЕРС+. https://bryansk-1.on-prava.com купить права на бульдозер в Брянске.

Видео:Компьютерная шина PCI ExpressСкачать

PCI и PCI-X

Видео:Шина PCI Express: эволюция от поколения к поколениюСкачать

Сигнальный протокол шин PCI и PCI-X

Обмен информацией по шине PCI и PCI-X организован в виде транзакций — логически завершенных операций обмена. В типовой транзакции участвуют два устройства —инициатор обмена (initiator), он же ведущее устройство (master), и целевое устройство (ЦУ, target)), оно же ведомое (slave). Правила взаимодействия этих устройств определяются протоколом шины PCI. Устройство может следить за транзакциями на шине и не являясь их участником (не вводя никаких сигналов); режиму слежения соответствует термин Snooping. Есть особый тип транзакции (Special Cycle) — широковещательный, в котором инициатор протокольно не взаимодействует ни с одним из устройств. В каждой транзакции выполняется одна команда — как правило, чтение или запись данных по указанному адресу. Транзакция начинается с фазы адреса, в которой инициатор задает команду и целевой адрес. Далее могут следовать фазы данных, в которых одно устройство (источник данных) помещает данные на шину, а другое (приемник) их считывает. Транзакции, в которых присутствует множество фаз данных, называются пакетными. Есть и одиночные транзакции (с одной фазой данных). Транзакция может завершиться и без фаз данных, если целевое устройство (или инициатор) не готово к обмену. В шине PCI-X добавлена фаза атрибутов, в которой передается дополнительная информация о транзакции.

Читайте также: Шины tigar чьи они

Видео:лекция 403 CAN шина- введениеСкачать

Сигнальный протокол шин PCI и PCI-X

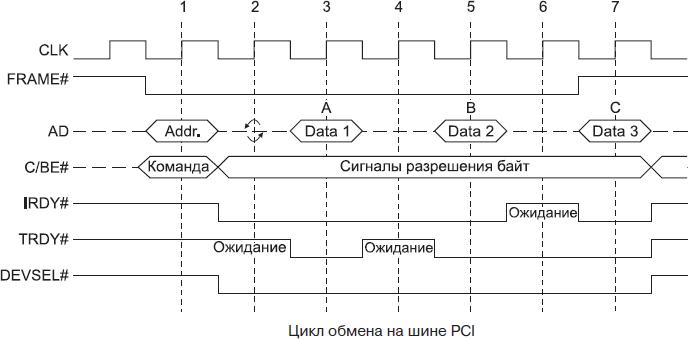

Состав и назначение интерфейсных сигналов шины раскрывает таблице ниже. Состояния всех сигнальных линий воспринимаются по положительному перепаду CLK, и именно эти моменты в дальнейшем описании подразумеваются под тактами шины (на рисунках отмечены вертикальными пунктирными линиями). В разные моменты времени одними и теми же сигнальными линиями управляют разные устройства шины, и для корректной (бесконфликтной) «передачи полномочий» требуется, чтобы существовал промежуток времени, в течение которого линией не управляет ни одно устройство. На временных диаграммах это событие — так называемый «пируэт» (turnaround) — обозначается парой полукруглых стрелок.

Таблица. сигналы шины PCI

| Сигнал | Назначение |

| AD[31:0] | Address/Data — мультиплексированная шина адреса/данных. В начале транзакции передается адрес, в последующих тактах — данные |

| C/B [3:0]# | Command/Byte Enable — команда/разрешение обращения к байтам. Команда, определяющая тип очередного цикла шины, задается четырехбитным кодом в фазе адреса |

| FRAME# | Кадр. Введением сигнала отмечается начало транзакции (фаза адреса), снятие сигнала указывает на то, что последующий цикл передачи данных является последним в транзакции |

| DEVSEL# | Device Select — устройство выбрано (ответ ЦУ на адресованную к нему транзакцию) |

| IRDY# | Initiator Ready — готовность ведущего устройства к обмену данными |

| TRDY# | Target Ready — готовность ЦУ к обмену данными |

| STOP# | Запрос ЦУ к ведущему устройству на остановку текущей транзакции |

| LOCK# | Сигнал блокировки (захвата) шины для обеспечения целостного выполнения операции. Используется мостом, которому для выполнения одной операции требуется выполнить несколько транзакций PCI |

| REQ# | Request — запрос от ведущего устройства на захват шины |

| GNT# | Grant — предоставление ведущему устройству управления шиной |

| PAR | Parity — общий бит четности для линий AD[31:0] и C/BE[3:0]# |

| PERR# | Parity Error — сигнал об ошибке четности (для всех циклов, кроме специальных). Вырабатывается любым устройством, обнаружившим ошибку |

| PME# | Power Management Event — сигнал о событиях, вызывающих изменение режима потребления (дополнительный сигнал, введенный в PCI 2.2) |

| CLKRUN# | Clock running — шина работает на номинальной частоте синхронизации. Снятие сигнала означает замедление или остановку синхронизации с целью снижения потребления (для мобильных применений) |

| PRSN [1,2]# | Present — индикаторы присутствия платы, кодирующие запрос потребляемой мощности. На карте расширения одна или две линии индикаторов соединяются с шиной GND, что воспринимается системной платой |

| RST# | Reset — сброс всех регистров в начальное состояние (по кнопке «Reset» и при перезагрузке) |

| IDSEL | Initialization Device Select — выбор устройства в циклах конфигурационного считывания и записи; на эти циклы отвечает устройство, обнаружившее на данной линии высокий уровень сигнала |

| SERR# | System Error — системная ошибка. Ошибка четности адреса или данных в специальном цикле или иная катастрофическая ошибка, обнаруженная устройством. Активизируется любым устройством PCI и вызывает NMI |

| REQ64# | Request 64 bit — запрос на 64-битный обмен. Сигнал вводится 64-битным инициатором, по времени он совпадает с сигналом FRAME#. Во время окончания сброса (сигналом RST#) сигнализирует 64-битному устройству о том, что оно подключено к 64-битной шине. Если 64-битное устройство не обнаружит этого сигнала, оно должно переконфигурироваться на 32-битный режим, отключив буферные схемы старших байтов |

| ACK64# | Подтверждение 64-битного обмена. Сигнал вводится 64-битным ЦУ, опознавшим свой адрес, одновременно с DEVSEL#. Отсутствие этого подтверждения заставит инициатор выполнять обмен с 32-битной разрядностью |

| INTA#, INTB#, INTC#, INTD# | Interrupt A, B, C, D — линии запросов прерывания, чувствительность к уровню, активный уровень — низкий, что допускает разделяемость (совместное использование) линий |

| CLK | Clock — тактовая частота шины. Должна лежать в пределах 20—33 МГц, начиная с PCI 2.1 может быть до 66 МГц, в PCI-X до 100 и 133 МГц |

| M66EN | 66MHz Enable — разрешение частоты синхронизации до 66 МГц (на картах 33 МГц заземлен, на 66 МГц — свободен) |

| PCIXCAP (38B) |

Возможности PCI-X: на платах PCI — заземлен, на PCI-X133 соединен с землей через конденсатор 0,01 мкФ, на PCI-X66 — параллельной RC-цепочкой 10 кОм, 0,01 мкФ.

Читайте также: Шины в смоленске для уаз патриот

В каждый момент времени шиной может управлять только одно ведущее устройство, получившее на это право от арбитра. Каждое ведущее устройство имеет пару сигналов — REQ# для запроса на управление шиной и GNT# для подтверждения предоставления управления шиной. Устройство может начинать транзакцию (устанавливать сигнал FRAME#) только при полученном активном сигнале GNT# и дождавшись отсутствия активности шины. Заметим, что за время ожидания покоя арбитр может «передумать» и отдать управление шиной другому устройству с более высоким приоритетом. Снятие сигнала GNT# не позволяет устройству начать следующую транзакцию, а при определенных условиях (см. далее) может заставить прекратить начатую транзакцию. Арбитражем запросов на использование шины занимается специальный узел — арбитр, входящий в мост, соединяющий данную шину с центром. Схема приоритетов (фиксированный, циклический, комбинированный) определяется программированием арбитра.

Для адреса и данных используются общие мультиплексированные линии AD. Четыре мультиплексированные линии C/BE[3:0] обеспечивают кодирование команд в фазе адреса и разрешение байтов в фазе данных. В транзакциях записи линии C/BE[3:0] разрешают использование байтов данных одновременно с их присутствием на шине AD, в транзакциях чтения эти сигналы относятся к байтам следующей за ними фазы данных. В фазе адреса (начало транзакции) ведущее устройство активирует сигнал FRAME#, передает целевой адрес по шине AD, а по линиям C/BE# — информацию о типе транзакции (команду). Адресованное целевое устройство отзывается сигналом DEVSEL#. Ведущее устройство указывает на свою готовность к обмену данными сигналом IRDY#, эта готовность может быть выставлена и до получения DEVSEL#. Когда и целевое устройство будет готово к обмену данными, оно установит сигнал TRDY#. Данные по шине AD передаются только при одновременном наличии сигналов IRDY# и TRDY#. С помощью этих сигналов ведущее и целевое устройства согласовывают свои скорости, вводя такты ожидания (wait states). На рисунке ниже приведена временная диаграмма обмена, в которой и ведущее и целевое устройства вводят такты ожидания. Если бы они оба ввели сигналы готовности в конце фазы адреса и не снимали бы их до конца обмена, то в каждом такте после фазы адреса передавались бы по 32 бита данных, что обеспечило бы выход на предельную производительность обмена. В транзакциях чтения после фазы адреса необходим дополнительный такт для пируэта, во время которого инициатор прекращает управление линией AD; целевое устройство сможет взять на себя управление шиной AD только в следующем такте. В транзакции записи пируэт не нужен, поскольку данные передает инициатор.

На шине PCI все транзакции трактуются как пакетные: каждая транзакция начинается фазой адреса, за которой может следовать одна или несколько фаз данных. Количество фаз данных в пакете явно не указывается, но в такте последней фазы данных ведущее устройство при введенном сигнале IRDY# снимает сигнал FRAME#. В одиночных транзакциях сигнал FRAME# активен лишь в течение одного такта. Если устройство не поддерживает пакетные транзакции в ведомом режиме, то оно должно потребовать прекращения пакетной транзакции в течение первой фазы данных (выставив сигнал STOP# одновременно с TRDY#). В ответ на это ведущее устройство завершит данную транзакцию и продолжит обмен последующей транзакцией со следующим значением адреса. После завершающей фазы данных ведущее устройство снимает сигнал IRDY#, и шина переходит в состояние покоя (Idle) — оба сигнала: — FRAME# и IRDY# — находятся в пассивном состоянии.

Инициатор может начать следующую транзакцию и без такта покоя, установив FRAME# одновременно со снятием IRDY#. Такие быстрые смежные транзакции (Fast Back-to-Back) могут быть обращены как к одному, так и к разным целевым устройствам. Первый тип быстрых смежных транзакций поддерживается всеми устройствами PCI, выступающими в роли целевого устройства. На поддержку второго типа смежных транзакций (такая поддержка необязательна) указывает бит 7 регистра состояния. Инициатору разрешают (если он умеет) использовать быстрые смежные транзакции с различными устройствами (разрешение определяется битом 9 регистра команд), только если все агенты шины допускают быстрые обращения. При обмене данных в режиме PCI-X быстрые смежные транзакции недопустимы.

Протокол шины обеспечивает надежность обмена — ведущее устройство всегда получает информацию об отработке транзакции целевым устройством. Средством повышения достоверности обмена является применение контроля четности: линии AD[31:0] и C/BE[3:0]# и в фазе адреса, и в фазе данных защищены битом четности PAR (количество установленных битов этих линий, включая PAR, должно быть четным). Действительное значение PAR появляется на шине с задержкой в один такт относительно линий AD и C/BE#. При обнаружении ошибки устройство вырабатывает сигнал PERR# (со сдвигом на такт после появления на шине действительного бита четности). В подсчете четности при передаче данных учитываются все байты, включая и недействительные (отмеченные высоким уровнем сигнала C/BEx#). Состояние бит, даже и в недействительных байтах данных, во время фазы данных должно оставаться стабильным.

Читайте также: Suzuki swift размеры шин

Каждая транзакция на шине должна быть завершена планово или прекращена, при этом шина должна перейти в состояние покоя (сигналы FRAME# и IRDY# пассивны). Завершение транзакции выполняется либо по инициативе ведущего устройства, либо по инициативе целевого устройства.

Ведущее устройство может завершить транзакцию одним из следующих способов:

- comletion — нормальное завершение по окончании обмена данными;

- time-out — завершение по тайм-ауту. Происходит, когда во время транзакции у ведущего устройства отбирают право на управление шиной (снятием сигнала GNT#), и истекает время, указанное в его таймере Latency Timer. Это может произойти, если адресованное целевое устройство оказалось непредвиденно медленным или запланирована слишком длинная транзакция. Короткие транзакции (с одной-двумя фазами данных) даже в случае снятия сигнала GNT# и срабатывания таймера завершаются нормально;

- master-Abort — прекращение транзакции, когда в течение заданного времени ведущее устройство не получает ответа от целевого устройства (сигнала DEVSEL#).

Транзакция может быть прекращена по инициативе целевого устройства; для этого оно может ввести сигнал STOP#. Возможны три типа прекращения транзакции:

- retry — повтор, введение сигнала STOP# при пассивном сигнале TRDY# до первой фазы данных. Эта ситуация возникает, когда целевое устройство изза внутренней занятости не успевает выдать первые данные в положенный срок (16 тактов). Прекращение типа retry является указанием ведущему устройству на необходимость повторного запуска той же транзакции;

- disconnect — отключение, введение сигнала STOP# в течение или после первой фазы данных. Если сигнал STOP# введен при активном сигнале TRDY# очередной фазы данных, то эти данные передаются, на чем транзакция и завершается. Если сигнал STOP# выставлен при пассивном сигнале TRDY#, то транзакция завершается без передачи данных очередной фазы. Отключение производится, когда целевое устройство не способно своевременно выдать или принять очередную порцию данных пакета. Отключение является указанием ведущему устройству на необходимость повторного запуска этой транзакции, но с модифицированным стартовым адресом;

- target-abort — отказ, введение сигнала STOP# одновременно со снятием сигнала DEVSEL# (в предыдущих случаях во время появления сигнала STOP# сигнал DEVSEL# был активен). После этого данные уже не передаются. Отказ производится, когда целевое устрйство обнаруживает фатальную ошибку или иные условия, по которым оно уже никак не сможет обслужить данный запрос (в том числе и неподдерживаемую команду).

Использование трех типов прекращения транзакции вовсе не обязательно для всех целевых устройств, однако любое ведущее устройство должно быть готово к завершению транзакций по любой из этих причин.

Прекращение типа retry используется для организации отложенных транзакций (delayed transactions). Отложенные транзакции используются только медленными целевыми устройствами, а также мостами PCI при трансляции транзакций на другую шину. Прекращая (для инициатора) транзакцию условием retry, целевое устройство внутренне выполняет данную транзакцию. Когда инициатор повторит эту транзакцию (выдаст ту же команду с тем же адресом и тем же набором сигналов C/BE# в фазе данных), у целевого устройства (или моста) уже будет готов результат (данные чтения или состояние выполнения записи), который оно быстро вернет инициатору. Результат отложенной транзакции, выполненной данным устройством, устройство или мост должны хранить до тех пор, пока результаты не будут запрошены инициатором. Однако он может и «забыть» повторить транзакцию (из-за каких-либо нештатных ситуаций). Чтобы избежать переполнения буфера хранения результатов, устройству приходится отбрасывать (discard) эти результаты. Отбрасывание может быть выполнено без побочных эффектов, если откладывалась транзакция к памяти, допускающей предвыборку (с атрибутом prefetchable, см. далее). Остальные типы транзакций в общем случае безнаказанно отбрасывать нельзя (может нарушиться целостность данных), для них отбрасывание разрешается только после безрезультатного ожидания повтора в течение 215 тактов шины (по срабатыванию discard timer). Об этой особой ситуации устройство может сообщить своему драйверу (или всей системе).

Инициатор транзакции может потребовать монопольного использования шины PCI на все время выполнения операции обмена, требующей нескольких шинных транзакций. Так, например, если центральный процессор выполняет инструкцию модификации данных в ячейке памяти, принадлежащей устройству PCI, ему нужно прочитать данные из устройства, модифицировать их в своем АЛУ и вернуть результат в устройство. Чтобы в эту операцию не вклинивались транзакции от других инициаторов (что чревато нарушением целостности данных), главный мост выполняет ее как блокированную — на все время исполнения операции подается шинный сигнал LOCK#. Этот сигнал никак не используется (и не вырабатывается) обычными устройствами PCI (не мостами); он используется только мостами для управления арбитражем.

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле

🔥 Видео

Что такое PCIe? Все виды скоростного интерфейса подключения PCIe 1.0-6.0 (x1 x4 x8 x18 x32)Скачать

Подробно про CAN шинуСкачать

ОБЪЯСНЯЕМ PCI Express 4.0Скачать

5 лекция "Шины AGP и PCI Express"Скачать

Цифровые интерфейсы и протоколыСкачать

Шина PCIСкачать

Системная шина персонального компьютера PCIСкачать

Лекция 281. Шина ISAСкачать

PCI и PCI-Express что можно подключитьСкачать

Как понять, когда протектор износился и шины пора менятьСкачать

Как работает компьютер? Шины адреса, управления и данных. Дешифрация. Взгляд изнутри!Скачать

Интеграционные шиныСкачать

поиск нерабочей can шины, часть дваСкачать

Китайская резина Maxxis SUV / SS-01Скачать

Системная шина персонального компьютера pci expressСкачать

Вот вам и китайская резинаСкачать

Компьютерная Энциклопедия

Компьютерная Энциклопедия