Системная шина процессора предназначена для обмена информацией микропроцессора с любыми внутренними устройствами микропроцессорной системы (контроллера или компьютера). В качестве обязательных устройств, которые входят в состав любой микропроцессорной системы, можно назвать ОЗУ, ПЗУ, таймер и порты ввода-вывода. Структурная схема простейшего микропроцессорного устройства приведена на рисунке 1.

В состав системной шины в зависимости от типа процессора входит одна или несколько шин адреса, одна или несколько шин данных и шина управления. Несколько шин данных и адреса применяется для увеличения производительности процессора и используется только в сигнальных процессорах. В универсальных процессорах и контроллерах обычно применяется одна шина адреса и одна шина данных.

В понятие шины вкладывают разное значение при рассмотрении различных вопросов. В простейшем случае под понятием шина подразумевают параллельно проложенные провода, по которым передаётся двоичная информация. При этом по каждому проводу передаётся отдельный двоичный разряд. Информация может передаваться в одном направлении, как, например, для шины адреса или шины управления, или в различных направлениях (для шины данных). По шине данных информация передаётся либо к процессору, либо от процессора в зависимости от операции записи или чтения, которую в данный момент осуществляет процессор.

В любом случае все сигналы, необходимые для работы системной шины формируются микросхемой процессора как это рассматривалось при изучении операционного блока. Иногда для увеличения скорости обработки информации функции управления системной шины берёт на себя отдельная микросхема (например контроллер прямого доступа к памяти или сопроцессор). Арбитраж доступа к системной шине при этом осуществляет контроллер системной шины (в простейшем случае достаточно сигнала занятости шины).

В некоторых случаях в понятие шина дополнительно включают требования по уровням напряжения, которыми представляются нули и единицы, передаваемые по её проводам. В состав требований могут быть включены длительности фронтов передаваемых сигналов, типы используемых разъёмов и их распайка, последовательность передаваемых сигналов и скорость их передачи.

Рисунок 1. Структурная схема подключения микропроцессорных устройств к системной шине

При подключении различных устройств к системной шине возникает вопрос — как различать эти устройства между собой? Единственный способ сделать это использовать индивидуальный адрес для каждого устройства, подключенного к системной шине микропроцессора. Так как адресация производится к каждой ячейке устройства индивидуально, то возникает понятие адресного пространства, занимаемого каждым устройством и адресного пространства микропроцессорного устройства в целом.

Адресное пространство микропроцессорного устройства.

Адресное пространство микропроцессорного устройства изображается графически прямоугольником, одна из сторон которого представляет разрядность адресуемой ячейки этого микропроцессора, а другая сторона — весь диапазон доступных адресов для этого же микропроцессора. Обычно в качестве минимально адресуемой ячейки памяти выбирается восьмиразрядная ячейка памяти (байт). Диапазон доступных адресов микропроцессора определяется разрядностью шины адреса системной шины. При этом минимальный номер ячейки памяти (адрес) будет равен 0, а максимальный определяется из формулы:

Для шестнадцатиразрядной шины это будет число 65535 (64K). Адресное пространство этой шины и распределение памяти микропроцессорной системы, изображённой на рисунке 1, приведено на рисунке 2, а распределение памяти микропроцессорной системы, изображённой на рисунке 1, приведено на рисунке 3.

Рисунок 2. Адресное пространство шестнадцатиразрядной шины адреса

Рисунок 3. Распределение памяти микропроцессора с шестнадцатиразрядной шиной адреса

Микропроцессоры после включения питания и выполнения процедуры сброса всегда начинают выполнение программы с определённого адреса, чаще всего нулевого. Однако есть и исключения. Например процессоры, на основе которых строятся универсальные компьютеры IBM PC или Macintosh стартуют не с нулевого адреса. Программа должна храниться в памяти, которая не стирается при выключении питания, то есть в ПЗУ.

Выберем для построения микропроцессорной системы микросхему ПЗУ объёмом 2 килобайта, как это показано на рисунке 1. При рассмотрении построения блока обработки сигналов мы договорились, что процессор после сброса начинает работу с нулевого адреса, поэтому разместим ПЗУ в адресном пространстве начиная с нулевого адреса. Для того, чтобы нулевая ячейка ПЗУ оказались расположенной по нулевому адресу адресного пространства микропроцессора, старшие разряды шины адреса должны быть равны 0.

Читайте также: Программное обеспечение сети шина

При построении схемы необходимо декодировать старшие пять разрядов адреса (определить, чтобы они были равны 0). Это выполняется при помощи дешифратора адреса, который в данном случае вырождается в пятивходовую схему «ИЛИ» Это связано с тем, что внутри ПЗУ уже есть одиннадцативходовый дешифратор адреса. При использовании дешифратора адреса, обращение к ячейкам памяти выше двух килобайт не приведёт к чтению ячеек ПЗУ, так как на входе выбора кристалла CS уровень напряжения останется высоким.

Теперь подключим микросхему ОЗУ. Для примера выберем микросхему объёмом 8 Кбайт. Для выбора любой из ячеек этой микросхемы достаточно тринадцатибитового адреса, поэтому необходимо дополнительно декодировать три оставшихся разряда адреса. Так как начальные ячейки памяти адресного пространства уже заняты ПЗУ, то использовать нельзя. Выберем следующую комбинацию цифр 001 и используем известные нам принципы построения схемы по произвольной таблице истинности. Дешифратор адреса выродится в данном случае в трёхвходовую схему «И-НЕ» с двумя инверторами на входе. Схема этого дешифратора приведена на рисунке 1. Приведённый дешифратор адреса обеспечивает нулевой уровень сигнала на входе CS только при комбинации старших бит 001. Обратите внимание, что так как объём ПЗУ меньше объёма ОЗУ, то между областью адресов ПЗУ и областью адресов ОЗУ образовалось пустое пространство неиспользуемых адресов памяти.

И, наконец, так как все микропроцессоры предназначены для обработки данных, поступающих извне, то в любой микропроцессорной системе должны присутствовать порты ввода-вывода. Порт ввода-вывода отображается в адресное пространство микропроцессорного устройства как одиночная ячейка памяти, поэтому порт ввода вывода можно разместить по любому свободному адресу. Проще всего построить дешифратор числа FFFFh. В этом случае дешифратор превращается в обычную 16-ти входовую схему «И-НЕ», поэтому и выберем эту ячейку памяти в адресном пространстве микропроцессора для размещения порта ввода-вывода.

Способы расширения адресного пространства микропроцессора.

Известно, что размер адресного пространства определяется разрядностью счётчика команд микропроцессора. Достаточно часто при развитии микропроцессорной системы возможности адресного пространства исчерпываются. В таком случае приходится прибегать к методам расширения адресного пространства.

Для расширения адресного пространства можно воспользоваться параллельным портом. Внешние выводы параллельного порта при этом используются в качестве старших битов адресной шины. Такой метод расширения адресного пространства называется страничным методом адресации. Регистр данных параллельного порта при использовании его для расширения адресного пространства будет называться переключателем страниц. Схема использования параллельного порта в качестве переключателя страниц памяти приведена на рисунке 4.

Рисунок 4. Использование параллельного порта в качестве переключателя страниц памяти

В этой схеме параллельный порт используется в качестве простейшего контроллера памяти микропроцессорного устройства. При применении восьмиразрядного параллельного порта в микропроцессорной системе появились дополнительные восемь линий адреса. В результате адресное пространство микропроцессорной системы увеличилось до 16 Мегабайт. Структура нового адресного пространства приведена на рисунке 5, а принцип формирования нового адреса с использованием переключателя страниц приведён на рисунке 6.

Рисунок 5. Структура страничного адресного пространства

Рисунок 6. Формирование адреса с использованием переключателя страниц

Метод страничной адресации прост в реализации и при формировании адреса физической памяти не приводит к дополнительным временным задержкам, но при использовании многозадачного режима работы процессора для каждой активной задачи выделяется целая страница в системной памяти микропроцессора. При такой работе в системной памяти процессора остаётся много неиспользуемых областей. Решить возникшую проблему позволяет метод сегментной организации памяти.

При сегментном методе организации памяти для расширения адресного пространства используется базовый регистр, относительно которого производится адресация команд или данных в программе. Разрядность базового регистра обычно выбирают равной разрядности счётчика команд. В качестве базового регистра, как и при страничной организации памяти, можно использовать параллельный порт.

Читайте также: Шипованные шины для севера

Для формирования физического адреса используется параллельный двоичный сумматор. На входы этого сумматора подаётся содержимое базового регистра и содержимое счётчика команд. Суммирование производится со смещением содержимого базового регистра влево на несколько бит относительно счётчика команд (рисунок 8). В результате максимальный размер сегмента определяется разрядностью программного счётчика, а максимальная неиспользуемая область памяти — смещением базового регистра относительно программного счётчика.

Адресное пространство при использовании сегментного метода адресации приведено на рисунке 7.

Рисунок 7. Пример адресного пространства с разделением на сегменты

Количество сегментов определяется количеством базовых регистров. Сегменты могут перекрываться в адресном пространстве, и тем самым может регулироваться размер памяти, который отводится под каждый конкретный сегмент памяти. В компьютерах семейства IBM PC имеются четыре базовых регистра, определяющих сегмент данных, сегмент программы, сегмент стека и дополнительный сегмент. Информацию в базовые регистры заносит операционная система при переключении задач.

Рисунок 8. Формирование адреса при сегментной адресации

Ещё одним распространённым способом увеличения адресного пространства является применение окон. При использовании окон производится расширение не всего адресного пространства, а только его части. Внутри адресного пространства выделяется некоторая область, которая называется окном. В это окно может отображаться часть другого адресного пространства.

При использовании окон может быть использован как страничный метод отображения адресного пространства, так и сегментный метод отображения адресного пространства в окно.

При использовании страничного метода отображения, конкретная страница другого адресного пространства, которая в данный момент отображается в окно памяти, определяется переключателем страниц, построенному по такому же принципу как это было рассмотрено на рисунке 4.

При использовании сегментного метода отображения, конкретная область адресного пространства, которая будет отображаться в окно, определяется содержимым базового регистра. Если разрядность адреса вспомогательного адресного пространства, отображаемого в окно основной памяти, совпадает с разрядностью базового регистра, то любая область вспомогательной памяти может быть отображена в основную память с точностью до байта.

Принцип построения оконной адресации при отображении страниц показан на рисунке 9.

Рисунок 9. Применение окна для расширения адресного пространства

Оконная адресация часто используется при развитии микропроцессорных семейств, когда размера областей памяти, отведённых для конкретных задач в младших моделях семейства, не хватает для старших моделей семейства, а при этом нужно поддерживать аппаратную совместимость с младшими моделями семейства. В качестве примера можно привести микросхемы I81c96 фирмы INTEL или TMS320c5410 фирмы Texas Instrument, где для расширения области регистров специальных функций используется оконная адресация.

Понравился материал? Поделись с друзьями!

Вместе со статьей «Системная шина микропроцессора» читают:

Шины микропроцессорной системы

Шина данных — это основная шина, ради которой и создается вся система. Количество ее разрядов (линий связи) определяет скорость и эффективность информационного обмена, а также максимально возможное количество команд.

Шина данных всегда двунаправленная, так как предполагает передачу информации в обоих направлениях. Наиболее часто встречающийся тип выходного каскада для линий этой шины — выход с тремя состояниями.

Обычно шина данных имеет 8, 16, 32 или 64 разряда. Разрядность шины данных определяет и разрядность всей магистрали.

Шина адреса — вторая по важности шина, которая определяет максимально возможную сложность микропроцессорной системы, то есть допустимый объем памяти и, следовательно, максимально возможный размер программы и максимально возможный объем запоминаемых данных. Количество адресов, обеспечиваемых шиной адреса, определяется как 2N, где N — количество разрядов. Например, 16-разрядная шина адреса обеспечивает 65 536 адресов. Разрядность шины адреса обычно кратна 4 и может достигать 32 и даже 64. Шина адреса может быть однонаправленной (когда магистралью всегда управляет только процессор) или двунаправленной (когда процессор может временно передавать управление магистралью другому устройству, например контроллеру ПДП). Наиболее часто используются типы выходных каскадов с тремя состояниями или обычные ТТЛ (с двумя состояниями).

Читайте также: Запчасти в самаре шины

Как в шине данных, так и в шине адреса может использоваться положительная логика или отрицательная логика. При положительной логике высокий уровень напряжения соответствует логической единице на соответствующей линии связи, низкий — логическому нулю. При отрицательной логике — наоборот. В большинстве случаев уровни сигналов на шинах — ТТЛ.

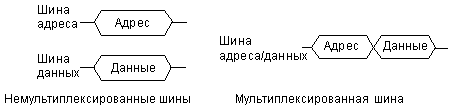

Для снижения общего количества линий связи магистрали часто применяется мультиплексирование шин адреса и данных. То есть одни и те же линии связи используются в разные моменты времени для передачи как адреса, так и данных (в начале цикла — адрес, в конце цикла — данные). Для фиксации этих моментов (стробирования) служат специальные сигналы на шине управления. Понятно, что мультиплексированная шина адреса/данных обеспечивает меньшую скорость обмена, требует более длительного цикла обмена (рис. 2.1). По типу шины адреса и шины данных все магистрали также делятся на мультиплексированные и немультиплексированные.

Рис.2. 1. Мультиплексирование шин адреса и данных.

В некоторых мультиплексированных магистралях после одного кода адреса передается несколько кодов данных (массив данных). Это позволяет существенно повысить быстродействие магистрали. Иногда в магистралях применяется частичное мультиплексирование, то есть часть разрядов данных передается по немультиплексированным линиям, а другая часть — по мультиплексированным с адресом линиям.

Шина управления — это вспомогательная шина, управляющие сигналы на которой определяют тип текущего цикла и фиксируют моменты времени, соответствующие разным частям или стадиям цикла. Кроме того, управляющие сигналы обеспечивают согласование работы процессора (или другого хозяина магистрали, задатчика, master) с работой памяти или устройства ввода/вывода (устройства-исполнителя, slave). Управляющие сигналы также обслуживают запрос и предоставление прерываний, запрос и предоставление прямого доступа.

Сигналы шины управления могут передаваться как в положительной логике (реже), так и в отрицательной логике (чаще). Линии шины управления могут быть как однонаправленными, так и двунаправленными. Типы выходных каскадов могут быть самыми разными: с двумя состояниями (для однонаправленных линий), с тремя состояниями (для двунаправленных линий), с открытым коллектором (для двунаправленных и мультиплексированных линий).

Самые главные управляющие сигналы — это стробы обмена, то есть сигналы, формируемые процессором и определяющие моменты времени, в которые производится пересылка данных по шине данных, обмен данными. Чаще всего в магистрали используются два различных строба обмена:

Строб записи (вывода), который определяет момент времени, когда устройство-исполнитель может принимать данные, выставленные процессором на шину данных;

Строб чтения (ввода), который определяет момент времени, когда устройство-исполнитель должно выдать на шину данных код данных, который будет прочитан процессором.

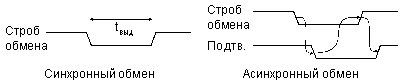

При этом большое значение имеет то, как процессор заканчивает обмен в пределах цикла, в какой момент он снимает свой строб обмена. Возможны два пути решения (рис. 2.2):

При синхронном обмене процессор заканчивает обмен данными самостоятельно, через раз и навсегда установленный временной интервал выдержки (tвыд), то есть без учета интересов устройства-исполнителя;

При асинхронном обмене процессор заканчивает обмен только тогда, когда устройство-исполнитель подтверждает выполнение операции специальным сигналом (так называемый режим handshake — рукопожатие).

Рис. 2.2. Синхронный обмен и асинхронный обмен.

Достоинства синхронного обмена — более простой протокол обмена, меньшее количество управляющих сигналов. Недостатки — отсутствие гарантии, что исполнитель выполнил требуемую операцию, а также высокие требования к быстродействию исполнителя.

Достоинства асинхронного обмена — более надежная пересылка данных, возможность работы с самыми разными по быстродействию исполнителями. Недостаток — необходимость формирования сигнала подтверждения всеми исполнителями, то есть дополнительные аппаратурные затраты.

По используемому типу обмена магистрали микропроцессорных систем также делятся на синхронные и асинхронные.

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле