Шина данных — это основная шина, ради которой и создается вся система. Количество ее разрядов (линий связи) определяет скорость и эффективность информационного обмена, а также максимально возможное количество команд.

Шина данных всегда двунаправленная, так как предполагает передачу информации в обоих направлениях. Наиболее часто встречающийся тип выходного каскада для линий этой шины — выход с тремя состояниями.

Обычно шина данных имеет 8, 16, 32 или 64 разряда. Разрядность шины данных определяет и разрядность всей магистрали.

Шина адреса — вторая по важности шина, которая определяет максимально возможную сложность микропроцессорной системы, то есть допустимый объем памяти и, следовательно, максимально возможный размер программы и максимально возможный объем запоминаемых данных. Количество адресов, обеспечиваемых шиной адреса, определяется как 2N, где N — количество разрядов. Например, 16-разрядная шина адреса обеспечивает 65 536 адресов. Разрядность шины адреса обычно кратна 4 и может достигать 32 и даже 64. Шина адреса может быть однонаправленной (когда магистралью всегда управляет только процессор) или двунаправленной (когда процессор может временно передавать управление магистралью другому устройству, например контроллеру ПДП). Наиболее часто используются типы выходных каскадов с тремя состояниями или обычные ТТЛ (с двумя состояниями).

Как в шине данных, так и в шине адреса может использоваться положительная логика или отрицательная логика. При положительной логике высокий уровень напряжения соответствует логической единице на соответствующей линии связи, низкий — логическому нулю. При отрицательной логике — наоборот. В большинстве случаев уровни сигналов на шинах — ТТЛ.

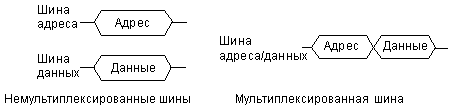

Для снижения общего количества линий связи магистрали часто применяется мультиплексирование шин адреса и данных. То есть одни и те же линии связи используются в разные моменты времени для передачи как адреса, так и данных (в начале цикла — адрес, в конце цикла — данные). Для фиксации этих моментов (стробирования) служат специальные сигналы на шине управления. Понятно, что мультиплексированная шина адреса/данных обеспечивает меньшую скорость обмена, требует более длительного цикла обмена (рис. 2.1). По типу шины адреса и шины данных все магистрали также делятся на мультиплексированные и немультиплексированные.

Рис.2. 1. Мультиплексирование шин адреса и данных.

В некоторых мультиплексированных магистралях после одного кода адреса передается несколько кодов данных (массив данных). Это позволяет существенно повысить быстродействие магистрали. Иногда в магистралях применяется частичное мультиплексирование, то есть часть разрядов данных передается по немультиплексированным линиям, а другая часть — по мультиплексированным с адресом линиям.

Шина управления — это вспомогательная шина, управляющие сигналы на которой определяют тип текущего цикла и фиксируют моменты времени, соответствующие разным частям или стадиям цикла. Кроме того, управляющие сигналы обеспечивают согласование работы процессора (или другого хозяина магистрали, задатчика, master) с работой памяти или устройства ввода/вывода (устройства-исполнителя, slave). Управляющие сигналы также обслуживают запрос и предоставление прерываний, запрос и предоставление прямого доступа.

Сигналы шины управления могут передаваться как в положительной логике (реже), так и в отрицательной логике (чаще). Линии шины управления могут быть как однонаправленными, так и двунаправленными. Типы выходных каскадов могут быть самыми разными: с двумя состояниями (для однонаправленных линий), с тремя состояниями (для двунаправленных линий), с открытым коллектором (для двунаправленных и мультиплексированных линий).

Самые главные управляющие сигналы — это стробы обмена, то есть сигналы, формируемые процессором и определяющие моменты времени, в которые производится пересылка данных по шине данных, обмен данными. Чаще всего в магистрали используются два различных строба обмена:

Строб записи (вывода), который определяет момент времени, когда устройство-исполнитель может принимать данные, выставленные процессором на шину данных;

Строб чтения (ввода), который определяет момент времени, когда устройство-исполнитель должно выдать на шину данных код данных, который будет прочитан процессором.

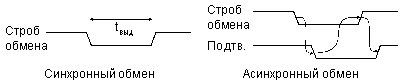

При этом большое значение имеет то, как процессор заканчивает обмен в пределах цикла, в какой момент он снимает свой строб обмена. Возможны два пути решения (рис. 2.2):

При синхронном обмене процессор заканчивает обмен данными самостоятельно, через раз и навсегда установленный временной интервал выдержки (tвыд), то есть без учета интересов устройства-исполнителя;

При асинхронном обмене процессор заканчивает обмен только тогда, когда устройство-исполнитель подтверждает выполнение операции специальным сигналом (так называемый режим handshake — рукопожатие).

Рис. 2.2. Синхронный обмен и асинхронный обмен.

Достоинства синхронного обмена — более простой протокол обмена, меньшее количество управляющих сигналов. Недостатки — отсутствие гарантии, что исполнитель выполнил требуемую операцию, а также высокие требования к быстродействию исполнителя.

Достоинства асинхронного обмена — более надежная пересылка данных, возможность работы с самыми разными по быстродействию исполнителями. Недостаток — необходимость формирования сигнала подтверждения всеми исполнителями, то есть дополнительные аппаратурные затраты.

По используемому типу обмена магистрали микропроцессорных систем также делятся на синхронные и асинхронные.

Видео:Понятие Микропроцессорной системыСкачать

Шины микропроцессорной системы и циклы обмена: шины микропроцессорной системы

6.1. Шины микропроцессорной системы и циклы обмена: шины микропроцессорной системы

В системную магистраль (шину) микропроцессорной системы входит три основные информационные шины: адреса, данных и управления.

Шина данных — это основная шина, ради которой и создается вся система. Количество ее разрядов (линий связи) определяет скорость и эффективность информационного обмена, а также максимально возможное количество команд.

Шина данных всегда двунаправленная, так как предполагает передачу информации в обоих направлениях. Наиболее часто встречающийся тип выходного каскада для линий этой шины — выход с тремя состояниями.

Обычно шина данных имеет 8, 16, 32 или 64 разряда. Разрядность шины данных определяет и разрядность всей магистрали.

Шина адреса — вторая по важности шина, которая определяет максимально возможную сложность микропроцессорной системы, то есть допустимый объем памяти и, следовательно, максимально возможный размер программы и максимально возможный объем запоминаемых данных. Количество адресов, обеспечиваемых шиной адреса, определяется как 2N, где N — количество разрядов. Например, 16-разрядная шина адреса обеспечиваетадресов. Шина адреса может быть однонаправленной (когда магистралью всегда управляет только процессор) или двунаправленной (когда процессор может временно передавать управление магистралью другому устройству, например контроллеру ПДП). Наиболее часто используются типы выходных каскадов с тремя состояниями или обычные ТТЛ (с двумя состояниями).

Как в шине данных, так и в шине адреса может использоваться положительная логика или отрицательная логика. В большинстве случаев уровни сигналов на шинах — ТТЛ.

Для снижения общего количества линий связи магистрали часто применяется мультиплексирование шин адреса и данных. То есть одни и те же линии связи используются в разные моменты времени для передачи как адреса, так и данных (в начале цикла — адрес, в конце цикла — данные). Для фиксации этих моментов (стробирования) служат специальные сигналы на шине управления. Понятно, что мультиплексированная шина адреса/данных обеспечивает меньшую скорость обмена, требует более длительного цикла обмена (рис. 2.1). По типу шины адреса и шины данных все магистрали также делятся на мультиплексированные и немультиплексированные.

Рис. 2.1. Мультиплексирование шин адреса и данных.

В некоторых мультиплексированных магистралях после одного кода адреса передается несколько кодов данных (массив данных). Это позволяет существенно повысить быстродействие магистрали. Иногда в магистралях применяется частичное мультиплексирование, то есть часть разрядов данных передается по немультиплексированным линиям, а другая часть — по мультиплексированным с адресом линиям.

Шина управления — это вспомогательная шина, управляющие сигналы на которой определяют тип текущего цикла и фиксируют моменты времени, соответствующие разным частям или стадиям цикла. Кроме того, управляющие сигналы обеспечивают согласование работы процессора (или другого хозяина магистрали, задатчика, master) с работой памяти или устройства ввода/вывода (устройства-исполнителя, slave). Управляющие сигналы также обслуживают запрос и предоставление прерываний, запрос и предоставление прямого доступа.

Сигналы шины управления могут передаваться как в положительной логике (реже), так и в отрицательной логике (чаще). Линии шины управления могут быть как однонаправленными, так и двунаправленными. Типы выходных каскадов могут быть самыми разными: с двумя состояниями (для однонаправленных линий), с тремя состояниями (для двунаправленных линий), с открытым коллектором (для двунаправленных и мультиплексированных линий).

Самые главные управляющие сигналы — это стробы обмена, то есть сигналы, формируемые процессором и определяющие моменты времени, в которые производится пересылка данных по шине данных, обмен данными. Чаще всего в магистрали используются два различных строба обмена:

Читайте также: Неисправности автомобильного компрессора для подкачки шин

- Строб записи (вывода), который определяет момент времени, когда устройство-исполнитель может принимать данные, выставленные процессором на шину данных; Строб чтения (ввода), который определяет момент времени, когда устройство-исполнитель должно выдать на шину данных код данных, который будет прочитан процессором.

При этом большое значение имеет то, как процессор заканчивает обмен в пределах цикла, в какой момент он снимает свой строб обмена. Возможны два пути решения (рис. 2.2):

- При синхронном обмене процессор заканчивает обмен данными самостоятельно, через раз и навсегда установленный временной интервал выдержки (tвыд), то есть без учета интересов устройства-исполнителя; При асинхронном обмене процессор заканчивает обмен только тогда, когда устройство-исполнитель подтверждает выполнение операции специальным сигналом (так называемый режим handshake — рукопожатие).

Рис. 2.2. Синхронный обмен и асинхронный обмен.

Достоинства синхронного обмена — более простой протокол обмена, меньшее количество управляющих сигналов. Недостатки — отсутствие гарантии, что исполнитель выполнил требуемую операцию, а также высокие требования к быстродействию исполнителя.

Достоинства асинхронного обмена — более надежная пересылка данных, возможность работы с самыми разными по быстродействию исполнителями. Недостаток — необходимость формирования сигнала подтверждения всеми исполнителями, то есть дополнительные аппаратурные затраты.

По используемому типу обмена магистрали микропроцессорных систем также делятся на синхронные и асинхронные.

Данные передаются, начиная со значимого бита. Если приёмник не может принять еще один целый байт, пока он не выполнит какую-либо другую функцию (например, обслужит внутреннее прерывание), он может удерживать линию SCL = 0, переводя передатчик в состояние ожидания. Пересылка данных продолжается, когда приёмник будет готов к следующему байту и отпустит линию SCL.

Пересылка данных по шине I2C

Сигнал СТАРТ Старший разряд байта Сигнал подтверждения от приёмника Прием байта завершен. Прерывание внутри приемника Синхролиния удерживается в низком состоянии, пока обслуживается прерывание Сигнал подтверждения от приемника Сигнал СТОП

Видео:Системная шина процессораСкачать

Подтверждение

Передача 8 бит данных от передатчика к приемнику завершаются дополнительным циклом (формированием 9-го тактового импульса линии SCL), при котором приемник выставляет низкий уровень сигнала на линии SDA, как признак успешного приема байта.

Подтверждение при передаче данных обязательно. Соответствующий импульс синхронизации генерируется ведущим. Передатчик устанавливает линию SDA = 1 на время синхроимпульса подтверждения. Приёмник должен удерживать линию SDA = 0 пока SCL = 1.

Данные, переданные передатчиком Данные, переданные приёмником SCL от ведущего Сигнал СТАРТ Синхроимпульс подтверждения

В том случае, когда ведомый-приёмник не может подтвердить свой адрес (например, когда он выполняет в данный момент какие-либо функции реального времени), линия данных должна быть оставлена в высоком состоянии. После этого ведущий может выдать сигнал СТОП для прерывания пересылки данных.

Если в пересылке участвует ведущий-приёмник, то он должен сообщить об окончании передачи ведомому-передатчику путем не подтверждения последнего байта. Ведомый-передатчик должен освободить линию данных для того, чтобы позволить ведущему выдать сигнал СТОП или повторить сигнал СТАРТ.

7.1. Шины микропроцессорной системы и циклы обмена: циклы программного обмена

Средний уровень сигналов на шине AD обозначает, что состояния сигналов на шине в данные временные интервалы не важны. Для стробирования адреса используется отрицательный синхросигнал — SYNC, выставляемый также процессором. Его передний (отрицательный) фронт соответствует действительности кода адреса на шине AD. Фаза адреса одинакова в обоих циклах записи и чтения.

Рис. 2.3. Цикл чтения на магистрали Q-bus.

Рис. 2.4. Цикл записи на магистрали Q-bus.

Для сигнала — RPLY используется тип выходного каскада ОК, чтобы не было конфликтов между устройствами-исполнителями.

На данной магистрали адрес передается синхронно (без подтверждения его получения исполнителем), а данные передаются асинхронно, с обязательным подтверждением их выдачи или приема исполнителем. Отсутствие сигнала подтверждения — RPLY в течение заданного времени воспринимается процессором как аварийная ситуация. В принципе возможна и асинхронная передача адреса, что увеличивает надежность обмена, хотя может снижать его скорость.

Помимо циклов чтения и записи на магистрали Q-bus используются также и циклы типа «ввод-пауза-вывод» («чтение-модификация-запись»). Упрощенная временная диаграмма этого цикла представлена на рис. 2.5.

Рис. 2.5. Цикл «ввод-пауза-вывод» на магистрали Q-bus.

В этом цикле адресная фаза производится точно так же, как и в циклах чтения (ввода) и записи (вывода). Но в фазе данных процессор производит сначала чтение из заданного в адресной фазе адреса, а потом запись в тот же самый адрес. Для чтения используется строб чтения — DIN, а для записи – строб записи — DOUT. В ответ на сигнал — DIN устройство-исполнитель выдает свои данные на шину AD, а по сигналу — DOUT – принимает данные с шины AD. Как и в циклах чтения и записи, устройство-исполнитель подтверждает выполнение каждой операции сигналом подтверждения — RPLY. Понятно, что цикл «ввод-пауза-вывод» требует больше времени, чем каждый из циклов чтения или записи, но меньше времени, чем два последовательно произведенных цикла чтения и записи (так как для него нужна только одна адресная фаза). Сигнал — SYNC вырабатывается процессором в начале цикла «ввод-пауза-вывод» и держится до окончания всего цикла.

Рис. 2.6. Цикл чтения из УВВ на магистрали ISA.

Рис. 2.7. Цикл записи в УВВ на магистрали ISA.

На магистрали ISA также предусмотрена возможность и асинхронного обмена. Для этого применяется сигнал готовности канала (магистрали) I/O CH RDY, который исполняющим устройством устанавливается в уровень логического нуля, запрещая тем самым дальнейшее выполнение операции и продляя строб обмена. Тип выходного каскада для данного сигнала — ОК, для предотвращения конфликтов между устройствами-исполнителями. При синхронном обмене сигнал I/O CH RDY всегда положительный.

Арбитраж выполняется на линии SDA при высоком уровне линии SCL. Устройство, которое формирует на линии SDA высокий уровень когда другое передает низкий, теряет право брать «Master» и должно перейти в режим «Slave». «Master», потерявший инициативу на шине, может формировать тактовые импульсы до конца байта, в котором потерял свойства ведущего.

Вследствие того, что арбитраж зависит только от адреса и данных, передаваемых соревнующимися ведущими, не существует центрального ведущего, а также приоритетного доступа к шине.

8.1 Шины микропроцессорной системы и циклы обмена: циклы обмена по прерываниям

Циклы обмена в режиме прерываний строятся по тем же принципам, что и циклы программного обмена, но имеют ряд специфических особенностей.

Прерывания в микропроцессорных системах бывают двух основных типов:

- векторные прерывания, которые требуют проведения цикла чтения по магистрали; радиальные прерывания, которые не требуют никакого цикла обмена по магистрали.

Дело в том, что прерываний в микропроцессорной системе обычно бывает много. Поэтому процессору необходима информация о номере (или, как еще говорят, об адресе вектора) конкретного прерывания. Эта информация может быть передана процессору двумя путями.

При векторном прерывании код номера прерывания передается процессору тем устройством ввода/вывода, которое данное прерывание запросило. Для этого процессор проводит цикл чтения по магистрали, и по шине данных получает код номера прерывания. Шина адреса в данном цикле обычно не используется, так как устройство, запросившее прерывание, и так знает, что процессор будет обращаться именно к нему. В этом случае в магистрали достаточно всего одной линии запроса прерывания для всех устройств ввода/вывода. Так организованы прерывания, например, в магистрали Q-bus.

Рис. 2.8. Сигналы запроса и предоставления прерывания в магистрали Q-bus.

Схема распространения сигналов, участвующих в прерываниях на магистрали Q-bus, показана на рис. 2.8. Упрощенная временная диаграмма цикла запроса и предоставления магистрали представлена на рис. 2.9.

Рис. 2.9. Цикл запроса/предоставления векторного прерывания на магистрали Q-bus.

Запрос прерывания осуществляется отрицательным сигналом — VIRQ, который может формироваться каждым из устройств, запрашивающих прерывание. Тип выходного каскада для этого сигнала — ОК, чтобы избежать конфликтов между запрашивающими прерывания устройствами. Получив сигнал — VIRQ, процессор предоставляет прерывание (закончив предварительно выполнение текущей команды). Для этого он выставляет сигнал чтения данных — DIN и сигнал предоставления прерывания IAKO. Этот сигнал IAKO последовательно проходит через все устройства, которые могут запрашивать прерывания. Если устройство запросило прерывание, то оно не пропускает через себя этот сигнал. В результате получается, что если прерывания одновременно запросили два или более устройств, то сигнал предоставления прерывания получит только одно устройство, а именно то, которое ближе к процессору. Такой механизм разрешения конфликтов называется иногда географическим приоритетом (или цепочечным приоритетом, Daisy Chain). Получив сигнал IAKO, устройство, запросившее прерывание, должно снять свой сигнал — VIRQ.

Читайте также: Размер шин тойота пассо 2016

Затем процессор проводит цикл безадресного чтения номера прерывания. В ответ на полученные сигналы — DIN и IAKO устройство, которому предоставлено прерывание, должно выдать на шину адреса/данных AD код номера прерывания (адреса вектора прерывания) и выставить сигнал подтверждения — RPLY. Процессор читает код номера прерывания и заканчивает цикл безадресного чтения снятием сигналов — DIN и IAKO.

Рис. 2.10. Структура связей для организации радиальных прерываний на магистрали ISA.

При радиальном прерывании в магистрали имеется столько линий запроса прерывания, сколько всего может быть разных прерываний. То есть каждое устройство ввода/вывода, желающее использовать прерывание, подает сигнал запроса прерывания по своей отдельной линии. Процессор узнает о номере прерывания по номеру линии, по которой пришел сигнал запроса прерывания. Никаких циклов обмена по магистрали при этом не требуется. В случае радиальных прерываний в систему обычно включается дополнительная микросхема контроллера прерываний, обрабатывающая сигналы запросов прерываний. Именно так организованы прерывания, например, в магистрали ISA.

Упрощенная структура связей между устройствами, участвующими в обмене по прерываниям, на магистрали ISA показана на рис. 2.10. Процессор общается с контроллером прерываний как по магистрали (чтобы задать ему режимы работы), так и вне магистрали (при обработке запросов на прерывание). Сигналы запросов прерываний IRQ распределяются между всеми устройствами магистрали. На каждую линию IRQ приходится одно устройство. Тип выходного каскада для этих линий — 2С, так как конфликты здесь не предусмотрены. Запросом прерывания является передний, положительный фронт сигнала IRQ. При одновременном поступлении сигналов IRQ от нескольких устройств порядок их обслуживания определяется контроллером прерываний.

Какой тип прерываний лучше — векторный или радиальный?

Векторные прерывания обеспечивают системе большую гибкость, в системе их может быть очень много. Но зато они требуют дополнительных аппаратурных узлов во всех устройствах, запрашивающих прерывания, для обслуживания циклов безадресного чтения.

Радиальных прерываний в системе обычно не очень много (от 1 до 16). При этом типе прерываний, как правило, требуется введение в систему специального контроллера прерываний. Каждое радиальное прерывание требует введения дополнительной линии в шину управления системной магистрали. Но работать с радиальными прерываниями проще, так как все сводится только к выработке единственного сигнала IRQ, и никаких циклов обмена по магистрали не требуется.

Посылки данных происходят в формате, показанном на рис. 11. После сигнала СТАРТ посылается адрес ведомого. После 7 бит адреса следует бит направления данных (R/W^), “ноль” означает передачу (запись), а “единица” — прием (чтение). Пересылка данных всегда заканчивается сигналом СТОП, генерируемым ведущим. Однако, если ведущий желает оставаться на шине дальше, он должен выдать повторный сигнал СТАРТ и затем адрес следующего устройства. При таком формате посылки возможны различные комбинации чтения/записи.

- Ведущий-передатчик передает ведомому-приёмнику. Направление пересылки данных не изменяется Ведущий читает ведомого немедленно после пересылки первого байта (рис. 13). В момент первого подтверждения ведущий-передатчик становится ведущим-приёмником и ведомый-приёмник становится ведомым-передатчиком. Подтверждение тем не менее генерируется ведомым. Сигнал СТОП генерируется ведущим Комбинированный формат (рис. 14). При изменении направления пересылки данных повторяется сигнал СТАРТ и адрес ведомого, но бит направления данных инвертируется. Если ведущий-приёмник посылает повторный сигнал СТАРТ, он обязан предварительно послать сигнал неподтверждения.

Рисунок 12. Ведущий-передатчик адресует ведомого-приемника 7-битным адресом. Направление пересылки не изменяется

От ведущего к ведомому От ведомого к ведущему Адрес ведомого Бит направления Данные Пересылаемые данные (n байт + подтверждение) А — Подтверждение Неподтверждение Сигнал СТАРТ Сигнал СТОП

Рисунок 13. Ведущий читает из ведомого непосредственно после первого байта

Рисунок 14. Комбинированный формат

Адрес ведомого Чтение или запись n байтов + подтверждения Сигнал повторного СТАРТА Направление пересылки может измениться в этой точке Направление пересылки данных и битов подтверждения зависит от битов направления

Процедура адресации на шине I2C заключается в том, что первый байт после сигнала СТАРТ определяет, какой ведомый выбирается ведущим для работы. Исключение составляет адрес “Общего вызова”, который адресует все устройства на шине. Когда используется этот адрес, все устройства в теории должны послать сигнал подтверждения. Однако, устройства могут быть сделаны игнорирующими этот адрес. Второй байт посылки общего вызова определяет действие, которое должны произвести устройства. Более подробно процедура описана в разделе Назначение битов первого байта.

9.1. Шины микропроцессорной системы и циклы обмена: циклы обмена в режиме ПДП

Циклы обмена в режиме прямого доступа к памяти выполняются по тем же правилам, что и циклы программного обмена, и циклы предоставления прерываний.

Прежде чем начать обмен в режиме ПДП, устройство, которому необходим ПДП, должно запросить ПДП и получить его. Процедура запроса и предоставления ПДП очень похожа на процедуру запроса и предоставления прерывания. В обоих случаях устройство, требующее обслуживания, посылает сигнал запроса процессору. Однако в случае ПДП процессор обязательно должен предоставить ПДП запросившему устройству с помощью специальных сигналов, так как на время ПДП процессор отключается от магистрали. А при радиальных прерываниях предоставления прерывания от процессора не требуется.

На магистрали Q-bus запрос и предоставление ПДП организуются подобно запросу и предоставлению прерывания. Упрощенная структура связей устройств, участвующих в ПДП, показана на рис. 2.11. Временная диаграмма запроса/предоставления ПДП очень близка к временной диаграмме запроса/предоставления прерывания (см. рис. 2.9).

Рис. 2.11. Структура связей запроса/предоставления ПДП на магистрали Q-bus.

Сигнал запроса ПДП, называемый — DMR, передается всеми устройствами, нуждающимися в ПДП, по одной линии магистрали. Тип выходного каскада на этой линии — ОК. Процессор, получив сигнал — DMR, выдает сигнал предоставления ПДП DMGO, аналогичный сигналу IAKO. Этот сигнал также проходит через все устройства последовательно, в результате чего ПДП получает только то устройство, которое находится ближе к процессору (географический приоритет). А затем устройство, получившее ПДП, проводит циклы обмена по магистрали, аналогично циклам программного обмена. В циклах ПДП информация читается из памяти и записывается в устройство ввода/вывода, или наоборот — читается из устройства ввода/вывода и передается в память.

На магистрали ISA запрос/предоставление ПДП очень напоминает организацию радиальных прерываний (рис. 2.12). Точно так же в системе существует контроллер ПДП, к которому сходятся сигналы запроса ПДП, называемые DRQ, и от которого расходятся сигналы предоставления ПДП, называемые — DACK. К каждому каналу ПДП (пара сигналов DRQ и — DACK) подключается только одно устройство, запрашивающее ПДП. Тип выходных каскадов для этих сигналов —2С. Устройство, нуждающееся в ПДП, посылает сигнал запроса DRQ и получает в ответ сигнал предоставления — DACK. После этого контроллер ПДП проводит циклы обмена по магистрали между устройством ввода/вывода и памятью.

Упрощенная временная диаграмма циклов ПДП на магистрали ISA показана на рис. 2.13.

На магистрали ISA используются раздельные стробы записи в память (-MEMW) и записи в устройства ввода/вывода (-IOW), а также раздельные стробы чтения из памяти (-MEMR) и чтения из устройств ввода/вывода (-IOR). Это позволяет за один цикл обмена ПДП читать информацию из памяти и записывать ее в устройство ввода/вывода или же читать информацию из устройства ввода/вывода и записывать ее в память. При этом на шине адреса выставляется адрес памяти, а адрес устройства ввода/вывода заменяется одним-единственным сигналом AEN. Естественно, в цикле обмена в режиме ПДП участвует только то устройство ввода/вывода, которое предварительно запросило ПДП и которому ПДП было предоставлено. Поэтому никаких конфликтов между устройствами ввода/вывода из-за такой упрощенной адресации не возникает.

Рис. 2.12. Структура связей запроса/предоставления ПДП на магистрали ISA.

Читайте также: Устройства для хранения шин

Рис. 2.13. Цикл ПДП на магистрали ISA.

10-битная адресация не меняет формат шины. Для этого используется зарезервированная адресная комбинация 1111ХХХ первых семи бит первого байта. 10-битная адресация не влияет на существующую 7-битную адресацию. Устройства с 7-битной и 10-битной адресацией могут быть подключены к одной шине.

Хотя имеются восемь возможных комбинаций последовательности 1111ХХХ, из них используются только четыре — 11110ХХ. Комбинации типа 11111ХХ зарезервированы для дальнейших улучшений шины.

10-битный адрес формируется из первых двух байтов. Первые семь бит первого байта являются комбинацией вида 11110ХХ, где два младших бита (ХХ) являются двумя старшими (9 и 8) битами 10-битного адреса; восьмой бит первого байта — бит направления. “Ноль” в этом бите означает, что ведущий собирается записывать информацию в ведомого, а “единица” — что ведущий будет считывать информацию из ведомого.

Если бит направления равен “нулю”, то второй байт содержит оставшиеся 8 бит 10-битного адреса. Если бит направления равен “единице”, то следующий байт содержит данные, переданные с ведомого ведущему.

Возможны различные комбинации форматов 10-битных посылок:

- Ведущий-передатчик передает информацию ведомому-приемнику (рис 29). Направление пересылки не меняется. Когда за сигалом СТАРТ появляется начало 10-битного адреса, каждый ведомый на шине сравнивает первые семь бит первого байта со своим собственным адресом и удостоверяется, что бит направления равен “нулю”. Допустимо, чтобы более одного устройства обнаружили совпадение и сгенерировали сигнал подтверждения (А1). Все ведомые с совпавшими адресами продолжают сравнивать последующие 8 бит адреса, и только одно устройство обнаруживает совпадение и генерирует подтверждение (А2). Это устройство остается выбранным, пока ведущий не пошлет сигнал СТОП или сигнал повторного СТАРТА с другим адресом. Ведущий-приемник принимает данные от ведомого-передатчика. Направление передачи меняется после второго бита направления (рис. 30). Процедура идентична вышеописанной вплоть до момента второго подтверждения (А2). Далее передается сигнал повторного СТАРТА. Выбранный ведомый помнит, что был адресован ранее. Этот ведомый сравнивает первые семь бит адреса со своим адресом, а также удостоверяется, что бит направления равен “единице”. При совпадении ведомый полагает, что он адресован как передатчик и генерирует подтверждение (А3). Ведомый-передатчик остается адресованным до прихода сигнала СТОП или сигнала повторного СТАРТА с другим адресом. После сигнала повторного СТАРТА все другие устройства также сравнивают первые семь бит со своим адресом и проверяют бит направления. Однако, ни одно из них не адресуется, так как бит направления равен “единице” (для 10-битных устройств), или такого адреса не существует (для 7-битных устройств). Комбинированный формат. Ведущий передает данные ведомому, а потом читает данные с этого же ведомого (рис 31). Один ведущий занимает шину на все время пересылки. Направление пересылки меняется после второго бита направления Комбинированный формат. Ведущий передает данные одному ведомому, а потом передает данные другому ведомому (рис. 32). Один ведущий занимает шину на все время пересылки

Рисунок 29. Ведущий-передатчик адресует ведомого-приемника 10-битным адресом

Рисунок 30. Ведущий-приемник адресует ведомого-передатчика 10-битным адресом

Рисунок 31. Комбинированный формат. Ведущий адресует ведомого 10-битным адресом, потом передает ему данные и принимает из него данные.

Рисунок 32. Комбинированный формат. Ведущий передает данные двум ведомым, оба 10-битные

Комбинированные форматы могут быть использованы, например, для управления последовательной памятью. Во время первого байта данных можно передавать адрес в памяти, который записывается во внутреннюю защелку. После повторения сигнала СТАРТа и адреса ведомого выдаются данные из памяти. Все решения об авто-инкременте или декременте адреса, к которому произошел предыдущий доступ, принимаются конструктором устройства Каждый байт завершается битом подтверждения, обозначенным А или А^ на рисунках I2C-совместимые устройства должны сбрасывать логику шины при получении сигнала СТАРТ или повторный СТАРТ и подготавливаться к приему адреса.

10.1 Адресация операндов Адресация байтов и слов

Методы адресации

Количество методов адресации в различных процессорах может быть от 4 до 16. Рассмотрим несколько типичных методов адресации операндов, используемых сейчас в большинстве микропроцессоров.

Непосредственная адресация (рис. 3.1) предполагает, что операнд (входной) находится в памяти непосредственно за кодом команды. Операнд обычно представляет собой константу, которую надо куда-то переслать, к чему-то прибавить и т. д. Например, команда может состоять в том, чтобы прибавить число 6 к содержимому какого-то внутреннего регистра процессора. Это число 6 будет располагаться в памяти, внутри программы в адресе, следующем за кодом данной команды сложения.

Рис. 3.1. Непосредственная адресация.

Прямая (она же абсолютная) адресация (рис. 3.2) предполагает, что операнд (входной или выходной) находится в памяти по адресу, код которого находится внутри программы сразу же за кодом команды. Например, команда может состоять в том, чтобы очистить (сделать нулевым) содержимое ячейки памяти с адресом 1000000. Код этого адреса 1000000 будет располагаться в памяти, внутри программы в следующем адресе за кодом данной команды очистки.

Рис. 3.2. Прямая адресация.

Регистровая адресация (рис. 3.3) предполагает, что операнд (входной или выходной) находится во внутреннем регистре процессора. Например, команда может состоять в том, чтобы переслать число из нулевого регистра в первый. Номера обоих регистров (0 и 1) будут определяться кодом команды пересылки.

Косвенно-регистровая (она же косвенная) адресация предполагает, что во внутреннем регистре процессора находится не сам операнд, а его адрес в памяти (рис. 3.4). Например, команда может состоять в том, чтобы очистить ячейку памяти с адресом, находящимся в нулевом регистре. Номер этого регистра (0) будет определяться кодом команды очистки.

Рис. 3.3. Регистровая адресация.

Рис. 3.4. Косвенная адресация.

Реже встречаются еще два метода адресации.

Автоинкрементная адресация очень близка к косвенной адресации, но отличается от нее тем, что после выполнения команды содержимое используемого регистра увеличивается на единицу или на два. Этот метод адресации очень удобен, например, при последовательной обработке кодов из массива данных, находящегося в памяти. После обработки какого-то кода адрес в регистре будет указывать уже на следующий код из массива. При использовании косвенной адресации в данном случае пришлось бы увеличивать содержимое этого регистра отдельной командой.

Автодекрементная адресация работает похоже на автоинкрементную, но только содержимое выбранного регистра уменьшается на единицу или на два перед выполнением команды. Эта адресация также удобна при обработке массивов данных. Совместное использование автоинкрементной и автодекрементной адресаций позволяет организовать память стекового типа.

Адресация байтов и слов

Многие процессоры, имеющие разрядность 16 или 32, способны адресовать не только целое слово в памяти (16-разрядное или 32-разрядное), но и отдельные байты. Каждому байту в каждом слове при этом отводится свой адрес.

Так, в случае 16-разрядных процессоров все слова в памяти (16-разрядные) имеют четные адреса. А байты, входящие в эти слова, могут иметь как четные адреса, так и нечетные.

Например, пусть 16-разрядная ячейка памяти имеет адрес 23420, и в ней хранится код 2А5Е (рис. 3.9).

Рис. 3.9. Адресация слов и байтов.

При обращении к целому слову (с содержимым 2А5Е) процессор выставляет адрес 23420. При обращении к младшему байту этой ячейки (с содержимым 5Е) процессор выставляет тот же самый адрес 23420, но использует команду, адресующую байт, а не слово. При обращении к старшему байту этой же ячейки (с содержимым 2А) процессор выставляет адрес 23421 и использует команду, адресующую байт. Следующая по порядку 16-разрядная ячейка памяти с содержимым 487F будет иметь адрес 23422, то есть опять же четный. Ее байты будут иметь адреса 23422 и 23423.

Для различия байтовых и словных циклов обмена на магистрали в шине управления предусматривается специальный сигнал байтового обмена. Для работы с байтами в систему команд процессора вводятся специальные команды или предусматриваются методы байтовой адресации.

10.2 Эквивалентная электрическая схема RS-232

V0- напряжение генератора при разомкнутой схеме; R0- общее сопротивление генератора; C0- общая ёмкость генератора; V1- напряжение между сигнальной линией и общим проводом в месте стыка; CL — общая ёмкость приёмника ; RL — общее сопротивление приёмника; EL — ЭДС приёмника при разомкнутой схеме

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле

🔥 Видео

5.Микропроцессорные системы. Виды и классификация микроконтроллеровСкачать

[1] Микропроцессорные устройства РЗАСкачать

Лекция 4: Типы микропроцессорных системСкачать

03. Основы устройства компьютера. Память и шина. [Универсальный программист]Скачать

АПС Л14. ШиныСкачать

АПС Л19. ШиныСкачать

Чем отличается МИКРОКОНТРОЛЛЕР и МИКРОПРОЦЕССОРСкачать

[11] Дифференциальные защиты №1Скачать

лекция 403 CAN шина- введениеСкачать

Как работает компьютер? Шины адреса, управления и данных. Дешифрация. Взгляд изнутри!Скачать

Микропроцессорные системыСкачать

Микропроцессорные системы Виды и классификация микроконтроллеровСкачать

3.1 ДЗШ 110 кВ УРОВ 110 кВ 1Скачать

Как работает микропроцессорСкачать

Логическая защита шин. Принцип действия и особенностиСкачать

Лекция 4 Программирование микропроцессорных системСкачать

Цифровая электроника ч 1 Структура микропроцессорной системы mPСкачать

АВТОМАТИЧЕСКИЙ ВВОД РЕЗЕРВА - Как собрать схему АВР? Как работает схема АВР? Для чего нужно АВР?Скачать

![[1] Микропроцессорные устройства РЗА](https://i.ytimg.com/vi/oEBEbUijzKs/0.jpg)

![03. Основы устройства компьютера. Память и шина. [Универсальный программист]](https://i.ytimg.com/vi/mjiJutISb6U/0.jpg)

![[11] Дифференциальные защиты №1](https://i.ytimg.com/vi/i8F-w7hsgv8/0.jpg)