Компьютерная Энциклопедия

Компьютерная Энциклопедия- Архитектура ЭВМ

- Компоненты ПК

- Интерфейсы

- Мини блог

- Самое читаемое

- Ввод-вывод

- Контроллер прерываний

- Аппаратные прерывания. Контроллер прерываний

- Технические науки

- Похожие материалы

- Введение

- Аппаратные средства системы прерываний

- Обработка прерываний

- Контроллер прерываний

- Работа контроллера прерывания

- Заключение

- Список литературы

- Завершение формирования электронного архива по направлению «Науки о Земле и энергетика»

- Создание электронного архива по направлению «Науки о Земле и энергетика»

Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

Ввод-вывод

Контроллер прерываний

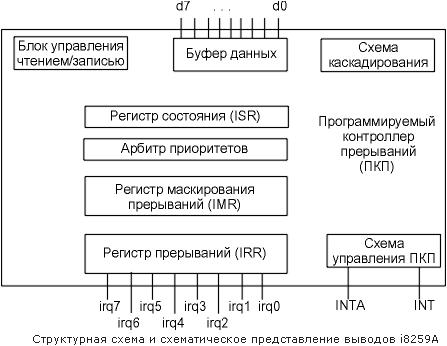

На наш взгляд, знакомство с системой прерываний микропроцессора Intel следует начать с обсуждения организации обработки аппаратных прерываний. Как видно из рис. 15.1, центральное место в схеме обработки аппаратных прерываний занимает программируемый контроллер прерываний (ПКП), выполненный в виде специальной микросхемы i8259А. Как мы уже говорили, эта микросхема может обрабатывать запросы от восьми источников внешних прерываний. Этого явно мало, поэтому в стандартной конфигурации вычислительной системы обычно используют две последовательно соединенные микросхемы i8259A. В результате такого соединения количество возможных источников внешних прерываний возрастает до 15.

Для того чтобы разобраться с обработкой аппаратных прерываний, нам придется проникнуть внутрь микросхемы i8259A. Перечислим функции, выполняемые микросхемой контроллера прерываний:

- фиксирование запросов на обработку прерывания от восьми источников, формирование единого запроса на прерывание и подача его на вход INTR микропроцессора;

- формирование номера вектора прерывания и выдача его на шину данных;

- организация приоритетной обработки прерываний;

- запрещение (маскирование) прерываний с определенными номерами.

На рисунке ниже показано схематическое представление внутренней структуры и физических выводов микросхемы i8259А.

Рассмотрим назначение представляющих для нас интерес выводов i8259А:

- d0. d7 — выводы i8259A, замыкающиеся на системную шину данных. По ним передается номер вектора прерывания и принимается управляющая информация;

- INT — вывод выходного сигнала запроса на прерывание, который подается на вход микропроцессора INTR;

- INTA — вывод для сигнала от микропроцессора, подтверждающего факт принятия им прерывания на обслуживание;

- irq0. irq7 — выводы для входных сигналов запросов на прерывания от внешних устройств.

Важное свойство данного контроллера — возможность его программирования, что позволяет достаточно гибко изменять алгоритмы обработки аппаратных прерываний. Исходя из этого, микросхема i8259А имеет два состояния:

- состояние настройки параметров обслуживания прерываний, во время которого путем посылки в определенном порядке так называемых управляющих слов производится инициализация контроллера;

- состояние работы — это обычное состояние контроллера, в котором производится фиксация запросов на прерывание и формирование управляющей информации для микропроцессора в соответствии с параметрами настройки.

Рассмотрим назначение основных структурных компонентов контроллера прерываний (см. рис. 15.2):

- регистр запросов на прерыванияIRR (Interrupt Request Register) — восьмиразрядный регистр, фиксирующий поступление сигнала на один из входов i8259А — irq0. irq7. Фиксация выражается в установке соответствующего бита в единичное состояние;

- регистр маскирования прерыванийIMR (Interrupt Mask Register) — восьмиразрядный регистр, с помощью которого можно запретить обработку запросов на прерывания, поступающих на соответствующие входы (уровни) irq0. irq_7. Для запрещения (маскирования) определенных уровней прерываний необходимо установить соответствующие биты регистра IMR. Эта операция осуществляется путем программирования порта 21h;

- регистр обслуживаемых прерыванийISR (Interrupt Service Register) — восьмиразрядный регистр, единичное состояние разрядов которого показывает, прерывания каких уровней обрабатываются в данный момент в микропроцессоре;

- арбитр приоритетовPR (Priority Resolver) — функцией данного блока является разрешение конфликта при одновременном поступлении запросов на входы irq0. irq7;

- блок управления — основной функцией данного блока является организация информационного обмена контроллера прерываний и микропроцессора через шину данных. На этот блок замыкаются как выводы d0. d7, так и некоторые другие (см. рис. 15.2).

Рассмотрим возможные прохождение и обработку сигнала прерывания от некоторого внешнего устройства. При этом воспользуемся структурной схемой контроллера прерываний и обозначениями на ней (см. рис. 15.2).

Допустим, на вход irq0 поступает сигнал прерывания, что приводит к установке нулевого бита регистра IRR. Этот регистр связан с регистром маски IMR, состояние битов которого определяет, какие уровни прерываний запрещены (единичные биты) или разрешены к обработке (нулевые биты). Управление данным регистром осуществляется через порт 21h. Таким образом, если бит 0 в IMR равен нулю, то прерывание уровня 0 разрешено. Далее сигнал поступает к арбитру приоритетов. Как мы уже отметили, функция этого блока — разрешение конфликтов при одновременном поступлении запросов на несколько уровней. Обычно самый высокий приоритет у уровня irq_0, и далее приоритет уменьшается с возрастанием номера уровня. Если конфликта нет, то сигнал поступает на схему управления контроллером прерываний, которая формирует сигнал на выводе int. Этот вывод связан со входом микропроцессора INTR. Таким образом, сигнал на входе i8259A достиг микропроцессора. Что происходит далее в микропроцессоре, мы рассмотрим ниже. Сейчас отметим только значимые для данного обсуждения моменты. Итак, при поступлении сигнала на вход INTR в микропроцессоре происходят следующие процессы:

- Анализируется флаг IF. Если вы помните, единичное состояние этого флага говорит о том, что аппаратные прерывания разрешены, нулевое — запрещены.

- Если прерывания запрещены, то запрос на прерывание «повисает» до момента установки IF в единицу.

- Если прерывания разрешены, микропроцессор выполняет следующие действия:

- сбрасывает флаг IF в ноль;

- формирует сигнал подтверждения прерывания на выводе микропроцессора INTA. Этот вывод микропроцессора замкнут на одноименный вывод микросхемы i8259A.

Таким образом, сигнал о прерывании прошел через микропроцессор и вернулся обратно в контроллер прерываний i8259A через вывод INTA. Данный вывод внутри контроллера прерываний замкнут на его схему управления, которая выполняет сразу несколько действий при поступлении этого сигнала:

- Сбрасывает бит в регистре IRR, соответствующий уровню прерывания irq_0.

- Устанавливает в 1 бит 0 регистра ISR, тем самым фиксируя факт обработки прерывания уровня 0 в микропроцессоре.

- Формирует с помощью блока управления номер вектора прерывания, значение которого формируется в буфере данных и далее поступает на выводы i8259A d0. d7. Выводы d0. d7 замкнуты на шину данных, по которой номер вектора поступает в микропроцессор. В микропроцессоре этот номер используется для вызова соответствующей процедуры обработки прерывания.

На данном этапе обработки прерывания, после того как номер прерывания по шине данных поступил в микропроцессор, последнему стало известно все об источнике прерывания. Далее микропроцессор осуществляет процедуру обработки прерывания. Если в это время придет другой сигнал о прерывании того же уровня, то он будет запомнен установкой бита в IRR, и обслуживание этого прерывания будет отложено. Если приходит прерывание другого уровня, то его дальнейшая обработка зависит от приоритета, который оно имеет по отношению к уже обрабатываемым прерываниям. Если приоритет выше, то текущая процедура обработки прерывания останавливается, и вызывается процедура обработки более приоритетного прерывания.

Очень важный момент связан с процессом завершения обработки прерывания. Проблема здесь состоит в следующем. После принятия микропроцессором запроса на обслуживание прерывания в контроллере устанавливается бит в регистре ISR, номер этого бита соответствует уровню прерывания. Установка бита с данным номером блокирует все прерывания уровня, начиная с текущего, и менее приоритетные в блоке-арбитре приоритетов. Если процедура прерывания закончит свою работу, то она сама должна этот бит сбросить, иначе все прерывания этого уровня и менее приоритетные будут игнорироваться. Для осуществления такого сброса необходимо послать код 20h в порт 20h. Есть и другая возможность — установить такой режим работы микросхемы i8259A, когда сброс этого бита будет производиться автоматически. Тонкий момент заключается в том, что происходить такой автоматический сброс будет одновременно с приходом сигнала INTA (то есть извещения о том, что запрос на обработку прерывания принят к обработке микропроцессором). Недостаток автоматического сброса в том, что существует вероятность прихода прерывания того же уровня, который уже обрабатывается в данный момент микропроцессором. В этом случае процедура обработки прерывания должна обладать свойством реентерабельности, то есть допускать повторное обращение к себе до завершения обработки предыдущего обращения. Для того чтобы процедура была реентерабельной, она должна иметь специфическую структуру, в частности, для каждого сеанса обращения к ней создается своя область для хранения переменных и значений регистров, а исполняемая часть процедуры находится в оперативной памяти только в одном экземпляре. Иногда может потребоваться подобный автоматический сброс, но надежнее и проще, конечно, контролировать этот процесс и самостоятельно сбрасывать бит в ISR. Это можно сделать либо в конце работы процедуры, либо в том месте процедуры, начиная с которого можно разрешить рекурсивный вызов данной процедуры, будучи уверенным в том, что она не разрушит никаких данных и работу программы в целом.

Другой не менее интересный момент заключается в том, что микропроцессор при принятии к обработке запроса на прерывание сбросил флаг IF в ноль, тем самым запретив все последующие аппаратные прерывания. Этим обстоятельством программист может пользоваться по своему усмотрению. Вы, конечно, помните, что все запросы на прерывания с приоритетом, равным текущему или меньшим, будут запрещены в любом случае, — это обусловлено логикой работы контроллера i8259A. Поэтому программист должен решить, насколько его замыслам могут помешать запросы на более приоритетные прерывания. Если это некритично, то лучше сразу, в начале процедуры обработки прерывания установить флаг IF в единицу. В большинстве случаев эту операцию нужно делать как можно раньше. Для установки флага IF в единицу в системе команд микропроцессора есть специальная команда, не имеющая операндов:

Читайте также: Самые износостойкие летние шины 2020 2021

sti — разрешить аппаратные прерывания.

Наиболее наглядный пример, показывающий важность своевременной установки IF, связан с отсчетом времени. Если вы не знакомы с тем, как ведется учет времени в компьютере, то уделим этому немного внимания. Как после включения компьютер определяет текущее время суток или как он запоминает информацию о своей конфигурации после выключения? Все дело в том, что компьютер имеет небольшую энергонезависимую память, которая питается от аккумулятора и не зависит от подключения к электросети. Конструктивно эта память выполнена на специальном типе полупроводниковых элементов с так называемой CMOS-структурой (Complementar Metal Oxide Semiconductor — комплиментарная МОП-структура). Особенность таких элементов памяти — в их пониженной по сравнению с обычными микросхемами потребляемой мощности (при этом они являются и более медленными, что в данном случае непринципиально). Аккумулятор кроме CMOS-памяти питает еще и микросхему системных часов, в функции которой входит отсчет текущих даты и времени суток. Таким образом, текущие значения даты и времени постоянно хранятся в CMOS-памяти и поддерживаются в актуальном состоянии даже после выключения компьютера. Кроме того, в CMOS-памяти хранится некоторая другая информация, в частности, о конфигурации компьютера. Во время загрузки компьютера дата и время считываются в область данных BIOS. Дальнейший отсчет времени, после загрузки системы, ведется уже с помощью системного таймера — другой микросхемы на системной плате, в функции которой входит регулярно, примерно 18,2 раза в секунду, генерировать сигнал, который в качестве прерывания подается на уровень irq0 контроллера прерываний i8259A. Во время работы компьютера соответствующая программа BIOS обрабатывает прерывание данного уровня и ведет счет времени. Если терять такты по этому входу, то фактическое время на часах будет отставать, и поэтому в большинстве случаев в обработчиках прерываний есть смысл как можно раньше выдавать команду sti.

Аппаратные прерывания. Контроллер прерываний

Технические науки

- КОНТРОЛЛЕР ПРЕРЫВАНИЙ

- КОНТРОЛЛЕР

- АППАРАТНЫЕ ПРЕРЫВАНИ

- ПРЕРЫВАНИЕ

- ЭВМ

Похожие материалы

Введение

Прерывание означает временное прекращение основного процесса вычислений для выполнения некоторых запланированных или незапланированных действий, вызываемых работой аппаратуры или программы. Т.е. это процесс, временно переключающий микропроцессор на выполнение другой программы с последующим возвратом к прерванной программе. Нажимая клавишу на клавиатуре, мы инициируем немедленный вызов программы, которая распознает клавишу, заносит ее код в буфер клавиатуры, из которого он считывается другой программой. Т.е. на некоторое время микропроцессор прерывает выполнение текущей программы и переключается на программу обработки прерывания, так называемый обработчик прерывания. После того, как обработчик прерывания завершит свою работу, прерванная программа продолжит выполнение с точки, где было приостановлено ее выполнение. Адрес программы-обработчика прерывания вычисляется по таблице векторов прерываний.

Читайте также: Какая компания производит больше всех шин в мире

Механизм прерываний поддерживается на аппаратном уровне. В зависимости от источника, прерывания делятся на:

- аппаратные — возникают как реакция микропроцессора на физический сигнал от некоторого устройства (клавиатура, системные часы, клавиатура, жесткий диск и т.д.), по времени возникновения эти прерывания асинхронны, т.е. происходят в случайные моменты времени;

- программные — вызываются искусственно с помощью соответствующей команды из программы (int), предназначены для выполнения некоторых действий операционной системы, являются синхронными;

- исключения — являются реакцией микропроцессора на нестандартную ситуацию, возникшую внутри микропроцессора во время выполнения некоторой команды программы (деление на ноль, прерывание по флагу TF (трассировка)) [1].

Аппаратные средства системы прерываний

Система прерываний — это совокупность программных и аппаратных средств, реализующих механизм прерываний.

К аппаратным средствам системы прерываний относятся:

- выводы микропроцессора — на них формируются сигналы, извещающие микропроцессор либо о том, что некоторое внешнее устройство «просит уделить ему внимание» (INTR), либо о том, что требуется безотлагательная обработка некоторого события или катастрофическая ошибка (NMI)

- INTR — вывод для входного сигнала запроса на прерывание,

- NMI — вывод для входного сигнала немаскируемого прерывания

- INTA — вывод для выходного сигнала подтверждения получения сигнала прерывания микропроцессором (этот сигнал поступает на одноименный вход микросхемы контроллера 8259А;

- программируемый контроллер прерываний 8259А (предназначен для фиксирования сигналов прерываний от восьми различных внешних устройств; он выполнен в виде микросхемы; обычно используют две последовательно соединенные микросхемы, поэтому кол-во возможных источников внешних прерываний до 15 плюс одно немаскируемое прерываний; именно он формирует номер вектора прерывания и выдает его шину данных);

- внешние устройства (таймер, клавиатура, магнитные диски и т.п.)

Обработка прерываний

Прерывание вызывает ряд событий, которые происходят как в аппаратном, так и в программном обеспечении. На рис. 1 показана типичная последовательность этих событий.

После завершения работы устройства ввода-вывода происходит следующее:

- Устройство посылает процессору сигнал прерывания.

- Перед тем как ответить на прерывание, процессор должен завершить исполнение текущей команды (см. рис. 1).

- Процессор производит проверку наличия прерывания, обнаруживает его и посылает устройству, приславшему это прерывание, уведомляющий сигнал об успешном приеме. Этот сигнал позволяет устройству снять свой сигнал прерывания.

Рисунок 1. Временная диаграмма программы: медленный ввод-вывод

Теперь процессору нужно подготовиться к передаче управления обработчику прерываний. Сначала необходимо сохранить всю важную информацию, чтобы в дальнейшем можно было вернуться к тому месту текущей программы, где она была приостановлена. Минимальная требуемая информация — это слово состояния программы и адрес очередной выполняемой команды, который находится в программном счетчике. Эти данные заносятся в системный управляющий стек.

Рисунок 2. Обработка простого прерывания

Далее в программный счетчик процессора загружается адрес входа программы обработки прерываний, которая отвечает за обработку данного прерывания. В зависимости от архитектуры компьютера и устройства операционной системы может существовать как одна программа для обработки всех прерываний, так может быть и своя программа обработки для каждого устройства и каждого типа прерываний. Если для обработки прерываний имеется несколько программ, то процессор должен определить, к какой из них следует обратиться. Эта информация может содержаться в первоначальном сигнале прерывания; в противном случае для получения необходимой информации процессор должен по очереди опросить все устройства, чтобы определить, какое из них отправило прерывание.

Как только в программный счетчик загружается новое значение, процессор переходит к следующему циклу команды, приступая к ее извлечению из памяти. Так как команда извлекается из ячейки, номер которой задается содержимым программного счетчика, управление переходит к программе обработки прерываний. Исполнение этой программы влечет за собой следующие операции.

Содержимое программного счетчика и слово состояния прерываемой программы уже хранятся в системном стеке. Однако это еще не вся информация, имеющая отношение к состоянию исполняемой программы. Например, нужно сохранить содержимое регистров процессора, так как эти регистры могут понадобиться обработчику прерываний. Поэтому необходимо сохранить всю информацию о состоянии программы. Обычно обработчик прерываний начинает свою работу с записи в стек содержимого всех регистров. Другая информация, которая должна быть сохранена, обсуждается в главе 3, «Описание процессов и управление ими». На рис. показан простой пример, в котором программа пользователя прерывается после выполнения команды из ячейки N. Содержимое всех регистров, а также адрес следующей команды (N+1), в сумме составляющие М слов, заносятся в стек. Указатель стека при этом обновляется, указывая на новую вершину стека. Обновляется и программный счетчик, указывая на начало программы обработки прерывания.

Теперь обработчик прерываний может начать свою работу. В процесс обработки прерывания входит проверка информации состояния, имеющая отношение к операциям ввода-вывода или другим событиям, вызвавшим прерывание. Сюда может также входить пересылка устройствам ввода-вывода дополнительных инструкций или уведомляющих сообщений.

После завершения обработки прерываний из стека извлекаются сохраненные ранее значения, которые вновь заносятся в регистры, возобновляя таким образом то состояние, в котором они пребывали до прерывания.

Последний этап — восстановление из стека слова состояния программы и содержимого программного счетчика. В результате следующей будет выполняться команда прерванной программы.

Из-за того, что прерывание не является подпрограммой, вызываемой из программы, для полного восстановления важно сохранить всю информацию состояния прерываемой программы. Однако прерывание может произойти в любой момент и в любом месте программы пользователя. Это событие непредсказуемо [2].

Контроллер прерываний

Контроллер прерываний предназначен для обработки и арбитража поступающих запросов на обслуживание к центральному процессору от переферийных устройств. По аналогии функции контроллера прерываний можно сравнить с секретарём какого–нибудь начальника. Секретарь должен решить, кого из посетителей допустить к боссу в первую очередь, а кого и потом, исходя из приоритетов, отдаваемых боссом и статуса самого посетителя. Так и в компьютерной системе, возможна такая ситуация, когда несколько переферийных устройств послали сигнал прерывания или запрос на прерывание. В компьютерной литературе этот сигнал обозначается IRQ (Interrupt Request).

Читайте также: Шина вильямса при дисплазии

Как уже выше говорилось, прерывания имеют определённый приоритет, который позволяет контроллеры прерываний отдавать предпочтение в данный момент времени одному устройству, а не другому. В современном компьютере существует до 16 внешних и периферийных устройств, генерирующие прерывания. Вот эти устройства:

–IRQ 0, системный таймер; –IRQ 1, клавиатура; –IRQ 2, исползуется для запросов устройств, подключенных каскадом; –IRQ 8, часы реального времени; –IRQ 9, зарезервировано; –IRQ 10, зарезервировано; –IRQ 11, зарезервировано; –IRQ 12, ps/2–мышь; –IRQ 13, сопроцессор; –IRQ 14, контроллер «жёсткого» диска; –IRQ 15, зарезервировано; –IRQ 3, порты COM2,COM4; –IRQ 4, порты COM1,COM3; –IRQ 5, порт LPT2; –IRQ 6, контроллер дисковода; –IRQ 7, порт LPT1,принтер.

Здесь сигналы приведены в порядке убывания приоритетов. Можно заметить, что после IRQ 2, следует IRQ 8. Дело в том, что в своё время контроллер прерываний состоял из двух микросхем, одна была подключена к другой. Вот эта вторая микросхема и подключается к линии IRQ 2, образуя каскад. Она обслуживает линии IRQ8–IRQ 15. А затем следуют линии первой микросхемы [3].

Работа контроллера прерывания

Работа контроллеов прерываний рассматривается на основе микросхем фирмы Intel 8259A, которые применялись в теперь уже очень старых компьютерах с процессорами до 386 серии. В этих компьютерах обычно было 2 микросхемы 8259A, подключенных каскадно, то–есть одна к другой. Одна из микросхем, подключенная по линии запроса на прерывание непосредственно к процессору является ведущей или мастером. Остальные,подключаются к ведущей через аналогичные выводы, называются ведомыми.

Рисунок 3. Схема подключения контроллеров прерываний и их взаимодействие с центральным процессором

На рисунке 3 изображена схема подключения контроллеров прерываний и их взаимодействие с центральным процессором. Сигналы на прерывание от переферийных устройств или ведомых контроллеров поступают на входы IR0–IR7 ведущего контроллера. Внутренняя логика ведущего контроллера обрабатывает поступившие запросы с точки зрения приоритета. Если приоритет запроса устройства достаточен, то на выходе INT контроллера вырабатывается сигнал, поступающий на вход INTR процессора. В противном случае, запрос блокируется.

Если процессор разрешает прерывания, то после завершения выполнения текущей команды, он вырабатывает по линии INTA последовательность сигналов, которая переводит ведомый контроллер в состояние невосприимчивости к поступающим новым запросам на прерывание, а кроме того, на линию данных выводится информация из внутренних регистров контроллера по которой процессор распознаёт тип прерывания.

Разрешение на прерывание процессор передаёт контроллеру прерываний через контроллер шины. Сигнал RD предназначен для того, чтобы контроллер прерываний поместил на шину данных содержимое внутренних регистров. По сигналу WR контроллер прерываний, наоборот, принимает данные с одноимённой шины и записывает их во внутренние регистры. Соответственно, это влияет на режим работы контроллера прерываний.

Вход CS подключается к шине адреса и по этому сигналу происходит идентификация конкретного контролллера прерываний. Вход A0 указывает на порт контроллера прерываний в пространстве ввода–вывода.

Входы IR0–IR7 предназначены для приёма запросов на прерывание от переферийных устройств и ведомых контроллеров.

Выходы CAS0–CAS2 предназначены для идентификации конкретного ведомого контроллера [4].

В статье рассмотрены аппаратные прерывания и устройство, функции, работу контроллера прерываний. Данный контроллер прерываний появился ещё в первых PC–совместимых компьютерах. С тех пор, и процессоры, и сам компьютер во многом изменились, хотя некоторые моменты остались. Поэтому, для того, чтобы было понятней и была рассмотрена организация контроллера прерываний 8295A.

На приведенной выше схеме показаны сигналов приходящие не только на ведомый и ведущий контроллеры прерываний, но и на остальные ведомые. Однако на вашем компьютере или ноутбуке на самом деле 2 контроллера прерываний, как выше указывалось: ведущий и ведомый. Но можно создавать свои компьютерные системы, используя таким образом до 64 ведомых контроллеров прерываний.

В современных компьютерах уже давно функции контроллера прерываний выполняют не микросхемы 8259A, а южный мост. Однако, для всех программ и устройств всё остаётся по–прежнему. Более того, контроллер прерываний можно программировать, и обращаться к внутренним регистрам и портам необходимо точно также, как и к контроллеру 8259A [5].

Заключение

В данной работе были рассмотрены прерывания, а именно аппаратные средства обработки прерываний и принцип обработки прерываний. Также рассмотрены контроллеры прерываний и принцип их работы.

Прерывание означает временное прекращение основного процесса вычислений для выполнения некоторых запланированных или незапланированных действий, вызываемых работой аппаратуры или программы. Механизм прерываний поддерживается на аппаратном уровне. Аппаратные прерывания возникают как реакция микропроцессора на физический сигнал от некоторого устройства (клавиатура, системные часы, клавиатура, жесткий диск и т.д.), по времени возникновения эти прерывания асинхронны, т.е. происходят в случайные моменты времени.

Контроллер прерываний предназначен для обработки и арбитража поступающих запросов на обслуживание к центральному процессору от переферийных устройств. Прерывания имеют определённый приоритет, который позволяет контроллеру прерываний отдавать предпочтение в данный момент времени одному устройству, а не другому. В современном компьютере существует до 16 внешних и переферийных устройств, генерирующие прерывания.

Список литературы

- Лекция. Прерывания. Эл. Ресурс. http://hromatron.narod.ru/_lekcii/prerivania_lekcia_g2013.htm

- Системные прерывания | Аппаратное прерывание | Обработка прерываний http://life-prog.ru/view_os.php?id=16

- Контроллер прерываний. Эл. Ресурс http://sdelaycomputersam.ru/Controller_irq.php,

- Прерывания. Контроллер прерываний. Устройство, функции, работа. Эл. Ресурс http://sdelaycomputersam.ru/Controller_irq.php

- Структура и инициализация контроллера прерываний Intel 8259A Эл.ресурс https://dev64.wordpress.com/2012/05/30/8259-programming/

Завершение формирования электронного архива по направлению «Науки о Земле и энергетика»

Создание электронного архива по направлению «Науки о Земле и энергетика»

Электронное периодическое издание зарегистрировано в Федеральной службе по надзору в сфере связи, информационных технологий и массовых коммуникаций (Роскомнадзор), свидетельство о регистрации СМИ — ЭЛ № ФС77-41429 от 23.07.2010 г.

Соучредители СМИ: Долганов А.А., Майоров Е.В.

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле