Введение

PCI (Peripheral Component Interconnect bus) — шина для подсоединения периферийных устройств. Стала массово применяться для Pentium-систем, но используется и с 486 процессорами. Частота шины от 20 до 33 МГц, теоретически максимальная скорость 132/264 Мбайт/с для 32/64 бит. В современных материнских платах частота на шине PCI задается как 1/2 входной частоты процессора, т.е при частоте 66 MHz на PCI будет 33 MHz, при 75 MHz — 37.5 MHz.

Имеет версии с питанием 5V, 3.3V и универсальную (с переключением линий +VI/O c 5V на 3,3V). Ключами являются пропущенные ряды контактов 12, 13 и 50, 51. Для слота с питанием 5V ключ расположен на месте контактов 50, 51, для 3,3 В — 12, 13, а для универсального — два ключа: 12, 13 и 50,51. 32-битный слот заканчивается контактами А62/В62, 64-битный — А94/В94.

Слот PCI самодостаточен для подключения любого контроллера (VLB не работала без ISA), на системной плате может сосуществовать с любой из других шин ввода-вывода.

Шина PCI — первая шина в архитектуре IBM PC, которая не привязана к этой архитектуре. Она является процессорно-независимой и применяется, например, в компьютерах Macintosh.

В отличие от остальных шин, компоненты расположены на левой поверхности плат PCI-адаптеров. По этой причине крайний PCI-слот обычно разделяет использование посадочного места с соседним ISA-слотом (Shared slot).

Процессор через так называемые мосты (PCI Bridge) может быть подключен к нескольким каналам PCI, обеспечивая возможность одновременной передачи данных между независимыми каналами PCI (возможно только в спецификации 2.1).

Автоконфигурирование устройств (выбор запросов прерывания, каналов DMA) поддерживается средствами BIOS материнской платы по образу и подобию стандарта Plug & Play. В настоящее время действует спецификация PCI 2.1.

Стандарт PCI определяет для каждого слота конфигурационное пространство размером до 256 восьмибитных регистров, не приписанных ни к пространству памяти, ни к пространству ввода-вывода. Доступ к ним осуществляется по специальным циклам шины Configuration Read и Configuration Write, вырабатываемым контроллером при обращении процессора к регистрам контроллера шины PCI, расположенным в его пространстве ввода-вывода.

На PCI определены два основных вида устройств — инициатор (по ГОСТ — задатчик), т.е. устройство, получившее от арбитра шины разрешение на захват ее и устройство назначения, цель (target) с которым инициатор выполняет цикл обмена данными.

Сигналы шины PCI

Знак — (минус) перед названием сигнала означает, что активный уровень этого сигнала логический ноль, обозначение означает группу сигналов с номерами от 0 до XX.

AD — мультиплексированная шина адреса/данных. Адрес передается по сигналу — FRAME, в последующих тактах передаются данные.

-C/ BE — команда/разрешение обращения к байтам. Команда, определяющая тип очередного цикла шины (чтение-запись памяти, ввода/вывода или чтение/запись конфигурации, подтверждение прерывания и другие) задается четырехбитным кодом в фазе адреса по сигналу — FRAME.

-FRAME — индикатор фазы адреса (иначе — передача данных).

-DEVSEL — выбор инициатором устройства назначения.

-IRDY — готовность инициатора к обмену данными.

-TRDY — готовность устройства назначения к обмену данными.

-STOP — запрос устройства назначения к инициатору на останов текущей транзакции.

-LOCK — используется для установки, обслуживания и освобождения захвата ресурса на PCI.

-REQ — запрос от PCI-устройства на захват шины (для слотов 3:0).

-GNT — разрешение мастеру на использование шины.

PAR — общий бит четности для линий AD и C/BE .

-ParityER — сигнал об ошибке по четности (от устройства, ее обнаружившего).

-RST — сброс всех устройств.

IDSEL — выбор устройства назначения в циклах считывания и записи конфигурации.

-SERR — системная ошибка, активизируется любым устройством PCI и вызывает немаскируемое прерывание процессора (NMI).

Читайте также: Шины белшина или кама что лучше

-REQ64 — запрос на 64-битный обмен.

-ASK64 — подтверждение 64-битного обмена.

-INTR A,B,C,D — линии запросов прерывания, направляются на доступные линии IRQ BIOS компьютера. Запрос по низкому уровню допускает разделяемое использование линий прерывания.

Clock — сигнал синхронизации на тактовой частоте шины.

Test Clock, -TSTRES, TestDO, TestDI — сигналы для тестирования адаптеров по интерфейсу JTAG (на системной плате обычно не задействованы).

TSTMSLCT — перевод в режим тестирования.

Видео:ОСОБЕННОСТИ КОНСТРУКЦИИ ШИНЫ! КОНСТРУКЦИЯ РАДИАЛЬНОЙ ШИНЫ!Скачать

Общие положения и введение в логику работы шины I 2 C

- Двунаправленный обмен по двум линиям

- Высокая скорость обмена — до 100 кбит и выше

- Возможность адресации до 128 устройств

- Простота программной реализации «Master»-абонента

- Временная независимость процесса передачи

Данное введение является формальным описанием шины I 2 C и предназначено только для достаточно подробного ознакомления с целью самостоятельной реализации частных алгоритмов связи. Для получения более полной информации обращайтесь к соответствующей литературе фирмы Philips.

Разработанная фирмой Philips шина I 2 C («Inter-Integrated Circuit»), — это двунаправленная асинхронная шина с последовательной передачей данных и возможностью адресации до 128 устройств. Физически шина I 2 C содержит две сигнальные линии, одна из которых (SCL) предназначена для передачи тактового сигнала, вторая (SDA) для обмена данными. Для управления линиями применяются выходные каскады с открытым коллектором, поэтому линии шины должны быть подтянуты к источнику питания +5 В через резисторы сопротивлением 1. 10 кОм, в зависимости от физической длины линий и скорости передачи данных. Длина соединительных линий в стандартном режиме может достигать 2-х метров, скорость передачи — до 100 кбит/с. Суммарная емкость линий должна быть не больше 400 пФ, входная емкость на каждую ИС должна быть в пределах 5. 10 пФ.

Все абоненты шины делятся на два класса — «Master» и «Slave». Устройство «Master» генерирует тактовый сигнал (SCL) и, как следствие, является ведущим. Оно может самостоятельно выходить на шину и адресовать любое «Slave» — устройство с целью передачи или приема информации. Все «Slave»-устройства «слушают» шину на предмет обнпружения собственного адреса и, распознав его, выполняют предписываемую операцию. Кроме того, возможен так называемый «Multi Master» — режим когда на шине установлено несколько «Master»-абонентов, которые либо совместно разделяют общие «Slave»-устройства, либо попеременно являются то «Master»-устройствами, когда сами инициируют обмен информацией, то «Slave», когда находятся в режиме ожидания обращения от другого «Master»-устройства. Режим «Multi Master» требует арбитража и распознавания конфликтов. Естественно, он сложнее в реализации (имеется ввиду программная реализаци) и, как следствие, реже используется в реальных изделиях.

В начальный момент времени — в режиме ожидания — обе линии SCL и SDA находятся в состоянии логической единицы (транзистор выходного каскада с ОК закрыт). В режиме передачи (рис. 1) бит данных SDA стробируется положительным импульсом SCL. Смена информации на линии SDA производится при нулевом состоянии линии SCL. «Slave»-устройство может «придерживать» линию SCL в нулевом состоянии, например, на время обработки очередного принятого байта, при этом «Master»-устройство обязано дождаться освобождения линии SCL, прежде чем продолжить передачу информации.

Рис. 1. Диаграмма процесса передачи данных по шине I 2 C

Для синхронизации пакетов шины I 2 C различают два условия — «Start» и «Stop», ограничивающие начало и конец информационного пакета (рис. 2). Для кодирования этих условий используется изменение состояния линии SCL, что недопустимо при передаче данных. «Start»-условие образуется при отрицательном перепаде линии SDA, когда линия SCL находится в единичном состоянии, и наоборот, ‘Stop»-условие образуется при положительном перепаде линии SDA при единичном состоянии линии SCL.

Рис. 2. Диаграмма «Старт»/»Стоп» условия шины I 2 C

Рис. 3. Диаграмма подтверждения приема байта по шине I 2 C

Передача данных начинается по первому положительному импульсу на линии SCL (рис. 3), которым стробируется старший бит первого информационного байта. Каждый информационный байт (8 битов) содержит 9 тактовых периодов линии SCL. В девятом такте устройство-получатель выдает подтверждение (ACK) — отрицательный импульс, свидетельствующий о «взаимопонимании» передатчика и получателя. Сразу отметим, что любой абонент шины, как «Master», так и «Slave» может в разные моменты времени быть как передатчиком, так и получателем и в соответствии с режимом обязан либо принимать, либо выдавать сигнал ACK, отсутствие которого интерпритируется как ошибка.

Читайте также: Шина дали что из себя представляет

Рис. 4. Временная диаграмма работы шины I 2 C

Временная диаграмма сигналов SCL и SDA шины I 2 C приведена на рис. 4. Здесь S обозначает «Start»-условие, Р — «Stop»-условие. Значения временных характеристик приведены в табл. 1.

Таблица 1. Значения временных характеристик шины I 2 C

| Параметр | Обозначение | Мин. | Макс. | Един. |

| Частота сигнала SCL | fSCL | 0 | 100 | кГц |

| Свободная шина | tBUF | 4.7 | — | мкс |

| Фиксация «Start»-условия | tHD;STA | 4.0 | — | мкс |

| Длительность «LOW» полупериода SCL | tLOW | 4.7 | — | мкс |

| Длительность «HIGH» полупериода SCL | tHIGH | 4.0 | — | мкс |

| Готовность повторного «Start»-условия | tSU;STA | 4.7 | — | мкс |

| Удержание данных | tHD;DAT | 0 | — | мкс |

| Готовность данных | tsu;dat | 250 | — | нс |

| Фронт сигналов SCL и SDA | tr | — | 1000 | нс |

| Спад сигналов SCL и SDA | tf | — | 300 | нс |

| Готовность «STOP»-условия | tSU;STO | 4.0 | — | мкс |

Чтобы начать операцию обмена устройство «Master» выдает на шину «Start»-условие, за которым следует байт с адресом «Slave»-устройства (рис. 5), состоящий из семибитового адреса устройства (занимает биты 1. 7) и однобитового флага операции — «R/W» (бит 0) определяющего направление обмена, причем 0 означает передачу от «Master» к «Slave» (рис. 5 а), а 1 — чтение из «Slave» (рис. 5б). Все биты передаются по шине I 2 C в порядке старший-младший, то есть первым передается 7-ой бит, последним 0-ой. За адресои могут следовать один или более информационных байтов (в направлении, определенном флагом R/W), биты которых стробируются сигналом SCL из «Master»-устройства.

При совершении операции чтения «Master»-абонент должен сопровождать прочитанный байт сигналом ACK, если необходимо прочитать следующий байт, и не выдавать сигнала ACK, если собирается закончить чтение пакета (рис. 5б).

Допускается многократное возобновление «Slave»-адреса в одном цикле передачи, то есть передача повторного «Start»-условия без предварительного «Stop»-условия. Такой принцип широко применяется в управлении I 2 C абонентами, когда выдача нового «Start»-условия служит для синхронизации начала нового пакета данных, сопровождаемого, например, новым управляющим словом, уточняющим адресацию пакета. Логическая реализация протоколов на шине I 2 C не нормируется документами фирмы Philips, содержащими формальные описания шины, и может быть произвольной для каждой конкретной ИС.

Видео:Проверка датчика давления шины TMPSСкачать

конспект / 13-Структура шины и временные диаграммы её работы

ШД (шина данных) – обеспечивает передачу данных между блоками МПС.

ША (шина адреса) – служит для указания ячейки памяти или устройства, к которым мы хотим обратиться.

ШУ (шина управления) – обеспечивает процесс управления записью/чтением, вводом/выводом.

ЦП, Память, УВВ – чаще всего реализуются как стандартные блоки. Для доступа к памяти используют операции чтения и записи, для УВВ – операции ввода и вывода.

Передача память/интерфейс может происходить без участия ЦП. В данном случае используется котроллер прямого доступа к памяти (DMA), который изолирует ЦП от шин.

Указывает на выбранную ячейку памяти или интерфейса –(направлена от процессора)

Разрядность определяет максимальное количество адресуемой памяти (216 = 64К) или количество устройств ввода/вывода.

Шина управления, как правило, однонаправлена, но для сообщения с медленными устройствами используется двунаправленная шина управления. Такие устройства используют шину для сообщения ЦП о своей готовности к действию.

При изолированном вводе/выводе используются изолированные друг от друга области памяти и регистров портов. В таком случае практически невозможно переписать другую область вместо необходимой. Такой способ обращения к портам используется в устройствах Гарвардской архитектуры.

При вводе/выводе с отображением на память имеется возможность при обращении к памяти переписать случайно регистры портов ввода/вывода и наоборот.

MEMRD – операция чтения из памяти

MEMWR – операция записи в память

IORD – операция вывода из порта

IOWR – операция ввода в порт

Сигналы для управления данными операциями подаются по соответствующим линиям ШУ.

Выходной буферный элемент

Сигналы чтения/записи подаются на оба буферных элемента, чтобы исключить возможность короткого замыкания. Сигнал чтения открывает выходной буферный элемент (входной буфер при этом закрыт), из которого прочитанные данные поступают на шину данных, а сигнал записи – открывает входной буферный элемент (выходной буфер закрыт), данные в который поступают с шины данных для записи в память.

Если бы были открыты оба буферных элемента (т.е. сигналы чтения/записи не подавались бы на их входы), данные приходили бы на входной буферный элемент и сразу же выходили бы через выходной буфер.

Временная диаграмма работы шины (циклы чтения)

Адрес на ША поступает с задержкой, т.к. необходимо некоторое время для срабатывания всех линий шины.

Для выполнения операции чтения каждому МП необходимо некоторое определенное количество тактов (в данном случае требуется четыре такта).

При подключении периферийных устройств необходимо иметь в виду, что оно может иметь до сотни внутренних регистров (в зависимости от сложности ПУ).

По фронту CLK (1-ый такт), с задержкой, на ША устанавливается адрес ячейки.

По фронту 2-го такта в активное состояние (низкий уровень) переходит сигнал чтения (MEMRD) и удерживается некоторое время. MEMWR не изменяется.

На ШД по спаду 2-го такта открываются выходные буферные элементы.

По спаду 4-го такта осуществляется чтение данных.

Подключение портов ввода/вывода

Дешифратор адреса выдает стробирующий сигнал для устройств ввода/вывода и на ШД поступают нужные данные. В зависимости от сложности периферийного устройства, количество регистров изменяется.

Сигналы управления с сигналом готовности

READY – сигнал готовности, реализующий обратную связь медленных устройств памяти и ввода/вывода с ЦП. Он может формироваться как внутренне (в устройстве), так и внешне.

Временная диаграмма работы шины (циклы чтения с сигналом готовности)

С 1 до 2 – устройство не готово. Данные на всех шинах сохраняются, вставляются дополнительные такты Tw до тех пор, пока устройство не сообщит о своей готовности. После 2 – устройство готово.

Сигналы управления с совмещенным сигналом MEM/IO

Введением информационного сигнала MEM/IO обеспечивается сокращение стробирующих сигналов. Этот сигнал информирует ЦП о том, будет использоваться память или устройства ввода/вывода. Он имеет три состояния (третье состояние лежит вне пределов нуля и единицы).

Сигналы управления с совмещенными сигналами MEM/IO и RD/WR

RD/WR – информационный сигнал с тремя состояниями, определяет выбор операции чтения или операции записи.

Временная диаграмма работы шины с совмещенными шинами адреса и данных

ALE – стробирующий сигнал. Высокий уровень данного сигнала говорит о том, что на совмещенной шине адреса и данных (ШД/ША low) выставлен адрес, который необходимо зафиксировать в буфере.

Пример подключения внешней памяти через совмещенную шину адреса/данных

ОЗУ (RAM) подключается через дешифратор.

001 – W, 010 – R, 011 – W, 100 – R …

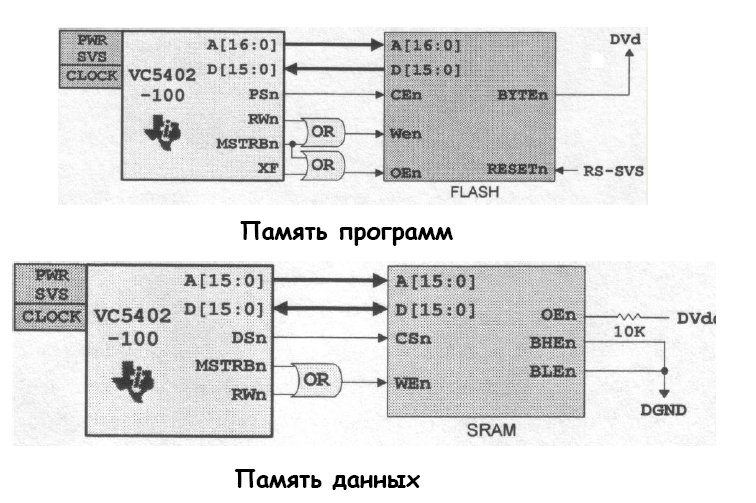

Пример подключения внешней памяти данных и памяти программ

На рисунке представлен пример Гарвардской архитектуры с разделением пространств памяти программ и данных.

Помимо Гарвардской МПС могут строиться согласно Принстонской архитектуры, где пространства программ и данных не разделяются.

Совмещенная шина адреса и данных

2

Тут вы можете оставить комментарий к выбранному абзацу или сообщить об ошибке.

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле

🔥 Видео

Левые и правые шины. Асимметричные и направленные. Разница?Скачать

На какую ось ставить новые шины | Правила перестановки шинСкачать

Ремонт боковых порезов шин.Скачать

Как понять, когда протектор износился и шины пора менятьСкачать

Самостоятельный ремонт бескамерной шины жгутомСкачать

Что означает МАРКИРОВКА НА ШИНАХ / Значение всех цифр и букв на резинеСкачать

Как устанавливать зимние асимметричные шины. Левые и правые шины.Скачать

Грибки, жгуты или заплаты? Что использовать при ремонте легковых шин?Скачать

Колёса и шиныСкачать

ТИХИЕ ШИНЫ ЭТОГО НЕ ЗНАЮТ БОЛЬШИНСТВО АВТОМОБИЛИСТОВСкачать

Последовательные логические устройства. Триггеры (RS, D, JK, T). Принцип работы, типовые схемы.Скачать

ВСЕ МАРКИРОВКИ ШИН. БЕЗ ИСКЛЮЧЕНИЙСкачать

Конструкция шиныСкачать

Старая шина, но ещё высокий протектор. Что делать?Скачать

Как починить боковой порез? Пробило шинуСкачать

Клиент даже не думал что можно почистить шины колёс!Скачать

Заземление или зануление? Что выбрать? Как это работает? #энерголикбезСкачать

Лекция "Интерфейсы (часть I). RS-232/422/485. SPI"Скачать