Компьютерная Энциклопедия

Компьютерная ЭнциклопедияАрхитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

Видео:Системная шина процессораСкачать

Системные платы

Видео:03. Основы устройства компьютера. Память и шина. [Универсальный программист]Скачать

![03. Основы устройства компьютера. Память и шина. [Универсальный программист]](https://i.ytimg.com/vi/mjiJutISb6U/0.jpg)

Шина процессора

Видео:КАК работает ПРОЦЕССОР? ОБЪЯСНЯЕМСкачать

Общие сведения о шине процессора

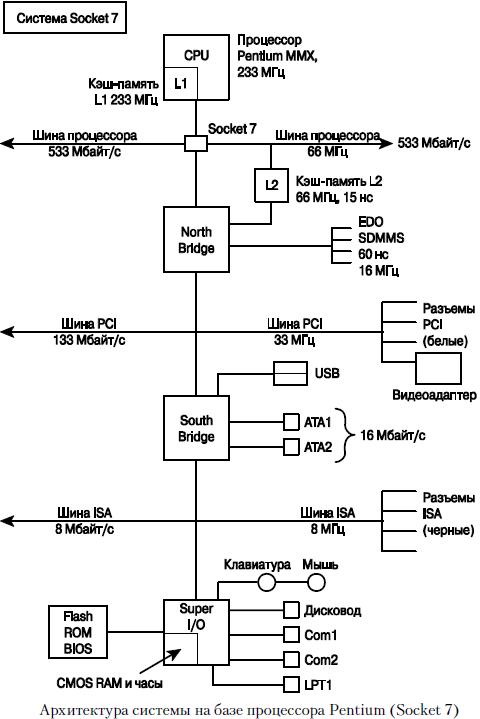

Шина процессора — соединяет процессор с северным мостом или контроллером памяти MCH. Она работает на частотах 66–200 МГц и используется для передачи данных между процессором и основной системной шиной или между процессором и внешней кэш-памятью в системах на базе процессоров пятого поколения. Схема взаимодействия шин в типичном компьютере на базе процессора Pentium (Socket 7) показано на рисунке.

На этом рисунке четко видна трехуровневая архитектура, в которой на самом верхнем уровне иерархии находится шина процессора, далее следует шина PCI и за ней шина ISA. Большинство компонентов системы подключается к одной из этих трех шин.

В системах, созданных на основе процессоров Socket 7, внешняя кэш-память второго уровня установлена на системной плате и соединена с шиной процессора, которая работает на частоте системной платы (обычно от 66 до 100 МГц). Таким образом, при появлении процессоров Socket 7 с более высокой тактовой частотой рабочая частота кэш-памяти осталась равной сравнительно низкой частоте системной платы. Например, в наиболее быстродействующих системах Intel Socket 7 частота процессора равна 233 МГц, а частота шины процессора при множителе 3,5х достигает только 66 МГц. Следовательно, кэш-память второго уровня также работает на частоте 66 МГц. Возьмем, например, систему Socket 7, использующую процессоры AMD K6-2 550, работающие на частоте 550 МГц: при множителе 5,5х ч астота шины процессора равна 100 МГц. Следовательно, в этих системах частота кэш-памяти второго уровня достигает только 100 МГц.

Проблема медленной кэш-памяти второго уровня была решена в процессорах класса P6, таких как Pentium Pro, Pentium II, Celeron, Pentium III, а также AMD Athlon и Duron. В этих процессорах использовались разъемы Socket 8, Slot 1, Slot 2, Slot A, Socket A или Socket 370. Кроме того, кэш-память второго уровня была перенесена с системной платы непосредственно в процессор и соединена с ним с помощью встроенной шины. Теперь эта шина стала называться шиной переднего плана (Front-Side Bus — FSB), однако я, согласно устоявшейся традиции, продолжаю называть ее шиной процессора.

Включение кэш-памяти второго уровня в процессор позволило значительно повысить ее скорость. В современных процессорах кэш-память расположена непосредственно в кристалле процессора, т.е. работает с частотой процессора. В более ранних версиях кэш-память второгоуровня находилась в отдельной микросхеме, интегрированной в корпус процессора, и работала с частотой, равной 1/2, 2/5 или 1/3 частоты процессора. Однако даже в этом случае скорость интегрированной кэш-памяти была значительно выше, чем скорость внешнего кэша, ограниченного частотой системной платы Socket 7.

В системах Slot 1 кэш-память второго уровня была встроена в процессор, но работала только на его половинной частоте. Повышение частоты шины процессора с 66 до 100 МГц привело к увеличению пропускной способности до 800 Мбайт/с. Следует отметить, что в большинство систем была включена поддержка AGP. Частота стандартного интерфейса AGP равна 66 МГц (т.е. вдвое больше скорости PCI), но большинство систем поддерживают порт AGP 2x, быстродействие которого вдвое выше стандартного AGP, что приводит к увеличению пропускной способности до 533 Мбайт/с. Кроме того, в этих системах обычно использовались модули памяти PC100 SDRAM DIMM, скорость передачи данных которых равна 800 Мбайт/с.

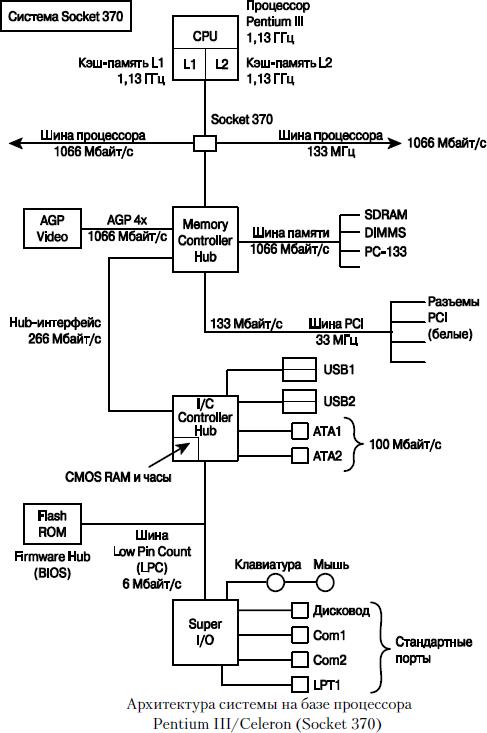

В системах Pentium III и Celeron разъем Slot 1 уступил место гнезду Socket 370. Это было связано главным образом с тем, что более современные процессоры включают в себя встроенную кэш-память второго уровня (работающую на полной частоте ядра), а значит, исчезла потребность в дорогом корпусе, содержащем несколько микросхем. Скорость шины процессора увеличилась до 133 МГц, что повлекло за собой повышение пропускной способности до 1066 Мбайт/с. В современных системах используется уже AGP 4x со скоростью передачи данных 1066 Мбайт/с.

Шина процессора на основе hub-архитектуры

Обратите внимание на hub-архитектуру Intel, используемую вместо традиционной архитектуры “северный/южный мост”. В этой конструкции основное соединение между компонентами набора микросхем перенесено в выделенный hub-интерфейс со скоростью передачи данных 266 Мбайт/с (вдвое больше, чем у шины PCI), что позволило устройствам PCI использовать полную, без учета южного моста, пропускную способность шины PCI. Кроме того, микросхема Flash ROM BIOS, называемая теперь Firmware Hub, соединяется с системой через шину LPC. Как уже отмечалось, в архитектуре “северный/южный мост” для этого использовалась микросхема Super I/O. В большинстве систем для соединения микросхемы Super I/O вместо шины ISA теперь используется шина LPC. При этом hub-архитектура позволяет отказаться от использования Super I/O. Порты, поддерживаемые микросхемой Super I/O, называются традиционными (legacy), поэтому конструкция без Super I/O получила название нетрадиционной (legacy-free) системы. В такой системе устройства, использующие стандартные порты, должны быть подсоединены к компьютеру с помощью шины USB. В этих системах обычно используются два контроллера и до четырех общих портов (дополнительные порты могут быть подключены к узлам USB).

Читайте также: Как считать маркировку шин

В системах, созданных на базе процессоров AMD, применена конструкция Socket A, в которой используются более быстрые по сравнению с Socket 370 процессор и шины памяти, но все еще сохраняется конструкция “северный/южный мост”. Обратите внимание на быстродействующую шину процессора, частота которой достигает 333 МГц (пропускная способность — 2664 Мбайт/с), а также на используемые модули памяти DDR SDRAM DIMM, которые поддерживают такую же пропускную способность (т.е. 2664 Мбайт/с). Также следует заметить, что большинство южных мостов включает в себя функции, свойственные микросхемам Super I/O. Эти микросхемы получили название Super South Bridge (суперъюжный мост).

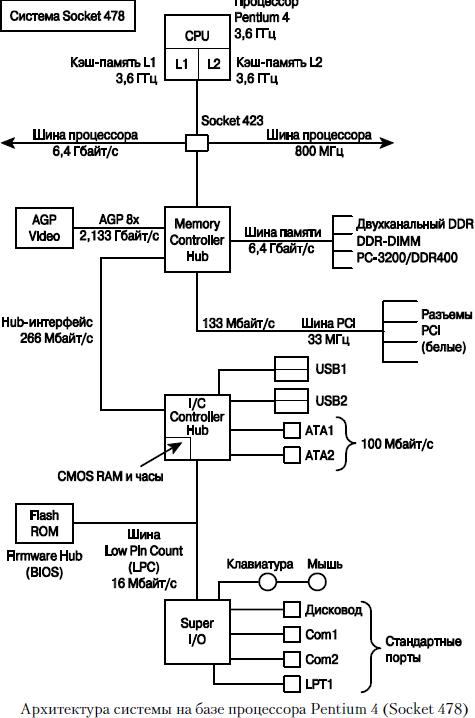

Система Pentium 4 (Socket 423 или Socket 478), созданная на основе hub-архитектуры, показана на рисунке ниже. Особенностью этой конструкции является шина процессора с тактовой частотой 400/533/800 МГц и пропускной способностью соответственно 3200/4266/6400 Мбайт/с. Сегодня это самая быстродействующая шина. Также обратите внимание на двухканальные модули PC3200 (DDR400), пропускная способность которых (3200 Мбайт/с) соответствует пропускной способности шины процессора, что позволяет максимально повысить производительность системы. В более производительных системах, включающих в себя шину с пропускной способностью 6400 Мбайт/с, используются двухканальные модули DDR400 с тактовой частотой 400 МГц, благодаря чему общая пропускная способность шины памяти достигает 6400 Мбайт/с. Процессоры с частотой шины 533 МГц могут использовать парные модули памяти (PC2100/DDR266 или PC2700/DDR333) в двухканальном режиме для достижения пропускной способности шины памяти 4266 Мбайт/с. Соответствие пропускной способности шины памяти рабочим параметрам шины процессора является условием оптимальной работы.

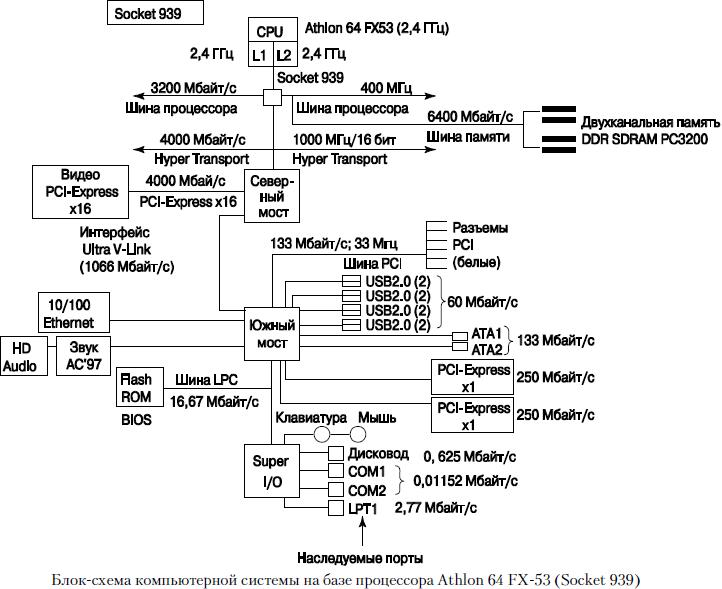

Процессор Athlon 64, независимо от типа гнезда (Socket 754, Socket 939 или Socket 940), использует высокоскоростную архитектуру HyperTransport для взаимодействия с северным мостом или микросхемой AGP Graphics Tunnel. Первые наборы микросхем для процессоров Athlon 64 использовали версию шины HyperTransport с параметрами 16 бит/800 МГц, однако последующие модели, предназначенные для поддержки процессоров Athlon 64 и Athlon 64 FX в исполнении Socket 939, используют более быструю версию шины HyperTransport с параметрами 16 бит/1 ГГц.

Наиболее заметным отличием архитектуры Athlon 64 от всех остальных архитектур ПК является размещение контроллера памяти не в микросхеме северного моста (или микросхеме MCH/GMCH), а в самом процессоре. Процессоры Athlon 64/FX/Opteron оснащены встроенным контроллером памяти. Благодаря этому исключаются многие “узкие места”, связанные с внешним контроллером памяти, что положительно сказывается на общем быстродействии системы. Главный недостаток этого подхода состоит в том, что для добавления поддержки новых технологий, например памяти DDR2, придется изменять архитектуру процессора.

Поскольку шина процессора должна обмениваться информацией с процессором с максимально возможной скоростью, в компьютере она функционирует намного быстрее любой другой шины. Сигнальные линии (линии электрической связи), представляющие шину, предназначены для передачи данных, адресов и сигналов управления между отдельными компонентами компьютера. Большинство процессоров Pentium имеют 64-разрядную шину данных, поэтому за один цикл по шине процессора передается 64 бит данных (8 байт).

Читайте также: Какое давление в шинах 185 75r16c

Тактовая частота , используемая для передачи данных по шине процессора, соответствует его внешней частоте. Это следует учитывать, поскольку в большинстве процессоров внутренняя тактовая частота, определяющая скорость работы внутренних блоков, может превышать внешнюю. Например, процессор AMD Athlon 64 3800+ работает с внутренней тактовой частотой 2,4 ГГц, однако внешняя частота составляет всего 400 МГц, в то время как процессор Pentium 4 с внутренней частотой 3,4 ГГц имеет внешнюю частоту, равную 800 МГц. В новых системах реальная частота процессора зависит от множителя шины процессора (2x, 2,5x, 3x и выше). Шина FSB, подключенная к процессору, по каждой линии данных может передавать один бит данных в течение одного или двух периодов тактовой частоты. Таким образом, в компьютерах с современными процессорами за один такт передается 64 бит.

Пропускная способность шины процессора

Для определения скорости передачи данных по шине процессора необходимо умножить разрядность шины данных (64 бит, или 8 байт, для Celeron/Pentium III/4 или Athlon/Duron/ Athlon XP/Athlon 64) на тактовую частоту шины (она равна базовой (внешней) тактовой частоте процессора).

Например, при использовании процессора Pentium 4 с тактовой частотой 3,6 ГГц, установленного на системной плате, частота которой равна 800 МГц, максимальная мгновенная скорость передачи данных будет достигать примерно 6400 Мбайт/с. Этот результат можно получить, используя следующую формулу:

800 МГц × 8 байт (64 бит) = 6400 Мбайт/с.

Для более медленной системы Pentium 4:

533,33 МГц × 8 байт (64 бит) = 4266 Мбайт/с;

400 МГц × 8 байт (64 бит) = 3200 Мбайт/с.

Для системы Athlon XP (Socket A) получится следующее:

400 МГц × 8 байт (64 бит) = 3200 Мбайт/с;

333 МГц × 8 байт (64 бит) = 2667 Мбайт/с;

266,66 МГц × 8 байт (64 бит) = 2133 Мбайт/с.

Для системы Pentium III (Socket 370):

133,33 МГц × 8 байт (64 бит) = 1066 Мбайт/с;

100 МГц × 8 байт (64 бит) = 800 Мбайт/с.

Максимальную скорость передачи данных называют также пропускной способностью шины (bandwidth) процессора.

Видео:Шины ввода-выводаСкачать

Взаимодействие памяти и процессора

Процессор взаимодействует с оперативной памятью не напрямую, а через специальный контроллер, подключенный к системной шине процессора приблизительно так же, как и остальные контроллеры периферийных устройств. Причем механизм обращения к портам ввода/вывода и к ячейкам оперативной памяти с точки зрения процессора практически идентичен. Процессор сначала выставляет на адресную шину требуемый адрес, а в следующем такте уточняет тип запроса: происходит ли обращение к памяти, портам ввода/вывода или подтверждение прерывания. В некотором смысле оперативную память можно рассматривать как совокупность регистров ввода/вывода, каждый из которых хранит некоторое значение.

Обработка запросов процессора ложится на набор системной логики (так же называемый чипсетом), среди прочего включающий в себя и контроллер памяти. Контроллер памяти полностью «прозрачен» для программиста, однако знание его архитектурных особенностей существенно облегчает оптимизацию обмена с памятью.

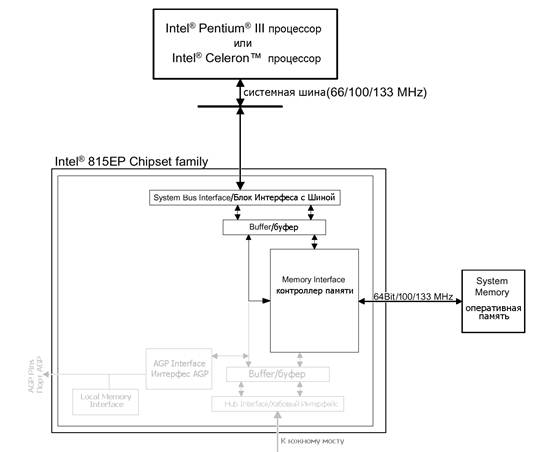

Рассмотрим механизм взаимодействия памяти и процессора на примере чипсета Intel 815EP (рис. 2.9). Когда процессору требуется получить содержимое ячейки оперативной памяти, он, дождавшись освобождения шины, через механизм арбитража захватывает шину в свое владение (что занимает один такт) и в следующем такте передает адрес искомой ячейки. Еще один такт уходит на уточнение типа запроса, назначение уникального идентификатора транзакции, сообщение длины запроса и маскировку байтов шины. Подробнее об этом можно прочитать в спецификациях на шины Р6 и EV6, здесь же достаточно отметить, что эта фаза запроса осуществляется за три такта системной шины.

Устройство северного моста чипсета Intel 815EP, содержащего (среди прочего) контроллер памяти

Независимо от размера читаемой ячейки (байт, слово, двойное слово) длина запроса всегда равна размеру линейки Ь2-кэша (подробнее об устройстве кэша мы поговорим в одноименной главе), что составляет 32 байт для процессоров K6/P-II/P-III, 64 байт — для AMD Athlon и 128 байт — для Р-4. Такое решение значительно увеличивает производительность памяти при последовательном чтении ячеек и практически не уменьшает ее при чтении ячеек вразброс, что и неудивительно, т. к. латентность чипсета в несколько раз превышает реальное время передачи данных, и им можно пренебречь.

Читайте также: Снеговик своими руками из шин автомобиля

Контроллер шины (BIU — Bus Interface Init), «вживленный» в северный мост чипсета, получив запрос от процессора, в зависимости от ситуации либо передает его соответствующему агенту (в нашем случае — контроллеру памяти), либо ставит запрос в очередь, если агент в этот момент чем-то занят. Потребность в очереди объясняется тем, что процессор может посылать очередной запрос, не дожидаясь завершения обработки предыдущего, а раз так, то запросы приходится где-то хранить.

Но, так или иначе, наш запрос оказывается у контроллера памяти (МСТ — Memory Controller). В течение одного такта он декодирует полученный адрес в физический номер строки/столбца ячейки и передает его модулю памяти по сценарию, описанному в разд. «Устройство и принципы функционирования оперативной памяти» этой главы.

В зависимости от архитектуры контроллера памяти он работает с памятью либо только на частоте системной шины (синхронный контроллер),либо поддерживает память любой другой частоты (асинхронный контроллер). Синхронные контролеры ограничивают пользователей ПК в выборе модулей памяти, но, с другой стороны, асинхронные контроллеры менее производительны. Почему? Во-первых, в силу несоответствия частот, читаемые данные не могут быть непосредственно переданы на контроллер шины, и их приходится сначала складывать в промежуточный буфер, откуда шинный контроллер сможет их извлекать с нужной ему скоростью. (Аналогичная ситуация наблюдается и с записью.) Во-вторых, если частота системной шины и частота памяти не соотносятся как целые числа, то перед началом обмена приходится дожидаться завершения текущего тактового импульса. Таких задержек (в просторечии пенальти) возникает две:

- при передаче микросхеме памяти адреса требуемой ячейки

- при передаче считанных данных шинному контроллеру.

Все это значительно увеличивает латентность подсистемы памяти — т. е. промежутка времени с момента посылки запроса до получения данных. Таким образом, асинхронный контроллер, работающий с памятью SDRAM PC-133 на системной шине в 100 МГц, проигрывает своему синхронному собрату, работающему на той же шине с памятью SDRAM PC-100.

Контроллер шины, получив от контроллера памяти уведомление о том, что запрошенные данные готовы, дожидается освобождения шины, и передает их процессору в пакетном режиме. В зависимости от типа шины за один такт может передаваться от одной до четырех порций данных. Так, в процессорах Кб, Р-И и Р-Ш осуществляется одна передача за такт, в процессоре Athlon — две, а в процессоре Р-4 — четыре.

С этого момента данные поступают в кэш и становятся доступными процессору.

Контроллер системной шины, отвечающий за обработку запросов и перемещение данных между процессором и чипсетом, состоит из следующих функциональных компонентов: трансфера данных (Processor Source Synch Clock Transceiver), планировщика запросов (Command Queue — CQ), контроллера очередей запросов (Control System Queue — CSQ) и агента транзакций (transaction combiner agent — XCA). Остальные компоненты контроллера шины, присутствующие на рис. 2.11, необходимы для поддержки зондовой отладки, которая к обсуждаемой теме не относится, а потому здесь не рассматривается.

Трансфер данных — в каком-то высшем смысле представляет собой «голый» контроллер шины, понимающий шинный протокол и берущий на себя все заботы по общению с процессором. Полученные от процессора запросы передаются планировщику запросов, откуда они отправляются соответствующим агентам по мере их освобождения.

Ответы агентов сохраняются в трех раздельных очередях: очереди чтения (SysDC Read Queue — SRQ), очереди записи памяти (Memory Write Queue — MWQ) и очереди записи шины PCI(PCI/A-PCI Write Queue — AWQ). Обратите внимание: в данном случае речь идет о записи/чтении в процессор, а не наоборот! Таким образом, очередь записи памяти хранит данные, передаваемые из памяти в процессор, но не записываемые процессором в память!

- Свежие записи

- Нужно ли менять пружины при замене амортизаторов

- Скрипят амортизаторы на машине что делать

- Из чего состоит стойка амортизатора передняя

- Чем стянуть пружину амортизатора без стяжек

- Для чего нужны амортизаторы в автомобиле

💥 Видео

Как разогнать процессор и память? Гоним по шине и множителю.Скачать

Принцип работы процессора на уровне ядраСкачать

05. Основы устройства компьютера. Регистры и команды процессора. [Универсальный программист]Скачать

Как работает компьютер? Шины адреса, управления и данных. Дешифрация. Взгляд изнутри!Скачать

169 секунд и ты знаешь как работает процессорСкачать

АПС Л14. ШиныСкачать

Частота процессора, множитель и системная шинаСкачать

Как работает процессор: частоты, шины и т.д.Скачать

Шина компьютера, оперативная память, процессор и мостыСкачать

Частота процессора или частота системной шины?Скачать

Посмотрите на ваши шины..Скачать

Как работает процессор, просто о сложном ✌Скачать

Разгон кольцевой шины и кэша L3 процессораСкачать

Частота процессора, множитель и системная шинаСкачать

Безвоздушные шины...Скачать

Тюнинг ГБЦ! Валы, Шестерни, Пружины и Портинг!Скачать

![05. Основы устройства компьютера. Регистры и команды процессора. [Универсальный программист]](https://i.ytimg.com/vi/ieT3JXSJYpA/0.jpg)